一种低压鲁棒性增强型电容偏置浮动反相放大器的制作方法

本发明属于模拟电路,尤其涉及一种低压鲁棒性增强型电容偏置浮动反相放大器。

背景技术:

1、在物联网应用下,许多传感器和生物医学设备由能量采集器供电,而能量采集器的输出电压通常在几百mv以内,因此非常希望放大器能够在低电压的情况下操作。

2、然而在sub-1v(低于1v)供电下,模拟电路设计难度也大大增大。放大器是最基本的模拟电路模块,其应用非常广泛。但是在sub-1v供电情况下,复杂的放大器设计无法实现,需要使用简单的结构实现放大器功能。

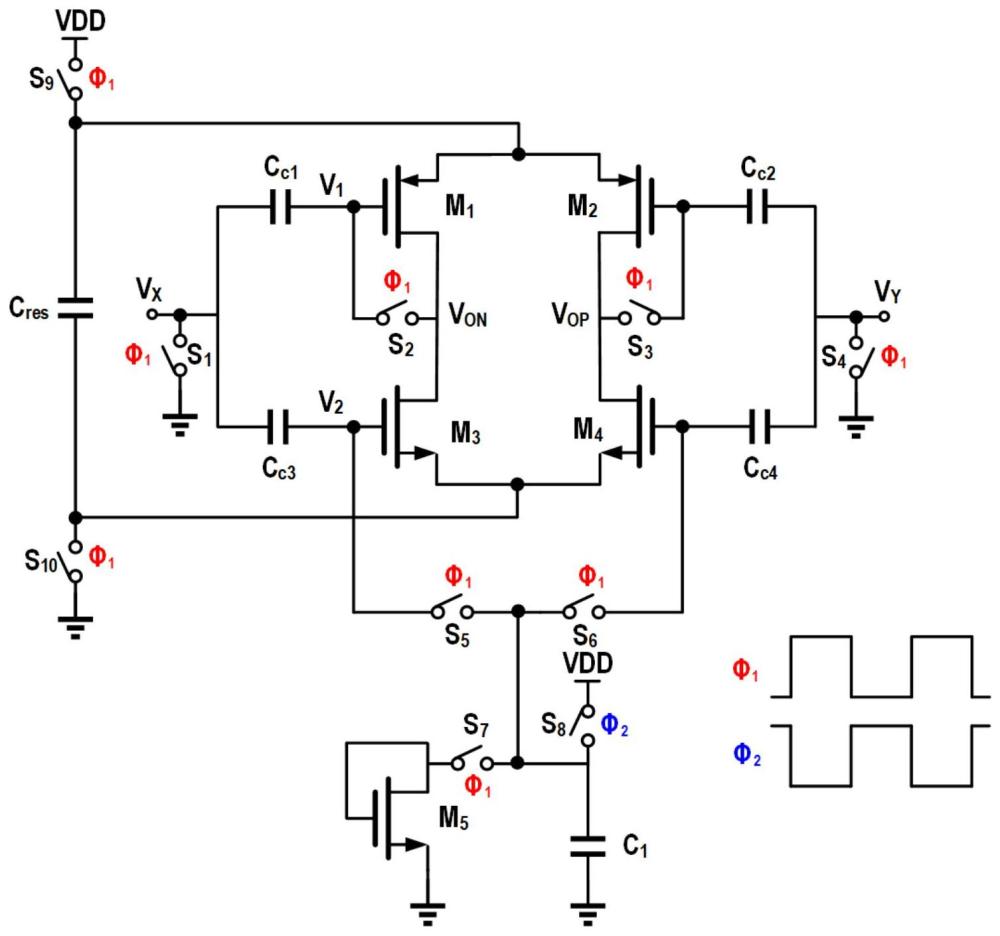

3、浮动反相放大器(floating inverter amplifier,fia)作为一款结构简单的动态放大器,拥有众多优点:不需要静态功耗,因此能量效率高;带宽和功耗随工作频率可调;输出共模稳定,不需要额外的共模反馈电路等。但fia无法在sub-1v的供电下工作,在专利zl202310955162.x中,申请人提出了一种简洁的低压浮动反相放大器(low voltage fia,lvfia),如图1所示。lvfia可以实现sub-1v的供电,但是在相位φ1时,nmos和pmos电流各自独立定义,不可避免存在电流适配的问题,因此鲁棒性仍然不足。且该方案需要多个控制时序时钟,方案复杂。

技术实现思路

1、发明目的:本发明所要解决的技术问题是针对现有技术的不足,提供一种低压鲁棒性增强型电容偏置浮动反相放大器。

2、为了解决上述技术问题,本发明公开了一种低压鲁棒性增强型电容偏置浮动反相放大器(capacitively bias fia,cbfia),包括电容偏置电路、电容耦合反相放大电路和储能电容电路,所述电容偏置电路,用于为电容耦合反相放大电路提供偏置电压;所述储能电容电路,用于为电容耦合反相放大电路供电;所述电容耦合反相放大电路,用于对差分输入信号进行放大,获得差分输出信号。

3、进一步地,所述电容耦合反相放大电路包括第一输入晶体管电路和第二输入晶体管电路,所述第一输入晶体管电路的一输入端和第二输入晶体管电路的一输入端连接,连接处接收差分输入信号vx以及通过第一开关s1接地;所述第一输入晶体管电路的另一输入端和第二输入晶体管电路的另一输入端连接,连接处接收差分输入信号vy以及通过第四开关s4接地;第一输入晶体管电路的两输出端分别与第二输入晶体管电路的两输出端连接,连接处形成差分输出节点von和vop。

4、进一步地,所述第一输入晶体管电路包括第一对输入晶体管以及与所述第一对输入晶体管的栅极分别连接的自动归零电容,所述第一对输入晶体管的源级相连,连接处与储能电容电路的一端连接;所述储能电容电路的一端还通过第十开关s10接地;所述第一对输入晶体管的栅极分别通过第五开关s5和第六开关s6相连,连接处与电容偏置电路连接。

5、进一步地,所述电容偏置电路包括第一电容偏置电路,所述第一电容偏置电路用于为第一对输入晶体管提供偏置电压,包括第一电容c1、晶体管m5、第七开关s7和第八开关s8,所述晶体管m5的源级接地,栅极和漏极相连,连接处与第七开关s7的一端连接;第一电容c1的一端接地,另一端与第七开关s7的另一端连接,连接处与第五开关s5和第六开关s6的连接处相连;第一电容c1的另一端还通过第八开关s8连接电源电压。由于引入额外的晶体管m5进行二极管连接,因此可以使cbfia电路工作在更低的供电电压下。

6、进一步地,所述第二输入晶体管电路包括第二对输入晶体管以及与所述第二对输入晶体管的栅极分别连接的自动归零电容,所述第二对输入晶体管的源级相连,连接处与储能电容电路的另一端连接;所述储能电容电路的另一端还通过第九开关s9连接电源电压;所述第二对输入晶体管的栅极分别通过第二开关s2与差分输出节点von连接,以及通过第三开关s3与差分输出节点vop连接。

7、采用电容偏置和自动归零的方式确定第一对输入晶体管和第二对输入晶体管偏置,保证流过第二对输入晶体管和第一对输入晶体管的电流相同,提高了输入晶体管偏置电流的鲁棒性。

8、进一步地,第一对输入晶体管的漏极分别与第二对输入晶体管的漏极连接,连接处形成差分输出节点von和vop。

9、进一步地,第一输入晶体管电路还包括第三对输入晶体管,第二输入晶体管电路还包括第四对输入晶体管,所述第一对输入晶体管的漏极分别与第三对输入晶体管的源级连接,第三对输入晶体管的漏极分别与第四对输入晶体管的漏极连接,连接处形成差分输出节点von和vop;第四对输入晶体管的源级分别与第二对输入晶体管的漏极连接;第三对输入晶体管的栅极均连接偏置电压v4,第四对输入晶体管的栅极均连接偏置电压v3。拓展为共源共栅结构能够提高直流增益。

10、进一步地,所述第一开关s1、第二开关s2、第三开关s3、第四开关s4、第五开关s5、第六开关s6、第七开关s7、第九开关s9和第十开关s10由自动归零相位φ1控制,第八开关s8由放大相位φ2控制,所述自动归零相位φ1和放大相位φ2互为反相相位;

11、在自动归零相位φ1,第一开关s1、第二开关s2、第三开关s3、第四开关s4、第五开关s5、第六开关s6、第七开关s7、第九开关s9和第十开关s10闭合,第八开关s8断开,储能电容电路充电;在上个相位预充电的第一电容c1和与所述第一对输入晶体管的栅极分别连接的自动归零电容进行电荷共享并通过晶体管m5进行放电;

12、记第一对输入晶体管栅极的偏置电压为v2,第二对输入晶体管栅极的偏置电压为v1,通过控制自动归零相位φ1的高电平时间能够改变偏置电压v2的值,从而确定第一对输入晶体管的偏置电流,与此同时,第二对输入晶体管进行自动归零,将偏置电压v1以及失调电压和闪烁噪声一起存储在与所述第二对输入晶体管的栅极分别连接的自动归零电容上。由于第一对输入晶体管和第二对输入晶体管的偏置均通过控制自动归零相位φ1的占空比自由确定,因此该cbfia的输出摆幅不受mos管阈值电压vth的限制。

13、进一步地,在放大相位φ2,第一开关s1、第二开关s2、第三开关s3、第四开关s4、第五开关s5、第六开关s6、第七开关s7、第九开关s9和第十开关s10断开,第八开关s8闭合,第一电容c1充电;由储能电容电路为电容耦合反相放大电路供电,v1和v2为自动归零相位φ1确定的偏置电压值,差分输入信号通过自动归零电容耦合到第一对输入晶体管和第二对输入晶体管,第一对输入晶体管和第二对输入晶体管对信号进行放大,获得差分输出信号。

14、进一步地,所述电容偏置电路还包括第二电容偏置电路和第三电容偏置电路,所述第二电容偏置电路用于提供偏置电压v3,第三电容偏置电路用于提供偏置电压v4;

15、所述第二电容偏置电路包括第二电容c2、晶体管m10、第十一开关s11和第十二开关s12,所述晶体管m10的源级接地,栅极和漏极相连,连接处形成偏置电压v3,并与第十一开关s11的一端连接;第二电容c2的一端接地,另一端与第十一开关s11的另一端连接;第二电容c2的另一端还通过第十二开关s12连接接地电压;

16、所述第三电容偏置电路包括第三电容c3、晶体管m11、第十三开关s13和第十四开关s14,所述晶体管m11的源级接地,栅极和漏极相连,连接处形成偏置电压v4,并与第十三开关s13的一端连接;第三电容c3的一端接地,另一端与第十三开关s13的另一端连接;第三电容c3的另一端还通过第十四开关s14连接电源电压;

17、第十一开关s11和第十三开关s13由自动归零相位φ1控制,第十二开关s12和第十四开关s14由放大相位φ2控制。

18、共源共栅结构的偏置同样由电容偏置方式生成,在提高增益的同时保持了cbfia随供电电压变化的鲁棒性。

19、有益效果:

20、1)本技术提供的一种低压鲁棒性增强型电容偏置浮动反相放大器由于引入额外的晶体管m5进行二极管连接,因此可以使电路工作在更低的供电电压下,轻松实现sub-1v的供电。

21、2)采用电容偏置和自动归零的方式确定第一对输入晶体管和第二对输入晶体管偏置,保证流过第二对输入晶体管和第一对输入晶体管的电流相同,提高了输入晶体管偏置电流的鲁棒性。

22、3)由于巧妙结合了自动归零技术降低失调电压和闪烁噪声,因此提高了所述浮动反相放大器的噪声性能。

23、4)由于第一对输入晶体管和第二对输入晶体管的偏置均通过控制自动归零相位φ1的占空比自由确定,因此该浮动反相放大器的输出摆幅不受mos管阈值电压vth的限制。

24、5)控制逻辑简洁,只需要一组反相时钟即可。

- 还没有人留言评论。精彩留言会获得点赞!