可变延时时钟电路及单比特ADC芯片、电子设备

本技术属于电子电路,尤其涉及一种可变延时时钟电路及单比特adc芯片、电子设备。

背景技术:

1、在时间交织技术的模数采样中,时钟偏差是不同通道间采样时钟的相位差不均匀导致,主要来源于输入缓冲器的失配、信号走线不等、采样不一致等,在输出频谱上表现为特定位置的杂散。时间偏移是由于每个子模数转换器中的采样边缘不对准引起的,这会产生杂散并降低模数转换器的信噪比,特别是在高频应用中。

2、故亟待提供一种可变延时时钟电路以提高相邻时钟信号的相位差的均匀性。

技术实现思路

1、本技术的目的在于提供一种可变延时时钟电路及单比特adc芯片、电子设备,旨在解决相关的可变延时时钟电路输出的相邻时钟信号的相位差均匀性差的问题。

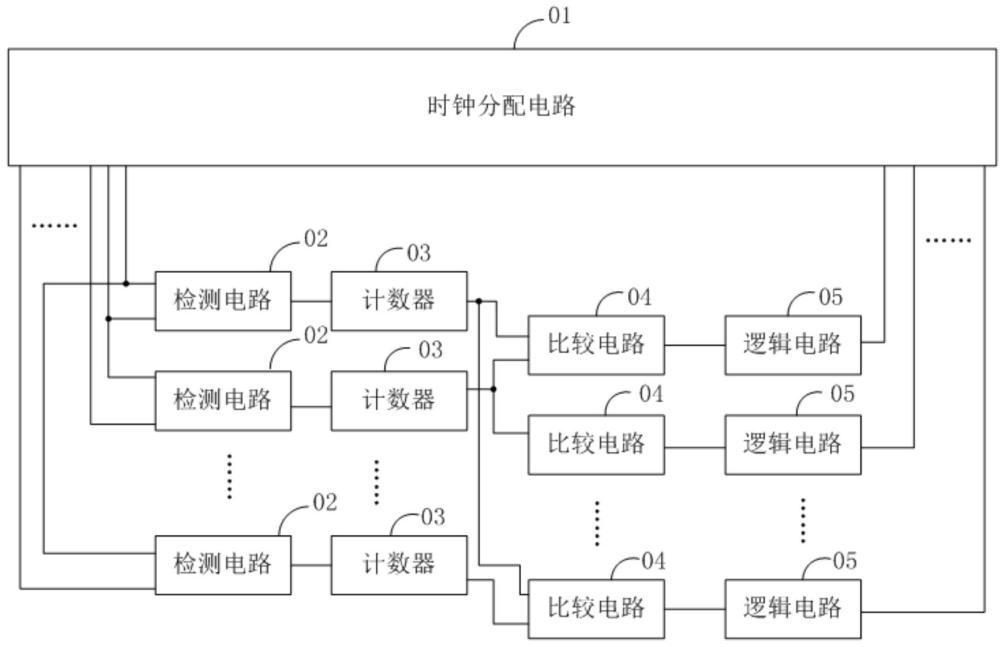

2、本技术实施例提供了一种可变延时时钟电路,包括时钟分配电路、n个检测电路、n个计数器、n个比较电路、n个逻辑电路;

3、第i个所述逻辑电路配置为输出携带预设的第i个控制字的控制信号;

4、所述时钟分配电路,与n个所述逻辑电路连接,配置为根据携带n个预设的所述控制字的控制信号输出n个时钟信号;

5、第i个所述检测电路,与所述时钟分配电路连接,配置为在第i个所述时钟信号和第i+1个所述时钟信号具有不同的电压极性的情况下,输出触发信号;第i个所述计数器,与第i个所述检测电路连接,配置为对第i个所述检测电路输出的所述触发信号进行计数;

6、第i个所述比较电路,与第i个计数器和第i+1个计数器连接,配置为在n个计数器中任意一个计数器的计数值达到预设值时,对第i个计数器的计数值和第i+1个计数器的计数值进行比较,并根据比较结果输出第i个比较信号;

7、第i个所述逻辑电路,还与所述第i个所述比较电路连接,还配置为根据第i个所述比较信号更新第i个所述控制字,并根据更新后的第i个所述控制字输出第i个控制信号;

8、所述时钟分配电路还配置为根据携带n个更新后的所述控制字的控制信号输出n个所述时钟信号;

9、n为大于2的正整数,i为小于等于n的正整数。

10、在其中一个实施例中,第i个所述比较电路具体配置为在n个计数器中任意一个计数器的计数值达到预设值时,在第i个计数器的计数值大于等于第i+1个计数器的计数值的情况下,输出第一电平的第i个比较信号,在第i个计数器的计数值小于第i+1个计数器的计数值的情况下,输出第二电平的第i个比较信号;所述第一电平和所述第二电平极性相反。

11、在其中一个实施例中,第i个所述逻辑电路,具体配置为根据第二电平的第i个所述比较信号将所述控制字与1的差作为新的第i个所述控制字,根据第一电平的第i个所述比较信号将所述控制字与1的和作为新的第i个所述控制字,并根据更新后的第i个所述控制字输出第i个控制信号。

12、在其中一个实施例中,所述时钟分配电路包括:

13、依次串联的n个第一缓冲器和与n个第一缓冲器的输出端一一并联连接的n个电容组件。

14、在其中一个实施例中,所述控制字具有k位;所述电容组件包括2k个可变电容;k为正整数;

15、所述时钟分配电路还包括n个解码开关电路;

16、第i个所述解码开关电路,与第i个所述逻辑电路和第i个电容组件连接,配置为根据第i个控制信号得到第i个所述控制字,将第i个所述控制字转换为十进制,以得到有效电容个数,并将第i个所述电容组件中的有效电容个数的可变电容接第一电源,并输出第i个所述时钟信号。

17、在其中一个实施例中,还包括:

18、自振荡电路,与n个所述检测电路连接,配置为基于基准电压输出基准时钟信号;

19、第i个所述检测电路,具体配置为在第i个所述时钟信号和第i+1个所述时钟信号具有不同的电压极性的情况下,根据所述基准时钟信号输出所述触发信号。

20、在其中一个实施例中,所述自振荡电路包括第一与非门、第二与非门、第三与非门、第四与非门、第五与非门、第六与非门、第七与非门以及第二缓冲器;

21、所述第一与非门的第一输入端与所述第七与非门的输出端和所述第二缓冲器的输入端连接,所述第一与非门的输出端与所述第二与非门的第一输入端连接,所述第二与非门的输出端与所述第三与非门的第一输入端连接,所述第三与非门的输出端与所述第四与非门的第一输入端连接,所述第五与非门的输出端与所述第六与非门的第一输入端连接,所述第六与非门的输出端与所述第七与非门的第一输入端连接,所述第一与非门的第二输入端、所述第二与非门的第二输入端、所述第三与非门的第二输入端、所述第四与非门的第二输入端、所述第五与非门的第二输入端、所述第六与非门的第二输入端以及所述第七与非门的第二输入端共同作为所述自振荡电路的基准电压输入端,以接入所述基准电压;所述第二缓冲器的输出端作为所述自振荡电路的基准时钟信号输出端,与所述检测电路连接,以输出所述基准时钟信号。

22、在其中一个实施例中,第i个所述检测电路包括第一比较器、第二比较器、异或门、第一场效应管以及第二场效应管;

23、所述第一场效应管的漏极以及所述第二场效应管的漏极共同作为第i个所述检测电路的基准时钟信号输入端,与所述自振荡电路连接,以接入所述基准时钟信号;

24、所述第一场效应管的栅极作为第i个所述检测电路的第i个时钟信号输入端,与所述时钟分配电路连接,以接入所述第i个时钟信号;

25、所述第二场效应管的栅极作为第i+1个所述检测电路的第i+1个时钟信号输入端,与所述时钟分配电路连接,以接入所述第i+1个时钟信号;

26、所述第一场效应管的源极与所述第一比较器的正相输入端连接,所述第二场效应管的源极与所述第二比较器的正相输入端连接,所述第一比较器的输出端与所述异或门的第一输入端连接,和所述第二比较器的输出端与所述异或门的第一输入端连接;

27、所述异或门的输出端作为第i个所述检测电路的触发信号输出端,与所述第i个所述计数器连接,以输出所述触发信号。

28、本发明实施例还一种单比特adc芯片,所述单比特adc芯片包括上述的可变延时时钟电路。

29、本发明实施例还一种电子设备,所述电子设备包括上述的可变延时时钟电路。

30、本发明实施例与现有技术相比存在的有益效果是:由于第i个检测电路在第i个时钟信号和第i+1个时钟信号具有不同的电压极性的情况下,输出触发信号;且第i个计数器对第i个检测电路输出的触发信号进行计数;故第i个时钟信号和第i+1个时钟信号的相位差与触发概率(第i个计数器的计数值)呈正相关;再通过第i个比较电路在n个计数器中任意一个计数器的计数值达到预设值时,对第i个计数器的计数值和第i+1个计数器的计数值进行比较,并根据比较结果输出第i个比较信号;第i个逻辑电路根据第i个比较信号更新第i个控制字,并根据更新后的第i个控制字输出第i个控制信号;时钟分配电路还配置为根据携带n个更新后的控制字的控制信号输出n个时钟信号;故实现了第i个时钟信号和第i+1个时钟信号的相位差与第i个计数器的计数值之间的关联和反馈;综上,提高了各个相邻的时钟信号的相位差的均匀性。

- 还没有人留言评论。精彩留言会获得点赞!