电路板和包括该电路板的半导体封装的制作方法

实施例涉及电路板和包括该电路板的半导体封装。

背景技术:

1、电子部件的小型化、重量减轻和集成度正在加速,因此,电路线宽变得更小。特别地,半导体芯片的设计规则正在集成于纳米级,因此,其上安装有半导体芯片的封装衬底或电路板的电路线宽变得更小到几微米以下。

2、已经提出了各种方法来增加电路板的电路集成度(即,使电路线宽减到最小)。例如,已经提出了sap(半增材工艺)方法和msap(改进半增材工艺)方法来防止在镀铜之后形成图案的蚀刻工艺期间电路线宽的损失。

3、从那时起,在工业中已经使用将铜箔嵌入绝缘层内的嵌入式迹线衬底(ets)方法来实现更精细的电路图案。ets方法是一种将铜电路嵌入绝缘层内的制造方法,而不是使铜电路突出到绝缘层的表面上来形成铜电路。因此,不存在由于蚀刻引起的电路损耗,这有利于使电路节距减到最小。

4、同时,如上所述将芯片安装在电路板上,或者将电路板与外部设备的主板组合以形成封装衬底。

5、为此,在设置在电路板的最外侧的保护层中形成凹槽,并且用于安装芯片或组合主板的焊球设置在凹槽中。另外,可以通过将芯片安装在焊球上或组合主板,然后形成模塑层来制造封装衬底。

6、然而,根据现有技术,当焊球设置在电路板上时,在焊球和与焊球结合的金属层之间形成金属间化合物(imc)。此时,当在制造封装衬底的过程中注入用于形成模塑层的模塑液时,存在由于模塑液注入压力引起的损坏被传递到金属间化合物(imc)的问题,并且因此在金属间化合物(imc)中出现裂纹。另外,当在金属间化合物(imc)中出现裂纹时,由于金属间化合物(imc)的分离而发生芯片或主板与电路板分离的可靠性问题。

7、因此,需要一种能够使由于模塑液注射压力而传递到金属间化合物(imc)的损坏减到最小的结构。

技术实现思路

1、[技术问题]

2、实施例提供了一种具有新颖结构的电路板和包括该电路板的半导体封装。

3、另外,实施例提供了一种能够提高金属间化合物(imc)的可靠性的电路板和包括该电路板的半导体封装。

4、另外,实施例提供了一种能够增加连接部分与焊盘之间的接触面积的电路板和包括该电路板的半导体封装。

5、所提出的实施例要解决的技术问题不限于上述技术问题,所提出的实施例所属领域的技术人员可以从以下描述清楚地理解未提及的其他技术问题。

6、[技术方案]

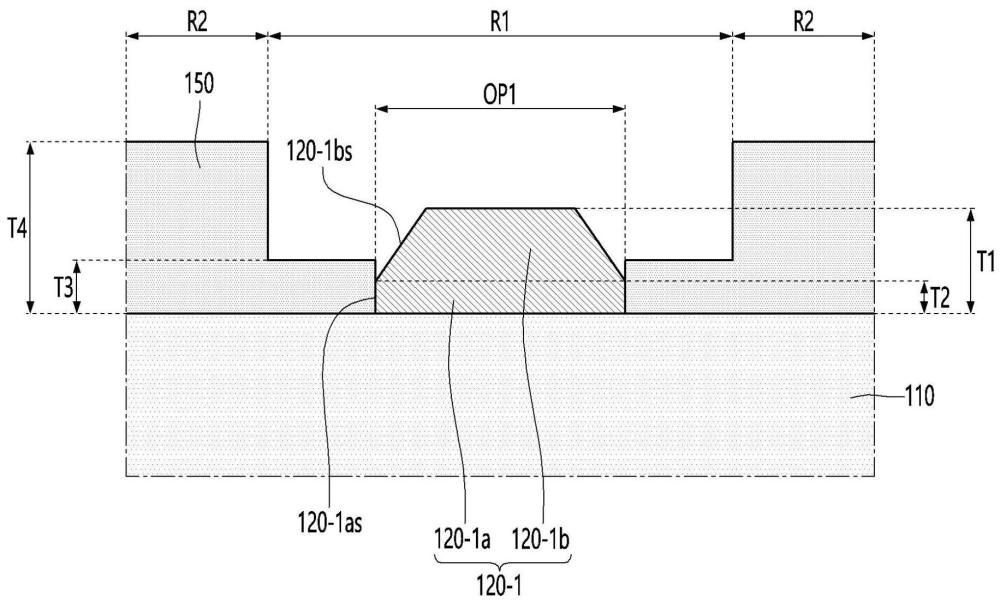

7、根据实施例的电路板包括:绝缘层;第一电路图案,所述第一电路图案设置在所述绝缘层上;以及第一保护层,所述第一保护层设置在所述绝缘层上并且包括与所述第一电路图案垂直重叠的第一开口部分,其中,所述第一保护层包括第一区域和第二区域,所述第一区域包括所述第一开口部分并且具有第一厚度,所述第二区域具有大于所述第一厚度的第二厚度而不包括所述第一开口部分,其中,所述第一区域的所述第一厚度小于所述第一电路图案的第三厚度,其中,构成所述第一开口部分的所述第一区域的内侧表面包括第一内侧表面和第二内侧表面,所述第一内侧表面与所述第一电路图案的外侧表面直接接触,所述第二内侧表面与所述第一电路图案的外侧表面间隔开。

8、另外,所述第一区域的所述第二内侧表面连接到所述第一区域的所述第一内侧表面,并且具有与所述第一内侧表面的斜率对应的斜率。

9、另外,所述第二区域的所述第二厚度大于所述第一电路图案的所述第三厚度。

10、另外,所述第一电路图案包括宽度朝向所述第一电路图案的上表面减小的区域,并且所述第一区域的所述第二内侧表面与所述第一电路图案的宽度减小的区域的外侧表面间隔开。

11、另外,所述第一区域的所述第一厚度在所述第一电路图案的所述第三厚度的20%至90%的范围内。

12、另外,所述第一电路图案包括第一部分和第二部分,所述第一部分设置在所述绝缘层的上表面并且具有与所述第一区域的所述第一内侧表面接触的外侧表面,所述第二部分设置在所述第一部分上并且具有不接触所述第一保护层的外侧表面,其中,所述第二部分包括宽度小于所述第一部分的宽度的区域。

13、另外,所述第一开口部分的宽度对应于所述第一部分的宽度。

14、另外,所述第一部分具有在所述第一区域的所述第一厚度的20%至90%的范围内的第四厚度。

15、另外,所述第二部分的外侧表面具有使宽度朝向所述第二部分的上表面逐渐减小的线性斜率。

16、另外,所述第二部分的外侧表面包括具有使宽度朝向所述第二部分的上表面减小的特定曲率的弯曲斜率。

17、另外,最靠近所述第一部分的所述第二部分的宽度小于最靠近所述第二部分的所述第一部分的宽度,并且所述第一电路图案包括设置在所述第一部分与所述第二部分之间的台阶部分。

18、另外,所述第二部分的外侧表面具有使宽度朝向所述第二部分的上表面减小的斜率或使宽度朝向所述第二部分的上表面不改变的斜率。

19、另外,所述第二部分包括第一子部分和第二子部分,所述第一子部分的外侧表面具有第一斜率,所述第二子部分的外侧表面具有不同于所述第一斜率的第二斜率。

20、另外,所述第一保护层包括设置在所述第一区域与所述第二区域之间的边界处并且在所述第一保护层的向内方向上凹陷的凹陷部分。

21、此外,电路板还包括设置在所述第一电路图案上的表面处理层,并且所述表面处理层的最下端定位成低于所述第一区域的上表面。

22、另外,所述表面处理层的至少一部分与所述第一区域的所述第二内侧表面接触。

23、另外,所述第一部分的外侧表面的表面粗糙度不同于所述第二部分的外侧表面的表面粗糙度。

24、同时,根据实施例的半导体封装包括:绝缘层;第一电路图案,所述第一电路图案设置在所述绝缘层上;第一保护层,所述第一保护层设置在所述绝缘层上并且包括与所述第一电路图案垂直重叠的第一开口部分;第一连接部分,所述第一连接部分设置在所述第一电路图案上,与所述第一保护层的所述第一开口部分垂直重叠;以及半导体器件,所述半导体器件安装在所述第一连接部分上,其中,所述第一保护层包括第一区域和第二区域,所述第一区域包括所述第一开口部分并具有第一厚度,所述第二区域具有大于所述第一厚度的第二厚度而不包括所述第一开口部分,所述第一区域的所述第一厚度小于所述第一电路图案的第三厚度,在构成所述第一开口部分的所述第一区域的内侧表面与所述第一电路图案的外侧表面之间形成缝隙(crevice),并且所述第一连接部分的至少一部分设置在所述缝隙中。

25、另外,所述第一保护层包括设置在所述第一区域与所述第二区域之间的边界处并且在所述第一保护层的向内方向上形成的凹陷部分,并且所述第一连接部分的至少一部分设置在所述凹陷部分中。

26、[有益效果]

27、实施例包括绝缘层、设置在绝缘层上的第一电路图案、以及设置在绝缘层上的第一保护层,第一保护层包括与第一电路图案垂直重叠的第一开口部分。

28、即,第一保护层包括与第一开口部分相邻并包括第一开口部分的第一区域。另外,第一保护层包括与第一区域相邻的第二区域。此时,第一区域的上表面的高度低于第二区域的上表面的高度。优选地,第一区域的上表面的高度低于第一电路图案的上表面的高度。因此,实施例在由于保护层的曝光分辨率而未设置保护层的区域中,可以布置包括具有第一开口部分的第一区域和第二区域的第一保护层。另外,第一区域围绕第一电路图案设置,同时包括宽度与第一电路图案基本相同的第一开口部分。

29、因此,实施例可以稳定地保护第一电路图案免受由各种应力引起的损坏。因此,实施例可以提高第一电路图案的物理可靠性和/或电气可靠性。

30、此时,可以在第一保护层的第一区域的内侧表面与第一电路图案的外侧表面之间形成缝隙。

31、具体地,第一区域的内侧表面包括与第一电路图案的外侧表面接触的第一内侧表面、和通过缝隙与第一电路图案的外侧表面间隔开而不接触第一电路图案的外侧表面的第二内侧表面。

32、另外,实施例允许在缝隙中设置表面处理层和/或焊料。因此,实施例可以增加由于设置焊料而形成的金属间化合物与第一保护层的最上表面之间的距离。因此,实施例可以极大地减少金属间化合物中裂纹的发生,从而提高电路板和半导体封装的物理可靠性和/或电气可靠性。

33、此外,实施例可以在不增加第一保护层的厚度的情况下,通过使用缝隙来增加距离。因此,实施例可以实现电路板和半导体封装的减薄。

34、另外,第一电路图案的外侧表面包括接触第一保护层的第一区域的外侧表面的第一外侧表面和不接触第一保护层的第二外侧表面。另外,第二外侧表面的表面粗糙度可以大于第一外侧表面的表面粗糙度。因此,实施例可以确保设置在第二外侧表面上的表面处理层与第一电路图案之间的粘合,从而提高电路板和包括该电路板的半导体封装的物理可靠性和/或电气可靠性。

35、另外,实施例通过控制第一区域的厚度,允许在第一区域与第二区域之间的边界处向内形成凹陷部分。另外,在接合焊料的工艺中,凹陷部分可以填充有诸如焊料的连接部分。另外,设置在凹陷部分中的连接部分可以用作锚固件,从而提高连接部分与第一电路图案之间的接合强度。

- 还没有人留言评论。精彩留言会获得点赞!