多栅极混合沟道场效应晶体管的制作方法

本发明涉及场效应晶体管(field effect transistor,fet)和用于制造fet的方法。本发明提出了一种多栅极混合沟道fet结构。fet结构可用于制造集成器件,如纳米片器件或叉片器件。

背景技术:

1、包括fet结构的集成器件可以通过增加有效晶体管宽度来提高器件性能。这可以通过使用用于形成fet结构的多个半导体沟道层的堆叠来实现。有效晶体管宽度取决于沟道层中每个沟道层的沟道宽度和沟道高度,并且取决于所使用的沟道层的总数。

2、因此,增加有效晶体管宽度的一种方法是增加沟道层的数量。但是,该数量受到最底沟道层的效率的限制。由于以下事实:较低沟道层上的电压逐渐降低,因此可以观察到沿这些层的电流降低。

技术实现思路

1、本发明旨在以不同的方式增加fet结构和/或集成器件中的有效晶体管宽度。例如,本发明的目标是在三门叉片状器件中获得更好的有效宽度。因此,本发明旨在提高器件性能。

2、这通过独立权利要求中描述的本发明的方案来实现。有利实现方式在从属权利要求中定义。

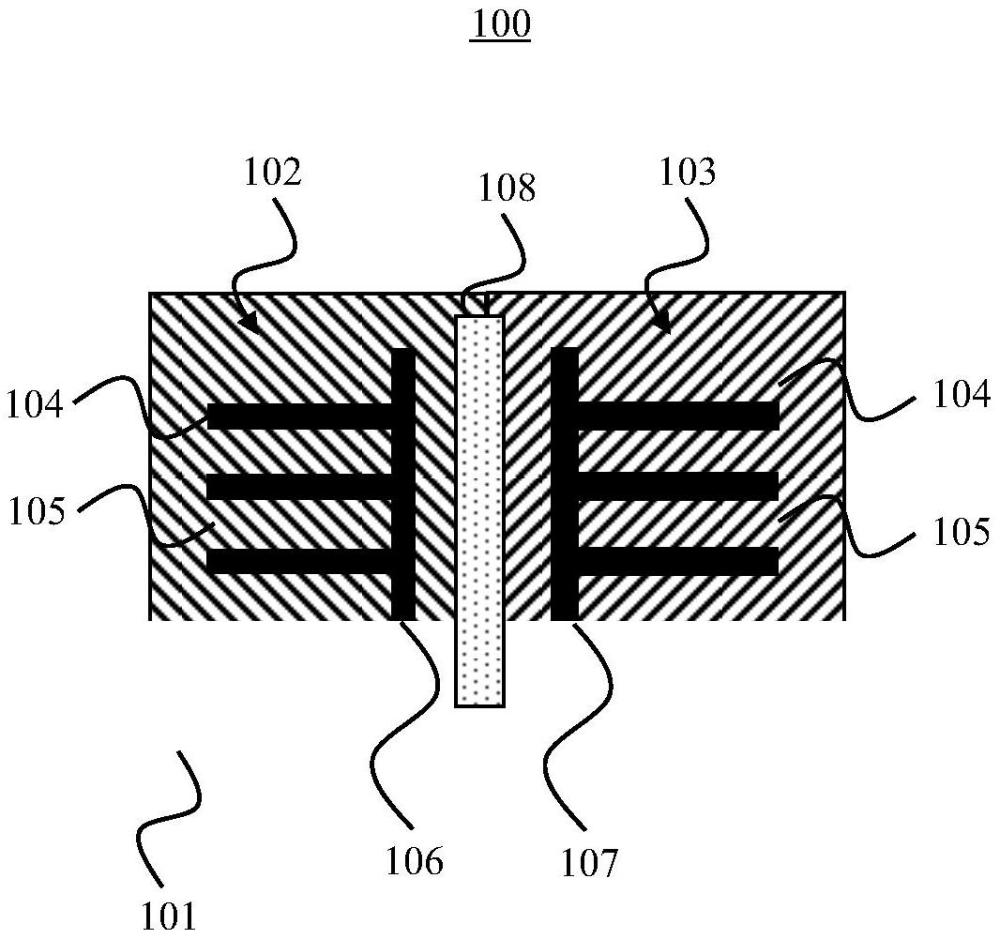

3、本发明的第一方面提供了一种用于纳米片器件的fet结构,所述fet结构包括:衬底层;第一层堆叠和第二层堆叠,并排布置在所述衬底层上,其中,所述第一层堆叠和所述第二层堆叠各自包括一个或多个半导体沟道层和一个或多个栅极层,所述一个或多个半导体沟道层和所述一个或多个栅极层沿垂直于所述衬底层的表面的第一方向以交替方式堆叠,其中,所述半导体沟道层和所述栅极层的相应表面平行于所述衬底层的所述表面;至少第一附加半导体沟道层和第二附加半导体沟道层,所述第一附加半导体沟道层布置在所述第一层堆叠旁边,所述第二附加半导体沟道层布置在所述第二层堆叠旁边,其中,所述第一附加半导体沟道层和所述第二附加半导体沟道层的相应表面彼此平行且垂直于所述衬底层的所述表面;介电壁,布置在所述衬底层上在位于一侧的所述第一层堆叠和所述第一附加半导体沟道层与位于另一侧的所述第二层堆叠和所述第二附加半导体沟道层之间。

4、第一附加半导体沟道层和第二附加半导体沟道层可以各自是沿第一方向延伸的鳍状结构,例如,各自可以是垂直鳍。例如,每个附加半导体沟道层具有高长宽比,即每个附加半导体沟道层向第一方向(层长度/高度)的延伸部与每个附加半导体沟道层向垂直于第一方向的第二方向(层厚度)的延伸部之比。附加半导体沟道层可以增加每层堆叠中的有效晶体管宽度。例如,可能的总宽度增益可以是2*n*vp,其中,n是层堆叠中的半导体沟道层的数量,vp是层堆叠中的这些沟道层的间距,这些沟道层沿第一方向堆叠(其中,栅极层布置在这些沟道层之间)。附加半导体沟道层可以设置在第一层堆叠与第二层堆叠之间的间隙内,该间隙足够大,使得附加半导体沟道层所占用的空间可以忽略不计。第一方面的fet结构可以提供电流增益,并且可以提高集成器件的器件性能。

5、在所述第一方面的一种实现方式中,所述第一附加半导体沟道层邻接所述第一层堆叠;并且/或者所述第二附加半导体沟道层邻接所述第二层堆叠。

6、因此,两个层堆叠之间占用的空间最少。

7、在所述第一方面的一种实现方式中,所述fet结构还包括:第三附加半导体沟道层,布置在所述第一层堆叠旁边,且位于所述第一层堆叠的另一侧,所述另一侧不是所述第一附加半导体沟道层所在的一侧;第四附加半导体沟道层,布置在所述第二层堆叠旁边,且位于所述第二层堆叠的另一侧,所述另一侧不是所述第二附加半导体沟道层所在的一侧;其中,所述介电壁布置在位于一侧的所述第一层堆叠、所述第一附加半导体沟道层和所述第三附加半导体沟道层与位于另一侧的所述第二层堆叠、所述第二附加半导体沟道层和所述第四附加半导体沟道层之间。

8、这可以进一步增加有效晶体管沟道宽度,从而增加电流增益。

9、在所述第一方面的一种实现方式中,所述第三附加半导体沟道层邻接所述第一层堆叠;并且/或者所述第四附加半导体沟道层邻接所述第二层堆叠。

10、通过这种方式,可以实现紧凑的fet结构。

11、在所述第一方面的一种实现方式中,每个附加半导体沟道层与所述层堆叠隔开,且布置在所述层堆叠旁边。

12、在所述第一方面的一种实现方式中,所述第一层堆叠和所述第一附加半导体沟道层形成n型fet(n-type fet,n-fet);并且/或者所述第二层堆叠和所述第二附加半导体沟道层形成p型fet(p-type fet,p-fet)。

13、在所述第一方面的一种实现方式中,布置在所述第一层堆叠旁边的每个附加半导体沟道层由n型硅基半导体材料制成;并且/或者布置在所述第二层堆叠旁边的每个附加半导体沟道层由p型硅基半导体材料制成。

14、在所述第一方面的一种实现方式中,每个附加半导体沟道层包括一个或多个由硅制成的部分和一个或多个由硅锗制成的部分。

15、由于硅锗的迁移率较高,附加半导体沟道层的硅和硅锗异质结构可以产生更多的电流增益。

16、在所述第一方面的一种实现方式中,每个附加半导体沟道层的所述一个或多个由硅制成的部分分别布置在所述层堆叠的所述一个或多个半导体沟道层旁边,所述附加半导体沟道层布置在所述层堆叠旁边。

17、在所述第一方面的一种实现方式中,所述第一层堆叠的所述一个或多个栅极层由n型功函数金属制成;所述第二层堆叠的所述一个或多个栅极层由p型功函数金属制成。

18、在所述第一方面的一种实现方式中,所述fet结构还包括:第一全环绕栅极(gateall around,gaa)结构,围绕所述第一层堆叠和布置在所述第一层堆叠旁边的每个附加半导体沟道层,其中,所述第一层堆叠的所述一个或多个栅极层与所述第一gaa结构一体地形成;和/或第二gaa结构,围绕所述第二层堆叠和布置在所述第二层堆叠旁边的每个附加半导体沟道层,其中,所述第二层堆叠的所述一个或多个栅极层与所述第二gaa结构一体地形成。

19、这种gaa结构有利于制造集成器件,例如,使用所述第一方面的fet结构的纳米片器件或叉片器件。

20、在所述第一方面的一种实现方式中,所述fet结构还包括介电材料,布置在所述衬底层上并包围所述第一层堆叠、所述第二层堆叠、每个附加半导体沟道层、每个gaa结构和所述介电壁。

21、在所述第一方面的一种实现方式中,所述第一层堆叠、布置在所述第一层堆叠旁边的每个附加半导体沟道层和所述第一gaa结构形成n-fet结构;所述第二层堆叠、布置在所述第二层堆叠旁边的每个附加半导体沟道层和所述第二gaa结构形成p-fet结构。

22、本发明的第二方面提供了一种纳米片器件,所述纳米片器件包括根据第一方面或其任一实现方式的fet结构。

23、由于集成器件中包括的第一方面的fet结构,集成器件可以具有改进的器件性能。

24、本发明的第三方面提供了一种用于制造纳米片器件的fet结构的方法,所述方法包括:形成衬底层;在所述衬底层上并排形成第一层堆叠和第二层堆叠;其中,所述第一层堆叠和所述第二层堆叠各自包括一个或多个半导体沟道层和一个或多个栅极层,所述一个或多个半导体沟道层和所述一个或多个栅极层沿垂直于所述衬底层的表面的第一方向以交替方式堆叠;其中,所述半导体沟道层和所述栅极层的相应表面平行于所述衬底层的所述表面;在所述第一层堆叠旁边形成至少第一附加半导体沟道层,在所述第二层堆叠旁边形成第二附加半导体沟道层,其中,所述第一附加半导体沟道层和所述第二附加半导体沟道层的相应表面彼此平行且垂直于所述衬底层的所述表面;在所述衬底层上在位于一侧的所述第一层堆叠和所述第一附加半导体沟道层与位于另一侧的所述第二层堆叠和所述第二附加半导体沟道层之间形成介电壁。

25、所述第三方面的方法可以具有根据所述第一方面的fet结构的实现方式的实现方式,具体地,所述方法的每个实现方式可以形成所述fet结构的实现方式。因此,所述第三方面及其可能的实现方式所述的方法实现了与所述第一方面及其相应的实现方式所述的fet结构相同的优势。

- 还没有人留言评论。精彩留言会获得点赞!