一种数字抽取滤波器的制作方法

本发明涉及通信,具体涉及一种数字抽取滤波器。

背景技术:

1、数字抽取滤波器是一种线性时不变系统,其基本原理是通过对待抽取数据与滤波器的冲激响应进行卷积计算得到输出信号。一般的实现的结构是先进行滤波,再进行抽取,但这样的实现结构会导致卷积计算时会将被抽取的数据也进行计算,从而导致会产生很多无效计算。在相关技术中,多相结构可以明显避免无效计算,并且工作在高频时钟下的寄存器相比于一般结构的也会少很多,大大提高了滤波器的最大工作频率,但是这样的结构需要使用到大量的寄存器,占用了更多的面积,消耗了更多的资源。

2、因此,如何提供一种先抽取后计算且设计结构简单的数字抽取滤波器,是目前亟需解决的技术问题。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明提供一种数字抽取滤波器,以解决上述技术问题中的至少之一。

2、为达到上述目的及其他相关目的,本技术提供的技术方案如下。

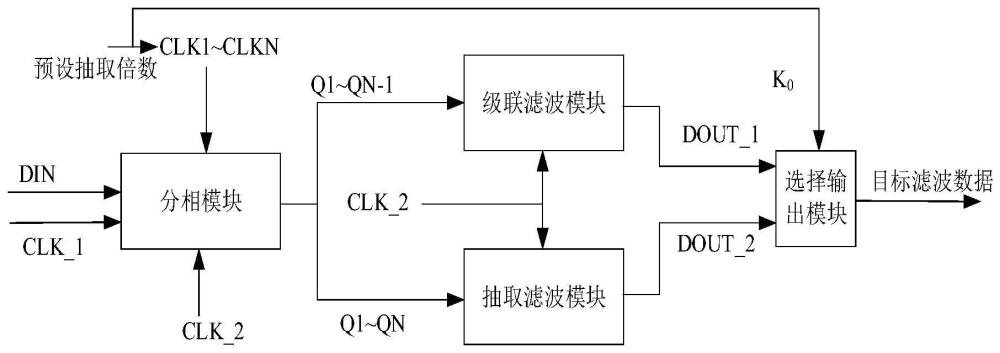

3、根据本技术实施例的一个方面,提供了一种数字抽取滤波器,包括分相模块、级联滤波模块、抽取滤波模块及选择输出模块,

4、所述分相模块接待抽取数据、第一时钟信号、多个分相驱动信号及第二时钟信号,基于所述第一时钟信号、多个所述分相驱动信号及所述第二时钟信号对所述待抽取数据进行采样及分相处理,得到与多个所述分相驱动信号一一对应的多个分相数据;

5、所述级联滤波模块的输入端接所述分相模块的输出端,所述级联滤波模块的控制端接所述第二时钟信号,所述抽取滤波模块的输入端接所述分相模块的输出端,所述抽取滤波模块的控制端接所述第二时钟信号,所述选择输出模块的两个输入端与所述级联滤波模块的输出端及所述抽取滤波模块的输出端一一对应连接,所述选择输出模块的控制端接选择控制信号;

6、其中,所述分相驱动信号的个数由预设抽取倍数确定,所述控制信号基于所述预设抽取倍数确定;

7、当所述预设抽取倍数为n-1时,所述分相驱动信号的个数为n-1,n-1个所述分相驱动信号为同频不同相位的信号,且相邻两个所述分相驱动信号之间的相位差为周期的1/(n-1),在所述第二时钟信号的控制下,开启所述级联滤波模块并关闭所述抽取滤波模块,通过所述级联滤波模块对各个所述分相数据进行n-1倍抽取并滤波,得到第一滤波数据,在所述控制信号的控制下,经所述选择输出模块选择所述第一滤波数据作为目标滤波数据向后级输出;

8、当所述预设抽取倍数为n时,所述分相驱动信号的个数为n,n个所述分相驱动信号为同频不同相位的信号,且相邻的两个所述分相驱动信号之间的相位差为周期的1/n,在所述第二时钟信号的控制下,关闭所述级联滤波模块并开启所述抽取滤波模块,通过所述抽取滤波模块对各个所述分相数据进行n倍抽取并滤波,得到第二滤波数据,在所述控制信号的控制下,经所述选择输出模块选择所述第二滤波数据作为目标滤波数据向后级输出;

9、n为大于或等于3的奇数。

10、可选地,所述分相模块包括采样单元及n个分相单元,所述采样单元的输入端接所述待抽取数据及所述第一时钟信号,基于所述第一时钟信号对所述待抽取数据进行采样,得到采样后的待抽取数据,n个所述分相单元接各个所述分相驱动信号、采样后的待抽取数据及所述第二时钟信号,基于各个所述分相驱动信号及所述第二时钟信号对采样后的待抽取数据进行分相处理,得到多个分相数据。

11、可选地,所述采样单元包括第一寄存器,所述第一寄存器的数据输入端接所述待抽取数据,所述第一寄存器的时钟输入端接所述第一时钟信号,所述第一寄存器的输出端对外输出采样后的待抽取数据,所述分相单元包括第二寄存器及第三寄存器,所述第二寄存器的数据输入端接所述第一寄存器的输出端,所述第二寄存器的时钟输入端接所述分相驱动信号,所述第二寄存器的输出端接所述第三寄存器的数据输入端,所述第三寄存器的时钟输入端接所述第二时钟信号,所述第三寄存器的输出端对外输出所述分相数据。

12、可选地,所述级联滤波模块包括第一滤波单元及第二滤波单元,所述第一滤波单元接各个所述分相数据及第二时钟信号,基于所述第二时钟信号对各个所述分相数据进行n-1倍数据抽取,得到第一过渡数据及第二过渡数据,所述第二滤波单元接所述第一过渡数据及所述第二过渡数据,对所述第一过渡数据及所述第二过渡数据进行奇偶运算,得到所述第一滤波数据。

13、可选地,所述第一滤波单元包括一个时间延时子单元及两个数据抽取子单元,所述时间延时子单元接各个所述分相数据和所述第二时钟信号,基于所述第二时钟信号对各个所述分相数据进行延时处理,得到下一时刻对应的各个分相数据,第一个所述数据抽取子单元接第一个所述分相数据、下一时刻的各个分相数据及(n+1)/2个滤波系数,基于(n+1)/2个所述滤波系数对第一个所述分相数据及下一时刻的各个分相数据进行加法及乘积运算,得到所述第一过渡数据,第二个所述数据抽取子单元接第一个所述分相数据至第(n+1)/2个所述分相数据、第(n+1)/2个下一个时刻的分相数据至第n-1个下一时刻的分相数据及(n+1)/2个所述滤波系数,基于(n+1)/2个所述滤波系数对第一个所述分相数据至第(n+1)/2个所述分相数据、第(n+1)/2个下一个时刻的分相数据至第n-1个下一时刻的分相数据进行加法及乘积运算,得到所述第二过渡数据。

14、可选地,所述时间延时子单元包括n-1个寄存器,n-1个寄存器的数据输入端一一对应接n-1个所述分相数据,n-1个寄存器的时钟输入端接所述第二时钟信号,n-1个寄存器的输出端输出下一时刻对应的各个分相数据。

15、可选地,所述数据抽取子单元包括(n+1)/2个加法器和(n+1)/2个乘法器,第i个加法器的输出端接第i个乘法器的第一输入端,第i个乘法器的第二输入端接第i个滤波系数,第i个乘法器的输出端接第(n+1)/2个加法器的输入端,第(n+1)/2个乘法器的第二输入端接第(n+1)/2个滤波系数,第(n+1)/2个乘法器的输出端接第(n+1)/2个加法器的输入端,其中,i为整数,0<i<(n-1)/2。

16、可选地,所述第二滤波单元包括第四寄存器、第五寄存器、第六寄存器、第七寄存器、第八寄存器、第九寄存器、第十寄存器、第一加法器、第二加法器、第三加法器、第四加法器、第一乘法器、第二乘法器、第三乘法器及第四乘法器,所述第四寄存器的输出端接所述第一加法器的第一输入端,所述第四寄存器的输出端还接所述第五寄存器的数据输入端,所述第五寄存器的输出端接所述第二加法器的第一输入端,所述第五寄存器的输出端还接所述第六寄存器的数据输入端,所述第六寄存器的输出端接第二加法器的第二输入端,所述第六寄存器的输出端还接所述第七寄存器的数据输入端,所述第七寄存器的输出端接所述第一加法器的第二输入端,所述第七寄存器的输出端还接所述第八寄存器的数据输入端,所述第四寄存器的数据输入端接所述第三加法器的第一输入端,所述第八寄存器的输出端接所述第三加法器的第二输入端,所述第一加法器的输出端接所述第一乘法器的第一输入端,所述第一乘法器的第二输入端接第三个滤波系数,所述第二加法器的输出端接所述第二乘法器的第一输入端,所述第二乘法器的第二输入端接第五个滤波系数,所述第三加法器的输出端接所述第三乘法器的第一输入端,所述第三乘法器的第二输入端接第一个滤波系数,所述第九寄存器的输出端接所述第十寄存器的数据输入端,所述第十寄存器的输出端接所述第四乘法器的第一输入端,所述第四乘法器的第二输入端接第六个滤波系数,所述第四加法器的输入端接所述第一乘法器的输出端、所述第二乘法器的输出端、所述第三乘法器的输出端及所述第四乘法器的输出端,其中,所述第四寄存器的数据输入端为所述第二滤波单元的第一输入端,所述第九寄存器的数据输入端为所述第二滤波单元的第二输入端,所述第四寄存器的时钟输入端、所述第五寄存器的时钟输入端、所述第六寄存器的时钟输入端、所述第七寄存器的时钟输入端、所述第八寄存器的时钟输入端、所述第九寄存器的时钟输入端、所述第十寄存器的时钟输入端为所述第二滤波单元的时钟控制端,所述第四加法器的输出端为所述第二滤波单元的输出端。

17、可选地,所述抽取滤波模块包括m个计算单元及m-1个叠加传输单元,所述计算单元的输入端接n个所述分相数据,将n个所述分相数据与对应的滤波系数进行相乘后再相加,得到每级的过渡计算数据,所述叠加传输单元接前一级的过渡计算数据、所述第二时钟信号及当前一级的过渡计算数据,根据所述第二时钟信号将前一级的过渡计算数据进行延时处理,并将当前一级的过渡计算数据与前一级的过渡计算数据进行叠加处理,得到综合过渡数据,经m-1次叠加后,得到所述第二滤波数据,其中,m为大于或等于2的整数。

18、可选地,所述计算单元包括n个乘法器和第五加法器,第j个乘法器的输出端接所述第五加法器的输入端,其中,第j个乘法器的第一输入端接第j个分相数据,第j个乘法器的第二输入端接对应的滤波系数,所述第五加法器的输出端对外输出每级的过渡计算数据,其中,j为整数,0<j≤n。

19、可选地,所述叠加传输单元包括第十一寄存器和第六加法器,所述第十一寄存器的数据输入端接前一级的过渡计算数据,所述第十一寄存器的时钟输入端接所述第二时钟信号,所述第十一寄存器的输出端接所述第六加法器的第一输入端,所述第六加法器的第二输入端接当前一级的过渡计算数据,所述第六加法器的输出端对外输出所述综合过渡数据。

20、本技术提供一种数字抽取滤波器,包括分相模块、级联滤波模块、抽取滤波模块及选择输出模块,根据预设抽取倍数确定分相驱动信号的个数及控制信号,分相模块基于第一时钟信号、多个分相驱动信号及第二时钟信号对待抽取数据进行分相处理,得到与多个分相驱动信号一一对应的多个分相数据,当预设抽取倍数为n-1时,在第二时钟信号的控制下,关闭抽取滤波模块并开启级联滤波模块,通过级联滤波模块对多个分相数据进行n-1倍的抽取及滤波处理,得到第一滤波数据,当预设抽取倍数为n时,在第二时钟信号的控制下,开启抽取滤波模块并关闭级联滤波模块,通过抽取滤波模块对多个分相数据进行n倍的抽取及滤波处理,得到第二滤波数据,选择输出模块根据控制信号选择第一滤波数据及第二滤波数据其中之一作为目标滤波数据进行输出。本发明提供的数字抽取滤波器不仅可以避免无效计算,所需的寄存器全部工作在低频时钟下,有利于后端设计中硬件的时序检查,此外,所需的寄存器数量远远少于常规的多相结构,缩短了计算时间,节约生产成本。

- 还没有人留言评论。精彩留言会获得点赞!