存储器结构及其形成方法与流程

本发明涉及半导体制造工艺,具体涉及一种存储器结构及其形成方法。

背景技术:

1、随着半导体集成电路(integrated circuit,ic)产业的快速成长,半导体技术在摩尔定律的驱动下持续地朝更小的工艺节点迈进,使得集成电路朝着体积更小、电路精密度更高、电路复杂度更高的方向发展。集成电路发展过程中,通常功能密度逐渐增加的同时,几何尺寸逐渐减小,增加了集成电路制造的难度和复杂度。

2、闪存作为当今主流的存储载体得到迅速的推广,其技术也得到了迅猛的发展。闪存分为或非(not or,nor)型闪存和与非(not and,nand)型闪存。或非型闪存作为闪存的一种,由于具有高效的编程速度和擦除能力,得到了广泛的关注。

3、采用1t(1-transistor)器件结构的或非型闪存阵列的闪存技术被广泛用于各种嵌入式消费类电子产品等应用中。1t结构由于没有选择栅晶体管,因此拥有更小的比特(bit)面积,提高了存储集成密度即节省芯片面积、降低制造成本。或非型闪存阵列由于每一个比特的源漏都直接通过金属引出,因此可实现每一个比特位的直接访问,因此相对于与非型闪存阵列具有更高的读取速度。

4、然而,随着二维平面器件的不断微缩,闪存器件的微缩逐渐接近二维微缩的极限,或非型闪存存储器的存储密度有待提升。

技术实现思路

1、本发明解决的技术问题是如何提升或非型闪存存储器的存储密度。

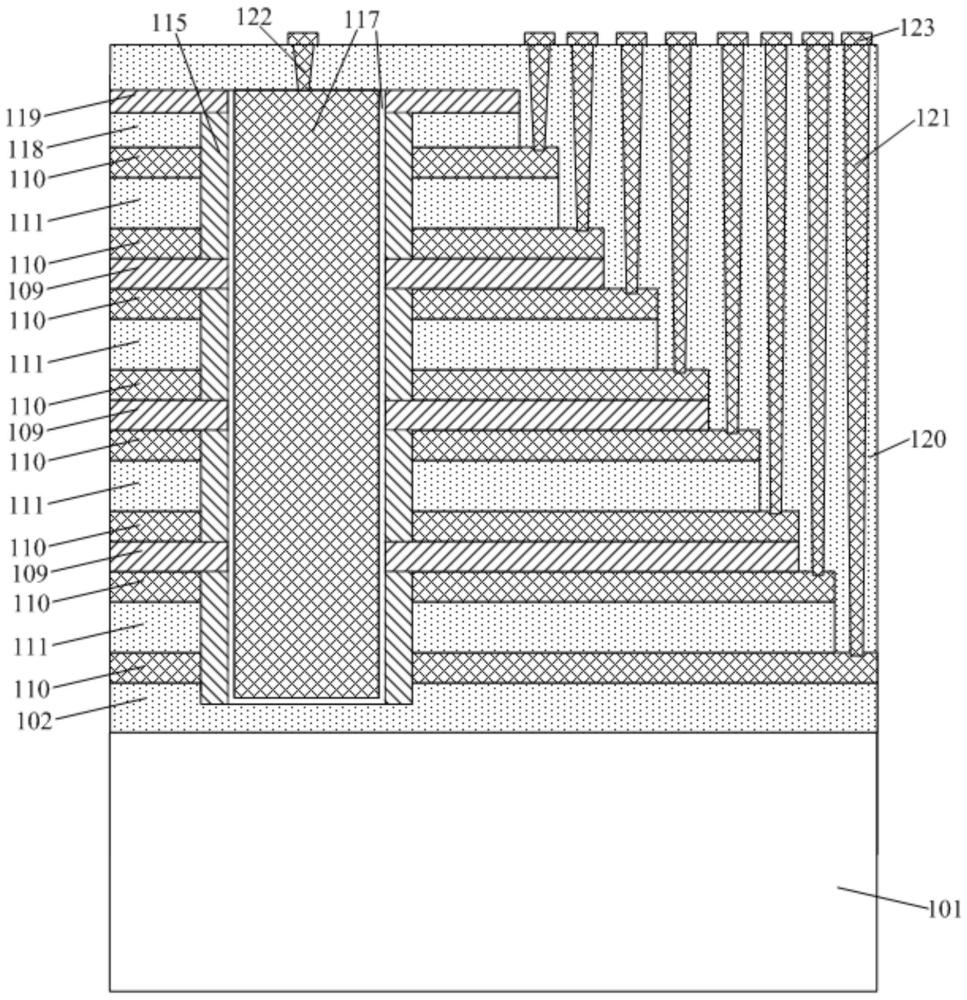

2、为解决上述技术问题,本发明实施例提供一种存储器结构的形成方法,包括:提供衬底;在所述衬底上形成阻挡层;在所述阻挡层上形成源漏层结构,所述源漏层结构包括:源漏叠层和第一隔离层,至少三个所述源漏叠层沿垂直衬底表面的方向依次堆叠,所述源漏叠层包括两个源漏掺杂层和位于所述源漏掺杂层之间的第二隔离层,所述第一隔离层位于相邻两个源漏叠层之间;形成沿垂直衬底表面的方向贯穿所述源漏层结构的栅极结构以及位于栅极结构和任一源漏叠层之间的沟道层,沿朝向所述栅极结构的方向,所述第一隔离层的端部凸出于所述源漏叠层的端部以实现相邻沟道层之间的电绝缘。

3、可选的,形成沿垂直衬底表面的方向贯穿所述源漏层结构的栅极结构以及位于栅极结构和任一源漏叠层之间的沟道层的步骤包括:形成沿垂直衬底表面的方向贯穿所述源漏层结构的第一开口,所述第一开口侧壁露出所述源漏叠层和所述第一隔离层;刻蚀所述第一开口侧壁露出的所述源漏叠层,在所述第一开口侧壁形成沟道凹槽;在所述沟道凹槽内形成沟道层;在侧壁内形成所述沟道层的第一开口内形成所述栅极结构。

4、可选的,刻蚀所述第一开口侧壁露出的所述源漏叠层,在所述第一开口侧壁形成沟道凹槽的步骤包括:刻蚀所述第一开口侧壁露出的所述第二隔离层,在所述第一开口侧壁形成初始沟道凹槽;刻蚀所述第一开口侧壁露出的所述源漏掺杂层,形成所述沟道凹槽。

5、可选的,在所述沟道凹槽内形成沟道层的步骤包括:形成初始沟道层;刻蚀所述初始沟道层,露出所述第一隔离层的端面,保留所述沟道凹槽内的初始沟道层以形成所述沟道层。

6、可选的,在所述阻挡层上形成源漏层结构包括:在所述衬底上形成阻挡层之后,在所述阻挡层上形成初始源漏层结构,所述初始源漏层结构包括:初始源漏叠层和初始第一隔离层,至少三个所述初始源漏叠层沿垂直衬底表面的方向依次堆叠,所述初始源漏叠层包括两个初始源漏掺杂层和位于所述初始源漏掺杂层之间的初始第二隔离层,所述初始第一隔离层位于相邻两个初始源漏叠层之间;形成沿垂直衬底表面的方向贯穿所述源漏层结构的栅极结构以及位于栅极结构和任一源漏叠层之间的沟道层之后,对所述初始源漏层结构进行多次连接刻蚀处理以露出任一源漏掺杂层的连接区、形成所述源漏层结构;其中,所述连接刻蚀处理包括:刻蚀上层的部分源漏掺杂结构以露出任一源漏掺杂层的连接区;露出所述连接区后,填充保护材料,所述保护材料覆盖所有露出的源漏掺杂层的连接区。

7、可选的,还包括:在所述阻挡层上形成初始源漏层结构之后,在所述初始源漏层结构上形成初始缓冲层和初始顶部隔离层;刻蚀所述初始顶部隔离层和所述初始缓冲层,露出最靠近所述缓冲层和所述顶部隔离层的源漏叠层的连接区。

8、可选的,还包括:形成位于所述阻挡层上覆盖所述源漏层结构、所述缓冲层以及顶部隔离层的层间介质层。

9、可选的,还包括:形成位于所述层间介质层内的互连结构。

10、可选的,形成位于所述层间介质层内的互连结构的步骤包括:形成位于所述层间介质层内的第一导电插塞,所述第一导电插塞与所述源漏掺杂层的连接区电连接;形成位于所述层间介质层内的第二导电插塞,所述第二导电插塞与所述栅极结构电连接;形成位于所述层间介质层上的金属层,所述金属层与所述第一导电插塞和所述第二导电插塞中的一个电连接。

11、相应的,本发明技术方案中还提供一种存储器结构,包括:衬底;位于所述衬底上的阻挡层;位于所述阻挡层上的源漏层结构,所述源漏层结构包括:源漏叠层和第一隔离层,至少三个所述源漏叠层沿垂直衬底表面的方向依次堆叠,所述源漏叠层包括两个源漏掺杂层和位于所述源漏掺杂层之间的第二隔离层,所述第一隔离层位于相邻两个源漏叠层之间;沿垂直衬底表面的方向贯穿所述源漏层结构的栅极结构;位于所述栅极结构侧壁和任一源漏叠层之间的沟道层,沿朝向所述栅极结构的方向,所述第一隔离层的端部凸出于所述源漏叠层的端部以实现相邻沟道层之间的电绝缘。

12、可选的,所述源漏掺杂层背向所述衬底一侧的表面具有连接区,所述连接区暴露于上层的部分源漏掺杂层。

13、可选的,所述连接区位于所述源漏掺杂层远离所述栅极结构的一端。

14、可选的,还包括:位于所述源漏层结构上的缓冲层以及位于所述缓冲层上的顶部隔离层;最靠近所述缓冲层和所述顶部隔离层的源漏掺杂层的连接区暴露于所述缓冲层和所述顶部隔离层。

15、可选的,还包括:位于所述阻挡层上覆盖所述源漏层结构、所述缓冲层以及顶部隔离层的层间介质层。

16、可选的,还包括:位于所述层间介质层内的互连结构。

17、可选的,所述互连结构包括:位于所述层间介质层内的第一导电插塞和第二导电插塞以及位于所述层间介质层上的金属层,所述第一导电插塞电连接所述连接区和所述金属层;所述第二导电插塞电连接所述栅极结构和所述金属层。

18、可选的,所述阻挡层还延伸至所述栅极结构和所述衬底之间。

19、可选的,沿朝向所述衬底的方向,所述栅极结构延伸入所述阻挡层内。

20、与现有技术相比,本发明实施例的技术方案具有以下有益效果:

21、在本发明技术方案的存储器结构的形成方法中,所述沿垂直衬底表面的方向依次堆叠的源漏叠层、沿垂直衬底表面的方向贯穿所述源漏层结构的栅极结构以及位于所述栅极结构侧壁和任一源漏叠层之间的沟道层的存储器结构增大了存储器结构的存储容量,并且所述源漏层结构在平行于衬底表面方向的占用面积仅为1个源漏叠层在平行于衬底表面方向的占用面积,所述存储器结构在增大存储容量时不增大在平行于衬底表面方向的面积,提升了存储器的存储密度。

22、本发明可选方案中,还包括:形成位于所述层间介质层内的互连结构。所述第一导电插塞与所述源漏掺杂层的连接区电连接,所述第一导电插塞将各源漏掺杂层引出,实现了对该具有多个源漏叠层的存储器各源漏掺杂层的直接控制,提升了存储器结构的工作速度。

23、在本发明技术方案的存储器结构中,所述沿垂直衬底表面的方向依次堆叠的源漏叠层、沿垂直衬底表面的方向贯穿所述源漏层结构的栅极结构以及位于所述栅极结构侧壁和任一源漏叠层之间的沟道层的存储器结构增大了存储器结构的存储容量,并且所述源漏层结构在平行于衬底表面方向的占用面积仅为1个源漏叠层在平行于衬底表面方向的占用面积,所述存储器结构在增大存储容量时不增大在平行于衬底表面方向的面积,提升了存储器的存储密度。

- 还没有人留言评论。精彩留言会获得点赞!