基于逐次逼近逻辑的RC振荡器校准电路、芯片及校准系统的制作方法

本技术涉及振荡器校准的,尤其涉及基于逐次逼近逻辑的rc振荡器校准电路、芯片及校准系统。

背景技术:

1、在各类电子设备中,都需要具有一定精度的时钟,振荡器是时钟电路的重要组成部分,用于向电路系统提供时序控制的标准时钟信号,使得电路系统在一定频率的时钟信号下工作。如果在芯片内部集成精准的振荡器,例如片上振荡器,在片上振荡器中,由一定的电流对电容进行充电,当电容的电压达到基准电压后开始对电容放电,放电结束后对电容充电,周而复始,产生振荡信号。在实际生产中,电容的工艺偏差一般在10%以内,在现有校准方案中,片上振荡器主要是通过改写充电电流控制字在时钟信号测试阶段对振荡频率和目标频率进行比对,测试求得频率差值,进而求得单步电流控制字变化对应的频率步长,然后通过将频率差值除以频率步长求得需要校准的步数,再由步数换算得到对应的充电电流控制字,然后通过一次性可编程存储器烧写完成校准,在实施这种校准方法的过程中,受限于频率和充电电流控制字的关系不是线性关系,在初始振荡频率相对理想频率偏差较远时,计算出的充电电流控制字不能让rc振荡器工作在目标频率区间内,充电电流控制字当中当前计算出的码值和下一次计算出的码值对应的频率差值不是恒定的,导致校准带有频率误差,特别是在要求时钟精度较高的场景下,用于驱动振荡器工作的芯片需要提高自适应校准能力。

技术实现思路

1、本技术公开基于逐次逼近逻辑的rc振荡器校准电路、芯片及校准系统,具体的技术方案如下:

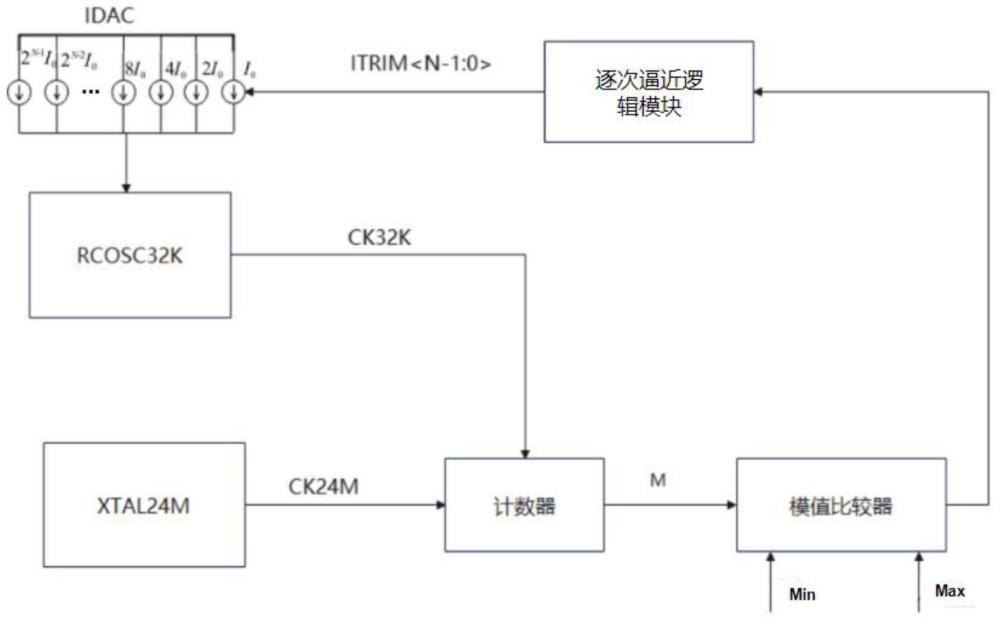

2、基于逐次逼近逻辑的rc振荡器校准电路,rc振荡器校准电路包括逐次逼近逻辑模块、电流阵列、rc振荡器、计数器和模值比较器,其中,逐次逼近逻辑模块、电流阵列、rc振荡器、计数器和模值比较器依次连接成环路;rc振荡器,用于产生待校准时钟信号;计数器,用于外接基准时钟信号,并对基准时钟信号的触发边沿进行计数;其中,待校准时钟信号的频率低于基准时钟信号的频率;模值比较器,用于每经过待校准时钟信号的时钟周期,控制计数器的计数值与测试模值区间进行比较,并根据计数器的计数值与测试模值区间之间的大小关系输出比较信号;电流阵列,用于接收逐次逼近逻辑模块产生的电流控制码值,再基于电流控制码值调节输出电流,并通过输出电流为rc振荡器内置电容提供充电电流,使得rc振荡器内置电容的充电电流发生变化时,rc振荡器产生的待校准时钟信号的频率发生变化;逐次逼近逻辑模块,用于根据所述比较信号,按照逐次逼近逻辑对电流控制码值进行调节,并根据调节后的电流控制码值调节电流阵列输出的电流,使待校准时钟信号的频率发生变化,进而让计数器的计数值逐次逼近测试模值区间,直至计数器的计数值落入测试模值区间时,确定所述待校准时钟信号校准完成。

3、综上,本技术公开的rc振荡器校准电路基于逐次逼近逻辑对待校准时钟信号的频率进行校准,而且是在逐次逼近逻辑模块、电流阵列、rc振荡器、计数器和模值比较器依次连接的环路中结合外接的基准时钟信号对所述待校准时钟信号进行校准,使能校准后,控制计数器的计数值与测试模值区间进行比较,在确定比较结果的基础上按照逐次逼近逻辑对电流控制码值进行调节,使待校准时钟信号的频率发生变化,进而在频率发生变化后的待校准时钟信号的时钟周期内带动计数器的计数值落入测试模值区间以完成校准,其中,电流控制码值在逐次逼近逻辑中会与校准步数/校准轮数相对应,则通过按照逐次逼近逻辑调节电流控制码值来改变校准步数/校准轮数,使待校准时钟信号被校准为满足预设时钟精度要求,避免在时钟测试阶段提前烧写入校准步数/校准轮数信息,而是让电路系统自动校准rc振荡器输出的时钟信号来达到预设时钟精度要求,能够实现较宽频率范围覆盖。

4、因此,本技术不受限于频率和电流控制字的关系是不是线性关系的技术障碍,也不受限于电流控制码值当中相邻两次参与调节的码值对应的频率差值不是恒定的技术障碍,在初始振荡频率相对理想频率偏差较远时,通过本技术公开的rc振荡器校准电路来自动调节电流控制码值,让计数器的计数值逐次逼近测试模值区间,进而让rc振荡器工作在目标频率区间内,提高rc振荡器的自适应校准能力。

5、进一步地,所述电流阵列包括多条并联的电流支路;每条电流支路均串接有开关,电流控制码值的位宽和电流支路的数量对应且电流控制码值的每一位的二进制值分别用于控制对应开关的通断;逐次逼近逻辑模块,用于按照电流控制码值的最高位向最低位的方向,逐位地控制电流阵列中对应的电流支路,以调节电流阵列输出的电流;其中,按照电流控制码值的最高位向最低位的方向,对应控制的各条电流支路被导通后提供的电流逐位递变。逐次逼近逻辑模块是逐位进行校准操作,按照电流控制码值的最高位向最低位的方向依次进行调节以通过电流阵列idac校准rc振荡器产生的待校准时钟信号;在校准过程中,逐次逼近逻辑模块可以先决定电流控制码值的最高位的值,然后每经过待校准时钟信号的时钟周期,待校准时钟信号的频率变化一次,待校准时钟信号的时钟周期内所容纳的基准时钟信号的触发边沿的数量也变化,即计数器的计数值也变化,在此基础上依次比较计数器的计数值是否落入测试模值区间,直至比较到电流控制码值的最低位的值,这样本技术基于电流控制码值控制对应条电流支路被导通后提供的电流按比例或指数幂递变,与现有技术相比,不采用二进制码加1或减1,减少校准步数。

6、进一步地,逐次逼近逻辑模块,用于每当模值比较器比较得到计数器的计数值大于测试模值区间的最大值时,控制电流控制码值按照二进制位减小以降低所述待校准时钟信号的频率,再使能计数器在频率降低后的待校准时钟信号的时钟周期内对基准时钟信号的触发边沿进行计数,直至计数器的计数值落入测试模值区间;逐次逼近逻辑模块,还用于每当模值比较器比较得到计数器的计数值小于测试模值区间的最小值时,控制电流控制码值按照二进制位增大以升高所述待校准时钟信号的频率,并通过rc振荡器使能计数器在频率升高后的待校准时钟信号的时钟周期内对基准时钟信号的触发边沿进行计数,直至计数器的计数值落入测试模值区间。

7、综上,逐次逼近逻辑模块,用于每当模值比较器比较得到计数器的计数值大于测试模值区间的最大值时,控制电流控制码值按照二进制位减小以降低所述待校准时钟信号的频率,再使能计数器对频率降低后的待校准时钟信号进行计数,若模值比较器比较得到计数器的计数值小于测试模值区间的最小值时,控制电流控制码值按照二进制位增大以升高所述待校准时钟信号的频率,再使能计数器在频率升高后的待校准时钟信号的时钟周期内对基准时钟信号的触发边沿进行计数,若模值比较器比较得到计数器的计数值大于测试模值区间的最大值时,控制电流控制码值按照二进制位减小以降低所述待校准时钟信号的频率,再使能计数器在频率降低后的待校准时钟信号的时钟周期内对基准时钟信号的触发边沿进行计数,如此按照逐次逼近逻辑循环运行,不断地缩小计数值的比较范围,直至计数器的计数值落入测试模值区间。

8、进一步地,所述模值比较器的第一输入端用于输入第一目标模值,所述模值比较器的第二输入端用于输入第二目标模值,所述模值比较器的第三输入端与计数器的计数输出端连接,所述模值比较器的输出端与逐次逼近逻辑模块的输入端连接;第一目标模值和第二目标模值分别是所述测试模值区间的两个端点;第一目标模值小于第二目标模值;计数器预先设置有理想模值;理想模值与第一目标模值之间的差值,等于第二目标模值与理想模值之间的差值;逐次逼近逻辑模块,用于在所述模值比较器比较得到计数器的计数值大于或等于第一目标模值,且比较得到计数器的计数值小于或等于第二目标模值的情况下,输出校准完成信号;逐次逼近逻辑模块,用于在所述模值比较器比较得到计数器的计数值小于第一目标模值的情况下,控制电流控制码值在保持原来各位二进制1的基础上,往低位方向将各位二进制0当中最高一位置位为一位二进制1,增大电流控制码值,确定按照逐次逼近逻辑完成一步校准,并将增大后的电流控制码值输出给电流阵列,以通过rc振荡器升高所述待校准时钟信号的频率;逐次逼近逻辑模块,用于在所述模值比较器比较得到计数器的计数值大于第二目标模值的情况下,控制电流控制码值中的二进制1往低位方向移一位,减小电流控制码值,确定按照逐次逼近逻辑完成一步校准,并将减小后的电流控制码值输出给电流阵列,以通过rc振荡器降低所述待校准时钟信号的频率。综上所述,计数器的计数值分别与第一目标模值和第二目标模值进行比较的过程中,无论计数器的计数值小于第一目标模值还是大于第二目标模值,逐次逼近逻辑模块先从电流控制码值的最高位开始,通过设置往低位方向置位或移位的逐次逼近方式,不断调节电流控制码值电流阵列,以间接调节rc振荡器产生的待校准时钟信号的频率,实现逐次向低位方向置位来逐步提高电流控制码值,或能够逐次向低位方向移位来逐步降低电流控制码值。

9、进一步地,所述理想模值是,基准时钟信号的频率与待校准时钟信号的频率之间的比值的取整结果;其中,计数器的计数值与所述理想模值的差值绝对值与所述待校准时钟信号的时钟周期误差存在正相关关系,以支持通过调整第一目标模值与第二目标模值来满足时钟精度需求。本技术通过调整第一目标模值与第二目标模值可以改变所述理想模值,也改变计数器的计数值所需进行比对的上下限,在对同一基准时钟信号的触发边沿计数的基础上引起比较结果出现变化并基于此自动调整电流阵列输出至rc振荡器的电流,进而影响rc振荡器所产生的待校准时钟信号的时钟周期,让待校准时钟信号满足时钟精度需求。

10、进一步地,逐次逼近逻辑模块,用于在rc振荡器起振产生待校准时钟信号时,将电流控制码值当中的最高位设置为二进制1,并将电流控制码值当中低于最高位的其余位均设置为二进制0。电流控制码值itrim<n-1:0>的初始值中,itrim<n-1>=1,itrim<n-2:0>=0。若逐次逼近逻辑模块按照逐次逼近逻辑对itrim<n-1:0>当中的二进制1进行移位,则最多可以移位n-1次,即达到电流控制码值的位宽与数值1的差值,进而在移位n-1次后,计数器的计数值落入测试模值区间时,累计进行的校准步数是n;若逐次逼近逻辑模块按照逐次逼近逻辑对itrim<n-1:0>当中的二进制0进行置1,则置1的次数最多达到n-1次,进而在置1的次数最多达到n-1次后,计数器的计数值落入测试模值区间时,累计进行的校准步数是n。综上,所述rc振荡器校准电路所需的最大校准步数等于电流控制码值的位宽。

11、进一步地,在所述模值比较器比较得到计数器的计数值小于第一目标模值的情况下,或所述模值比较器比较得到计数器的计数值大于第二目标模值的情况下,逐次逼近逻辑模块按照逐次逼近逻辑对电流控制码值进行调节所需的时间为所述待校准时钟信号的一个时钟周期,并控制校准步数加一;直至所述模值比较器比较得到计数器的计数值大于或等于第一目标模值,且比较得到计数器的计数值小于或等于第二目标模值时,校准步数小于或等于电流控制码值的位宽。在同样的设计下,若时钟精度进一步放宽,可能逼近到次低位时校准就结束;当rc振荡器需要振荡产生满足更高的时钟精度要求的时钟信号时,校准步数可以达到电流控制码值的位宽,克服更大的时钟频率偏差。

12、进一步地,电流阵列,用于在接收的电流控制码值增大后,通过增加被导通的电流支路的数量来提高输出至rc振荡器的电流,以升高所述待校准时钟信号的时钟频率;电流阵列,还用于在接收的电流控制码值减小后,通过将被导通的电流支路由提供电流大的电流支路切换为提供电流小的电流支路来降低输出至rc振荡器的电流,以降低所述待校准时钟信号的时钟频率;在所述电流控制码值当中,其中一位的二进制值对应导通的电流支路所提供的电流值为低一位的二进制值对应导通的电流支路所提供的电流值的两倍。综上所述,按照电流控制码值的最高位向最低位的方向,电流阵列被逐位地导通或关断对应的电流支路,以调节电流阵列输出的电流;所述电流控制码值的每一位的值对应控制的电流支路提供的电流值为所述电流控制码值的下一位的值对应控制的电流支路提供的电流值两倍,则按照电流控制码值的最高位向最低位的方向,对应控制的各条电流支路被导通后提供的电流按指数幂逐位递变,以调整所述待校准时钟信号的频率作相应变化,再使能计数器对频率降低后的待校准时钟信号进行计数,直至计数器的计数值落入测试模值区间。在调整所述待校准时钟信号的频率变化的过程中,按照电流控制码值的最高位向最低位的方向依次进行调节,逐次逼近逻辑模块形成对电流控制码值往低位方向置位或移位的逐次逼近方式,能够逐次向低位方向置位来逐步提高电流控制码值,或能够逐次向低位方向移位来逐步降低电流控制码值,实现不断缩小计数值比较范围,提高校准效率。

13、进一步地,计数器,用于输入基准时钟信号和待校准时钟信号;计数器,用于在接收到待校准时钟信号的第一个触发边沿时,开始对基准时钟信号的触发边沿进行计数;计数器,还用于在接收到待校准时钟信号的下一个触发边沿时,确定在待校准时钟信号的时钟周期内完成对基准时钟信号的触发边沿的计数,获得计数值,并将计数值传输给模值比较器,再进行复位使计数值归零,此时,模值比较器通过比较计数值与测试模值区间之间的大小关系输出比较信号,再由逐次逼近逻辑模块根据所述比较信号对电流控制码值进行调节,并根据调节后的电流控制码值调节电流阵列输出的电流,使待校准时钟信号的频率发生变化,并开始新的一轮计数,则在新的一轮计数中是使能计数器在频率发生变化后的待校准时钟信号的时钟周期内对基准时钟信号的触发边沿进行计数,因此,计数器在接收到待校准时钟信号的第一个触发边沿后能够自动触发所述rc振荡器校准电路内其它模块工作,避免提前烧写入校准步数相关的信息,而是让所述rc振荡器校准电路在rc振荡器起振产生待校准时钟信号后,自动校准rc振荡器输出的待校准时钟信号的频率来达到预设时钟精度要求,也能够实现较宽频率范围覆盖。

14、一种芯片,包括所述基于逐次逼近逻辑的rc振荡器校准电路。本技术公开的芯片基于逐次逼近逻辑对待校准时钟信号的频率进行校准,而且是在芯片内部的逐次逼近逻辑模块、电流阵列、rc振荡器、计数器和模值比较器依次连接的环路中结合外接的基准时钟信号对所述待校准时钟信号进行校准,使能校准后,控制计数器的计数值与测试模值区间进行比较,在确定比较结果的基础上按照逐次逼近逻辑对电流控制码值进行调节,使待校准时钟信号的频率发生变化,进而在频率发生变化后的待校准时钟信号的时钟周期内带动计数器的计数值落入测试模值区间以完成校准,其中,电流控制码值在逐次逼近逻辑中会与校准步数/校准轮数相对应,则通过按照逐次逼近逻辑调节电流控制码值来改变校准步数/校准轮数,使待校准时钟信号被校准为满足预设时钟精度要求,避免在时钟测试阶段提前往芯片烧写入校准步数/校准轮数信息,而是让芯片自动校准rc振荡器输出的时钟信号来达到预设时钟精度要求,能够实现较宽频率范围覆盖。

15、一种校准系统,校准系统包括晶体振荡器与所述芯片;或者,校准系统包括晶体振荡器与所述基于逐次逼近逻辑的rc振荡器校准电路。所述校准系统不受限于频率和电流控制字的关系是不是线性关系的技术障碍,也不受限于电流控制码值当中相邻两次参与调节的码值对应的频率差值不是恒定的技术障碍,在初始振荡频率相对理想频率偏差较远时,通过本技术公开的校准系统来自动调节电流控制码值,让计数器的计数值逐次逼近测试模值区间,进而让内置的rc振荡器工作在目标频率区间内,提高内置的rc振荡器的自适应校准能力。

- 还没有人留言评论。精彩留言会获得点赞!