抑制驱动电路输出级直接通路电流的分时控制电路及方法

本发明涉及抑制驱动电路输出级直接通路电流的分时控制电路及方法,属于集成电路。

背景技术:

1、驱动电路作为ic中的一种通用电路而被广泛使用,包括数字电路中的缓冲器设计,模拟电路中的电平移位器设计、功率器件驱动电路的缓冲器设计以及io接口驱动级设计等。驱动电路中会出现大量的输出级反相器或类反相器结构,传统的反相器或类反相器结构在电压切换过程中会出现大的直接通路电流和动态功耗,从而产生同步开关噪声和地弹效应。比如,随着现今ic功能的增加,伴随而来的是io引脚数目增加,io驱动电路的数目自然也随着增加,但是由于整个ic的引脚受限,相应的电源引脚数目往往并不能成比例的增加。由于普通的多个io驱动电路同时工作时会产生很明显的地弹噪声,当这个地弹噪声达到一定数值可能会导致接收端电路接收到错误的信号电平。

2、对于需要较高输出驱动能力,输出单元中的pmos管和nmos管通常采用大宽长比器件,在输出电平转换期间,pmos管和nmos管会存在短暂的同时导通现象,从而产生短路电流,导致非常大的动态功耗。此外,对于需要传输压差较大的高电压和低电压时,输出电平转换期间,pmos管和nmos管会存在两个压差较大的电源轨短暂同时导通现象,也会产生的比较大的短路电流和动态功耗。

3、驱动电路输出级的直接通路会产生比较大的短路电流和动态功耗。整个芯片电源轨之间产生的尖峰电流不仅会导致芯片电源和地平面的抖动,同时也会影响其他输出信号产生延迟和畸变,更为严重的是,如果它的最大幅度超过了晶体管的阈值电压,将会使电路不能正常工作。输出级驱动的直接通路电流是尖峰电流的重要组成部分,抑制大尺寸驱动输出级的尖峰电流可以有效的抑制地弹效应,减小动态功耗。

4、在传统的抑制输出级驱动直接通路电流方法中,如专利cn110677021a-一种抗地弹噪声的输出驱动电路,主要通过增加逻辑电路在输出驱动pmos管和nmos管的开关转换过程中引入一定的延时避免其同时导通,通过控制不同宽长比的驱动管相继开启实现静态和开关过程中电路具有不同的驱动能力。但这种方法设计复杂,面积开销大,引入的逻辑电路存在反相器设计,在输出级的两个电源轨之间会额外引入直接通路产生的短路电流。

技术实现思路

1、为了减小直接通路电流及动态功耗、提高驱动电路输出级抗地弹噪声的能力,本发明提供一种抑制驱动电路输出级直接通路电流的分时控制电路及方法,通过增加分时控制电路来调整输出级pmos晶体管和nmos晶体管的导通时间,避免其同时导通,而且分时控制电路仅由一个pmos晶体管和一个nmos晶体管组成,结构简单,不影响输出驱动能力。

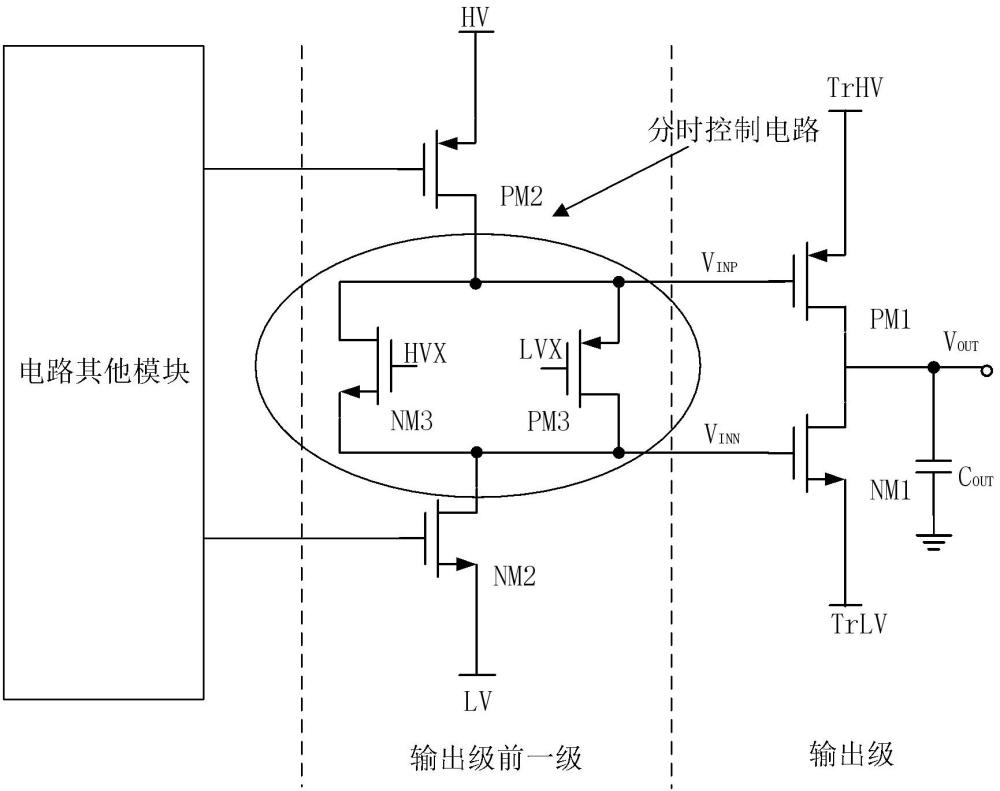

2、本发明的第一个目的在于提供一种抑制驱动电路输出级直接通路电流的分时控制电路,用于控制驱动电路输出级pmos晶体管和nmos晶体管的导通时间;所述驱动电路输出级包括传输高电压的第一pmos晶体管pm1、传输低电压的第一nmos晶体管nm1,第一pmos晶体管pm1的源端连接传输的第一高压(命名为trhv),第一nmos晶体管的源端连接传输的第一低压(命名为trlv),第一pmos晶体管pm1的漏端和第一nmos晶体管nm1的漏端连接,第一pmos晶体管pm1、第一nmos晶体管nm1的栅极连接驱动电路输出级前一级的输出信号,驱动电路输出级前一级输出信号控制输出级进行trlv、trhv输出切换。

3、可选地,所述输出级前一级包括传输第二高压(命名为hv)的第二pmos晶体管pm2、传输第二低压(命名为lv)的第二nmos晶体管nm2。第二pmos晶体管pm2的源极连接第二高压hv,第二nmos晶体管nm2的源极连接第二低压lv,第二pmos晶体管pm2、第二nmos晶体管nm2的漏极连接分时控制电路,第二pmos晶体管pm2、第二nmos晶体管nm2的栅极连接电路其他模块的端口。

4、进一步地,电路其他模块可包括移位寄存器、fifo存储器、电平移位器、io电路设计等。

5、进一步地,所述分时控制电路包括第三pmos晶体管pm3、第三nmos晶体管nm3,第三pmos晶体管pm3、第三nmos晶体管nm3组成类传输门结构,第三pmos晶体管pm3的栅极连接第三低压(命名为lvx),第三nmos晶体管nm3的栅极连接第三高压(命名为hvx)。第三pmos晶体管pm3源极、第三nmos晶体管nm3的漏极与输出前一级中第二pmos晶体管pm2的漏极连接,第三pmos晶体管pm3漏极、第三nmos晶体管nm3的源极与输出前一级中第二nmos晶体管nm2的漏极连接。

6、所述第一高压电压值满足关系式:;

7、所述第一低压电压值满足关系式:;

8、所述第三低压lvx电压值满足关系式:;

9、所述第三高压hvx电压值满足关系式:。

10、所述的由第一pmos晶体管pm1、第一nmos晶体管nm1组成的输出级设计中,输出级驱动的前一级的上升时间和下降时间合理假设为具有一定斜率的直线,斜率的大小与输出级pmos晶体管、nmos晶体管的尺寸成正比。输入信号不为无穷大的斜率造成了开关过程中第一高压和第一低压之间在短期内出现一条直接通路,此时第一pmos晶体管pm1、第一nmos晶体管nm1同时导通。所述的直接通路引起的功耗与开关活动性成正比,这类似于电容功耗。

11、所述的直接通路引起的尖峰电流由器件的饱和电流决定,因此正比于驱动电路输出级第一pmos晶体管pm1、第一nmos晶体管nm1的尺寸。所述的尖峰电流也与输入和输出的上升/下降时间之比密切相关。考虑不采取抑制地弹噪声的传统驱动电路输出级的连接方法,传统驱动电路输出级的第一pmos晶体管pm1、第一nmos晶体管nm1的栅极与前一级的输出连接。

12、当所述传统驱动电路输出级在输入端发生由第二低压lv到第二高压hv翻转时,假设负载电容很大,输出的下降时间明显大于输入的上升时间。在这种情况下输入在输出开始改变之前就已经通过了过渡区。由于在这一时期驱动电路输出级的第一pmos晶体管pm1的源漏电压近似为0v,因此该器件在传输电流之前就已经关断了,直接通路电流近似为0v,尖峰电流主要由于输出级晶体管对大的负载电容的充放电产生。

13、当所述传统驱动电路输出级在输入端发生在由第二低压lv到第二高压hv翻转时,假设负载电容很小,输出的下降时间明显小于输入的上升时间。在这种情况下这一时期驱动电路输出级的第一pmos晶体管pm1的源漏电压大部分时间内等于第二高压hv与第二低压lv的差值,从而引起了最大的直接通路电流,该情况是短路电流最大的情况,尖峰电流主要由直流通路引起的短路电流和输出级晶体管对小的负载电容的充放电电流。

14、所述抑制驱动电路输出级直接通路电流的方法,通过在输出级前一级增加分时控制电路,使得第一pmos晶体管pm1的栅极传输第二低压lv需要经过第二nmos晶体管nm2、第三nmos晶体管nm3,第一pmos晶体管pm1的栅极传输第二高压hv需要经过第二pmos晶体管pm2。

15、所述抑制驱动电路输出级直接通路电流的方法,通过在输出级前一级增加分时控制电路,使得第一nmos晶体管nm1的栅极传输第二低压lv需要经过第二nmos晶体管nm2,第一nmos晶体管nm1的栅极传输第二高压hv需要经过第二pmos晶体管pm2、第三pmos晶体管pm3。

16、所述驱动电路输出级的第一pmos晶体管pm1的栅极电压命名为,所述驱动电路输出级的第一nmos晶体管nm1的栅极电压命名为。

17、当所述输出级的前一级加上分时控制电路后,比更快地传输第二高压hv,、同时增大,当之前,,所述驱动电路输出级的第一nmos晶体管nm1还没打开,第一pmos晶体管pm1已经关断,这时不存在直接通路电流了,可有效地减小尖峰电流,降低动态功耗,提高驱动电路输出级抗地弹噪声能力。

18、当所述输出级的前一级加上分时控制电路后,比更快地传输第二低压lv,、同时减小,当之前,,所述驱动电路输出级的第一pmos晶体管pm1还没打开,第一nmos晶体管nm1已经关断,此时不存在直接通路电流了,可有效地减小尖峰电流,降低动态功耗,提高驱动电路输出级抗地弹噪声能力。

19、当所述输出级的前一级加上分时控制电路后,在升压到之前,还没有完全升压到,或者在降压到之前,还没有完全降压到,此时相比传统驱动电路输出级存在一段时间更短的直流通路时间,产生的直接通路电流也会减小,可有效地减小尖峰电流,降低动态功耗,提高驱动电路输出级抗地弹噪声能力。

20、所述的驱动电路输出级抑制直接通路电流的方法通过对输出级前一级增加分时控制电路来实现的,不会改变驱动电路的输出驱动能力。

21、本发明有益效果是:

22、相对于现有技术,本发明实施为了抑制驱动电路输出级的直接通路电流,通过在输出级前一级增加分时控制电路调整输出级pmos晶体管和nmos晶体管的导通时间,避免其同时导通,从而避免了电压切换过程中会出现大的直接通路电流,且由于直接通路电流是尖峰电流的重要组成部分,避免了直接通路电流即抑制了驱动输出级的尖峰电流,进而有效抑制了地弹效应,减小动态功耗。而且本技术是在输出级前一级增加分时控制电路来实现抑制驱动电路输出级直接通路电流,没有对驱动电路部分进行任何改变,不影响输出驱动能力。本技术分时控制电路由一个pmos晶体管和一个nmos晶体管组成,相比于现有技术,设计简单,面积开销小。本发明适用于数字驱动电路、io接口驱动电路、模拟驱动电路,相比于增加逻辑电路抑制地弹效应的方法,应用场景更为宽泛。

- 还没有人留言评论。精彩留言会获得点赞!