三维存储器及其制造方法与流程

本发明涉及半导体制造,尤其涉及一种三维存储器及其制造方法。

背景技术:

1、随着技术的发展,半导体工业不断寻求新的方式生产,以使得存储器装置中的每一存储器裸片具有更多数目的存储器单元。在非易失性存储器中,例如nand存储器,增加存储器密度的一种方式是通过使用垂直存储器阵列,即3d nand(三维nand)存储器;随着集成度的越来越高,3d nand存储器已经从32层发展到64层,甚至更高的层数。ctf(charge trapflash,电荷捕获闪存)型3d nand存储器是目前较为前沿、且极具发展潜力的存储器技术。

2、在ctf型3d nand存储器中,具有由层间绝缘层和栅极交替堆叠形成的堆叠结构,所述堆叠结构包括核心区域以及围绕所述核心区域设置的台阶区域。所述核心区域,用于信息的存储;所述台阶区域,位于所述堆叠结构的端部,用于向所述核心区域传输控制信息,以实现信息在所述核心区域的读写。其中,所述台阶区域具有贯穿所述堆叠结构的支撑柱,用于对所述堆叠结构进行支撑,避免所述堆叠结构出现坍塌。

3、但是,现有支撑柱的结构形貌较差,严重影响了存储器的性能。因此,如何改善支撑柱的结构形貌,提高存储器的性能,是目前亟待解决的技术问题。

技术实现思路

1、本发明提供一种三维存储器及其制造方法,用以解决现有的三维存储器中台阶区域的支撑柱结构形貌较差的问题,提高存储器的性能。

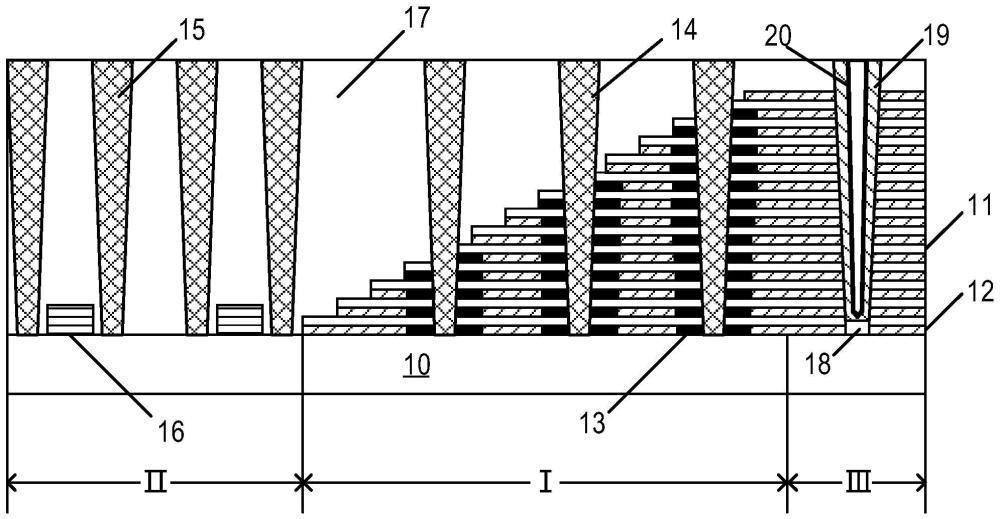

2、为了解决上述问题,本发明提供了一种三维存储器,包括:

3、衬底;

4、堆叠结构,形成于所述衬底上,包括沿垂直于所述衬底的方向依次排列的若干栅极层,所述堆叠结构的端部具有台阶区域;

5、导电支撑柱,沿垂直于所述衬底的方向贯穿所述台阶区域的堆叠结构;

6、隔离层,位于所述导电支撑柱与所述栅极层之间,用于电性隔离所述导电支撑柱与所述栅极层。

7、优选的,所述三维存储器包括若干层所述隔离层,且一层所述隔离层与所述栅极层同层设置。

8、优选的,所述堆叠结构还包括填充于相邻两层所述栅极层之间的层间绝缘层,若干层所述隔离层沿垂直于所述衬底的方向与所述层间绝缘层交替堆叠排列。

9、优选的,所述隔离层覆盖所述导电支撑柱的侧壁。

10、优选的,还包括:

11、外围区域,围绕所述堆叠结构的外围设置,所述外围区域中形成有外围电路;

12、介质层,覆盖所述外围区域与所述堆叠结构;

13、导电插塞,沿垂直于所述衬底的方向贯穿所述外围区域上方的所述介质层,并连接至所述外围电路。

14、优选的,所述导电插塞与导电支撑柱材质相同、高度相同。

15、优选的,还包括:

16、外围区域,沿垂直于所述衬底的方向层叠设置于所述堆叠结构下方,所述外围区域中形成有外围电路;

17、介质层,覆盖所述外围区域与所述堆叠结构;

18、导电插塞,沿垂直于所述衬底的方向贯穿所述外围区域上方的所述介质层,并连接至所述外围电路。

19、优选的,所述堆叠结构还包括核心区域,所述台阶区域位于所述核心区域的外围;

20、所述三维存储器还包括:

21、穿过所述核心区域的堆叠结构的存储串,所述存储串包括:

22、外延半导体层;

23、位于所述外延半导体层上的沟道层和存储器层,所述存储器层位于沟道层的外围。

24、优选的,所述三维存储器为3d nand存储器。

25、为了解决上述问题,本发明还提供了一种三维存储器的制造方法,包括如下步骤:

26、提供一衬底,所述衬底上具有堆叠层,所述堆叠层包括沿垂直于所述衬底的方向依次排列的若干栅层,所述堆叠层的端部具有阶梯区域;

27、形成通孔,所述通孔沿垂直于所述衬底的方向贯穿所述阶梯区域的堆叠层;

28、在所述通孔的外围形成隔离层;

29、向所述通孔内填充金属以形成导电支撑柱,所述隔离层位于所述导电支撑柱与所述栅层之间,用以电性隔离所述导电支撑柱与所述栅层。

30、优选的,所述堆叠层还包括填充于相邻两层所述栅层之间的层间绝缘层;形成导电支撑柱之后还包括如下步骤:

31、去除所述堆叠层中的所述栅层,在相邻两层层间绝缘层之间形成空隙区域;

32、填充导电材料于所述空隙区域,形成栅极层。

33、优选的,在所述通孔的外围形成隔离层的具体步骤包括:

34、沿所述通孔回刻蚀部分栅层,在相邻层间绝缘层之间形成一开口;

35、形成绝缘的隔离层,所述隔离层至少填充于所述开口内。

36、优选的,在所述通孔的外围形成隔离层的具体步骤包括:

37、沉积绝缘材料于所述通孔侧壁,形成所述隔离层。

38、优选的,所述衬底还包括:外围区域,所述外围区域设置于所述堆叠层外围,所述外围区域中形成有外围电路;形成通孔的具体步骤包括:

39、沉积介质层,所述介质层覆盖所述堆叠层与外围区域;

40、同时刻蚀所述阶梯区域与所述外围区域,于所述阶梯区域形成贯穿所述介质层和所述堆叠层的通孔、并同时于所述外围区域形成贯穿所述介质层的接触孔。

41、优选的,所述衬底还包括:外围区域,所述外围区域沿垂直于所述衬底的方向层叠设置于所述堆叠层下方,所述外围区域中形成有外围电路;形成通孔的具体步骤包括:

42、沉积介质层,所述介质层覆盖所述堆叠层与外围区域;

43、同时刻蚀所述阶梯区域与所述外围区域,于所述阶梯区域形成贯穿所述介质层和所述堆叠层的通孔、并同时于所述外围区域形成贯穿所述介质层的接触孔。

44、优选的,向所述通孔内填充金属以形成导电支撑柱的具体步骤包括:

45、同时沉积金属于所述通孔和所述接触孔内,于阶梯区域形成所述导电支撑柱、并同时于所述外围区域形成导电插塞;所述导电插塞与所述外围电路连接。

46、优选的,所述堆叠层还包括核心存储区域,所述阶梯区域位于所述核心存储区域的外围;

47、所述三维存储器的制造方法还包括如下步骤:

48、在形成所述通孔的同时形成沟道孔,所述沟道孔沿垂直于所述衬底的方向贯穿所述核心存储区域的堆叠层;

49、形成外延半导体层,所述外延半导体层覆盖所述沟道孔的底部;

50、形成存储器层,所述存储器层覆盖所述沟道孔的侧壁;

51、形成沟道层,所述沟道层覆盖于所述存储器层表面。

52、优选的,所述三维存储器为3d nand存储器。

53、本发明提供的三维存储器及其制造方法,在堆叠结构的台阶区域采用导电支撑柱来对堆叠结构进行支撑,相较于传统的于台阶区域刻蚀形成沟道孔、并采用选择性外延生长(selective epitaxy growth,seg)技术于沟道孔内生长硅来形成支撑柱的方式相比,本发明形成的导电支撑柱能够避免选择性外延生长技术导致的支撑柱形貌不均匀的问题,确保了三维存储器的产率,并提高了三维存储器的性能。

- 还没有人留言评论。精彩留言会获得点赞!