用于无限采样的高动态范围ADC

本发明涉及一种用于无限采样的高动态范围adc。

背景技术:

1、现有模数转换器(adc),如cn115967401a,一种流水式折叠内插型模数转器目的在于解决了现有流水式折叠插值结构模数转换器的数据转换结果,因为折叠量化曲线过零点的正确性、或比较器由于精度限制或失调电压出错,导致最终数据最终转换结果发生错误的问题;以及cn101499802b,一种改进型折叠结构adc目的在于节省了芯片的面积,且在细量化器精度允许的情况下,能够在一定程度上纠正粗量化器的精度导致在折叠点处的误差,具有较好的容错性;显然均未提及adc动态范围相关内容;新颖的无限采样(us)理论使模数转换器(adc)能够有效管理动态范围远远超过阈值电压的输入信号。然而,现有的us异步sigma-delta调制器adc(us-asdm-adc)设计在双通道架构内采用非线性调制运算来生成余数和整数部分,从而导致非理想现象造成的显著振幅损失。

技术实现思路

1、本发明的目的在于解决上述问题,提供一种用于无限采样的高动态范围adc,为us-asdm-adc提出一种新型单通道架构和反馈补偿机制,利用一个单通道折叠模块来生成剩余的模数运算,同时生成模数运算的整数部分,并通过基于施密特触发器的反馈系统启动振幅校正,避免了adc因信号幅度过大而产生饱和失真;因此,本发明可实现高动态范围的信号输入并具有较高的信噪比。

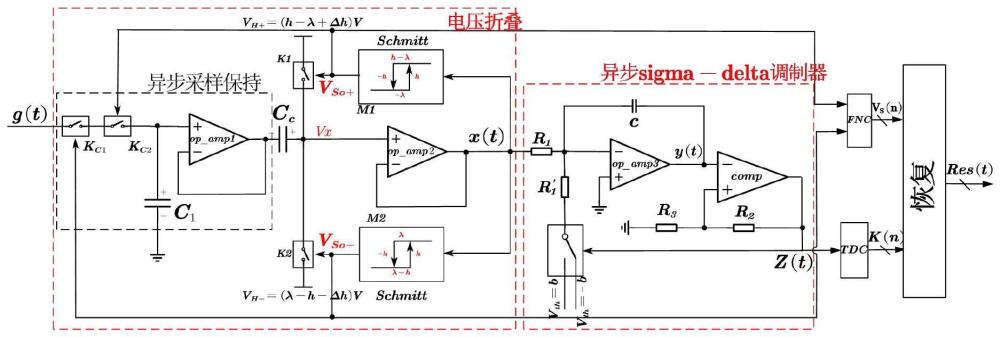

2、为实现上述目的,本发明的技术方案是:一种用于无限采样的高动态范围adc,包括电压折叠模块、asdm模块、折叠数计算模块、时间数字转换模块、信号恢复模块;其中,

3、电压折叠模块实现对输入信号g(t)的取模操作,得到模电压信号x(t);

4、asdm模块将模电压信号x(t)转化为时间信号z(t);

5、时间数字转换模块,将时间信号z(t)进行量化得到多位数字信号k(n);

6、折叠数计算模块,计算电压折叠模块的折叠数及折叠位置;

7、信号恢复模块利用折叠数计算模块的结果对数字信号k(n)进行恢复,得到恢复信号res(t)。

8、在本发明一实施例中,所述电压折叠模块包括异步采样保持模块,施密特触发器m1、m2,运算放大器amp2,开关k1、k2和耦合电容cc;异步采样保持模块的输入端作为电压折叠模块的输入端,异步采样保持模块的输出端经耦合电容cc分别与开关k1、k2的一端、运算放大器amp2的同相输入端连接,开关k1、k2的另一端连接电源,开关k1、k2的控制端分别与施密特触发器m1、m2的输出端连接,运算放大器amp2的反相输入端与输出端连接,并作为电压折叠模块的输出端。

9、在本发明一实施例中,所述异步采样保持模块包括开关kc1、kc2,电容c1和运算放大器amp1,开关kc1的一端作为异步采样保持模块的输入端,开关kc1的另一端经开关kc2分别与电容c1的一端、运算放大器amp1的同相输入端连接,开关kc1、kc2的控制端分别与施密特触发器m1、m2的输出端连接,电容c1的另一端接地,运算放大器amp1的反相输入端、运算放大器amp1的输出端、施密特触发器m1及m2的输入端连接,并作为异步采样保持模块的输出端,施密特触发器m1、m2的输出端还分别与折叠数计算模块的两输入端连接。

10、在本发明一实施例中,电压折叠模块将补偿信号ε(t)视为直流信号保存在耦合电容cc上,通过交流耦合的方式将其叠加在输入信号g(t)上;整个过程可视为,在输出信号x(t)幅度达到上阈值λ时,触发施密特触发器m2拉高施密特触发器m2的输出端节点vso-的电位,开关k2闭合,开关kc1断开,异步采样保持模块处于保持状态;与开关k2的另一端连接的电源vh-通过由开关k2的导通阻抗req2与电容cc构成的滤波单元将运算放大器amp2的同相输入端节点vx的电位下拉2hv,在节点vx达到相应阈值电压后,触发施密特触发器m2将节点vso-的电位拉低,开关k2断开,开关kc1闭合,异步采样保持模块处于采样状态;同理,当输出信号x(t)幅度达到下阈值-λ时,触发施密特触发器m1拉低施密特触发器m1的输出端节点vso+的电位,开关k1闭合,开关kc2断开,节点vx的电位被上拉2hv,在节点vx达到相应阈值电压后,触发施密特触发器m2将节点vso-的电位拉高,开关k1断开,开关kc2闭合,异步采样保持模块处于采样状态;由此实现对输入信号g(t)的幅度补偿,以防止后端asdm模块输入饱和。

11、在本发明一实施例中,所述施密特触发器m1、m2均采用6个cmos管结构。

12、在本发明一实施例中,所述asdm模块包括积分器和施密特触发器;所述积分器包括阻值相同的电阻r1、r'1,电容c,二择一开关和运算放大器amp3,电阻r1的一端作为asdm模块的输入端,电阻r1的另一端分别与电阻r'1的一端、电容c的一端、运算放大器amp3的反相输入端连接,电阻r'1的另一端与二择一开关的一端连接,二择一开关的另一端的两个输入端分别与两个电源连接,二择一开关的控制端与施密特触发器的输出端连接,并作为asdm模块的输出端,电容c的另一端与运算放大器amp3的输出端连接,运算放大器amp3的同相输入端连接至地;所述施密特触发器包括比较器、电阻r2、电阻r3,比较器的反相输入端作为施密特触发器的输入端与运算放大器amp3的输出端连接,比较器的同相输入端经电阻r3连接至地,比较器的同相输入端还经电阻r2与比较器的输出端连接,并作为施密特触发器的输出端。

13、在本发明一实施例中,所述asdm模块通过对输入信号x(t)进行占空比调制以进行时域转换,由此产生的输出信号是一个方波,其占空比符合规定的标准:

14、

15、其中αm为高电平脉宽,tm为输出信号周期,υm为输入信号的幅度,m表示输出信号周期数,b为与二择一开关的另一端的两个输入端连接的两个电源的电压中的正值电压;

16、而输出信号z(t)的频率ω0满足:

17、ω0=(1-x(t)2/2)ωc

18、其中ωc为输入信号x(t)为0时刻输出信号的角频率。

19、在本发明一实施例中,对于asdm模块输出的占空比信号可近似为时间段tm→tm+1内输入信号x(t)的均值,其满足:

20、

21、其中δ满足z(t)max即占空比信号z(t)的高电平电压,k满足r1、r2、r3、c分别表示电阻r1、电阻r2、电阻r3的阻值以及电容c的容值,tm是由时间数字转换模块测量得到的占空比信号的翻转时间,tm+1是由时间数字转换模块测量得到的占空比信号的下一个翻转时间,m是翻转的次数。

22、在本发明一实施例中,所述运算放大器amp1、运算放大器amp2均采用轨到轨输入结构,该轨到轨输入结构采用两级放大形式,由折叠共源共栅结构作为输入,共源级放大作为输出。

23、在本发明一实施例中,运算放大器amp3采用轨到轨输入结构,该轨到轨输入结构采用两级放大形式,由折叠共源共栅结构作为输入,共源级放大作为输出。

24、相较于现有技术,本发明具有以下有益效果:本发明提供一种用于无限采样的高动态范围adc,为us-asdm-adc提出一种新型单通道架构和反馈补偿机制,利用一个单通道折叠模块来生成剩余的模数运算,同时生成模数运算的整数部分,并通过基于施密特触发器的反馈系统启动振幅校正,避免了adc因信号幅度过大而产生饱和失真;因此,本发明可实现高动态范围的信号输入并具有较高的信噪比。

- 还没有人留言评论。精彩留言会获得点赞!