一种包绕式超导量子倒装芯片及制备方法与流程

本发明涉及量子器件,尤其涉及一种包绕式超导量子倒装芯片及制备方法。

背景技术:

1、随着量子计算研究的不断深入,超导量子计算方案在多个关键指标上取得了显著突破,如:在单比特和双比特量子门的操作上,保真度已分别达到和超越了99.9%和99%的重要阈值;量子比特作为衡量量子计算性能的重要指标,其数量已成功突破100位。这使得超导量子计算方案在实现实际应用方面具有巨大的潜力,进而受到各界的广泛关注。然而,随着比特数量的不断增加,传统的单平面集成方式已无法满足日益增长的比特集成需求,这成为了超导量子计算面临的一大挑战。为了克服这一挑战,研究者们开始探索新的解决方案,以实现更大规模的量子比特集成。

2、为了解决单平面上量子比特大规模集成的难题,先进封装技术被引入到超导量子芯片的制备中。这些技术,如倒装焊和tsv工艺,能够将电路结构拆分到多个平面上,并通过精确的对准和压焊工艺实现这些平面之间的高效连接。这种方法的引入不仅解决了单平面集成的限制,还为超导量子芯片向更高比特数量的发展提供了可能。通过这些先进封装技术的应用,超导量子芯片的制备效率和可靠性得到了显著提升。

3、然而,目前常用的超导量子芯片倒装焊芯片的制备,一般是先在2个独立芯片平面上制备相应的电路结构,然后分别在2个芯片电路平面上制作大规模数量分散排布的铟柱,最后利用倒装焊设备将2个芯片对准,将上下铟柱一一对准并压焊到预设的高度从而实现上下芯片的电互联。这种工艺会降低已存在的比特的性能。

技术实现思路

1、为解决上述技术问题,本技术提供了一种包绕式超导量子倒装芯片及制备方法。

2、为实现上述目的,本技术提供了一种包绕式超导量子倒装芯片,包括层叠设置的第一衬底、第一超导薄膜、金属围墙、第二超导薄膜、第二衬底,

3、所述第一超导薄膜包括第一电路层;所述第二超导薄膜包括第二电路层和约瑟夫森结;

4、所述金属围墙环绕于所述第一电路层、所述第二电路层以及所述约瑟夫森结的外围。

5、基于上述方案,金属围墙环绕于所述第一电路层、所述第二电路层以及所述约瑟夫森结的外围,有利于在制备包绕式超导量子倒装芯片的过程中,先制备金属围墙再制备电路结构或约瑟夫森结,以便于提升量子比特器件的性能。

6、作为本技术进一步的改进,在与所述第二衬底紧邻的所述第一衬底的表面上设置有第一凹槽和/或在与所述第一衬底紧邻的所述第二衬底的表面上设有第二凹槽,所述第一电路层位于所述第一凹槽内,所述第二电路层和所述约瑟夫森结位于所述第二凹槽内。压焊的过程中,金属围墙的高度以及面积不易控制,该种结构设计有利于降低对金属围墙的高度的要求,实现高精度的控制。

7、作为本技术进一步的改进,在与所述第二衬底紧邻的所述第一衬底的表面上设置有第三凹槽和在与所述第一衬底紧邻的所述第二衬底的表面上设有第四凹槽,所述金属围墙的两端分别嵌入到所述第三凹槽内和所述第四凹槽内。该种结构设计,有利于实现金属围墙的下沉式设计,在上顶片与下底片压焊的过程中,利用凹槽边缘的衬底实现限位作用,使金属围墙限位在凹槽内,有利于精确控制上顶片与下底片之间的片间距和均匀性,提升量子比特器件的性能。

8、作为本技术进一步的改进,所述第一衬底、所述第二衬底以及所述金属围墙形成封闭空腔,所述第一电路层、所述第二电路层以及所述约瑟夫森结均位于所述封闭空腔内。这种结构设计有利于将电路结构及约瑟夫森结完全包裹在金属围墙之内,实现了芯片电路结构与外界环境的完全自我隔绝,降低了芯片性能受外界环境噪声等污染的影响。

9、作为本技术进一步的改进,远离所述第一超导薄膜的所述第一衬底的表面上还设有第三超导薄膜,所述第三超导薄膜包括第三电路层,所述第一衬底上设有用于填充超导材料的tsv通孔,所述金属围墙环绕于所述tsv通孔的外围,所述第一电路层通过所述tsv通孔内的超导材料与所述第三电路层电互联。

10、基于上述方案,由于在第一衬底上设置了tsv通孔,tsv通孔内填充有超导材料,有利于将第三电路层设置在远离所述第一超导薄膜的第一衬底的表面上,大幅缩小了芯片的面积。

11、作为本技术进一步的改进,所述第一衬底和所述第二衬底的材料选自以下一种或多种:蓝宝石、本征硅;

12、所述第一超导薄膜、所述第二超导薄膜和所述第三超导薄膜的材料选自以下一种或多种:铌基超导材料、钽基超导材料、tin基超导材料、nbn基超导材料、nbtin基超导材料、al基超导材料;

13、所述金属围墙为铟柱子。

14、作为本技术进一步的改进,所述超导材料为铝、铟、tin、nbn、nbtin中的任意一种或者几种。

15、作为本技术进一步的改进,第一电路层可以包括谐振腔、读取线和控制线等,第二电路层可以为十字比特电容等,第三电路层可以为pad电路结构等。

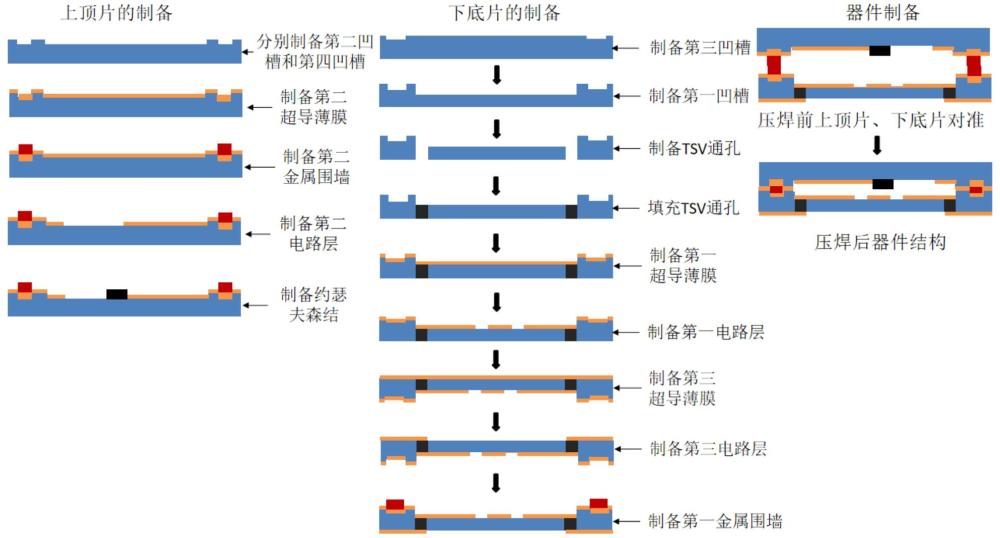

16、为实现上述目的,本技术还提供了一种包绕式超导量子倒装芯片的制备方法,包括如下步骤:

17、下底片的制备:

18、a1、取第一衬底,所述第一衬底包括相背的第一表面和第二表面,将所述第一衬底的第一表面清洁后,在所述第一衬底的第一表面上沉积第一超导薄膜;

19、a2、在所述第一超导薄膜上制备第一金属围墙和第一电路层,所述第一金属围墙设置为环绕所述第一衬底的第一表面的边缘一周;

20、上顶片的制备:

21、b1、取第二衬底,所述第二衬底包括相背的第一表面和第二表面,将所述第二衬底的第一表面清洁后,在所述第二衬底的第一表面上沉积第二超导薄膜;

22、b2、首先,在所述第二超导薄膜上制备第二金属围墙,所述第二金属围墙设置为环绕所述第二衬底的表面的边缘一周;其次,依次在所述第二超导薄膜上制备第二电路层和约瑟夫森结,所述二金属柱环绕于所述第二电路层和所述约瑟夫森结的外侧;

23、器件的制备:

24、于真空环境下,将所述下底片和所述上顶片分别安装到倒装焊设备上,使所述下底片和所述上顶片平行且所述第一金属围墙与所述第二金属围墙一一对应设置,利用倒装焊设备对所述下底片和所述上顶片施加压力,使所述第一金属围墙与所述第二金属围墙焊接连接并形成预设的高度,以便于实现所述下底片和所述上顶片的键合连接,预设的高度可以为20μm、15μm、10μm、5μm、2μm等等。

25、基于上述方案,携带比特器件的上顶片在制作的过程中,采用先制备金属柱,在制备电路结构及约瑟夫森结的制备流程,避免了后制备金属柱对量子比特组件的影响,提高了量子比特器件的比特性能。

26、作为本技术进一步的改进,步骤a1中:在所述第一衬底的第一表面上沉积第一超导薄膜之前还包括:在所述第一衬底的第一表面上制备第一凹槽,所述第一金属围墙设置为环绕于所述第一凹槽的外侧;和/或;

27、步骤b1中,在所述第二衬底的第一表面上沉积第二超导薄膜之前还包括:在所述第二衬底的第一表面上制备第二凹槽,所述第二金属围墙设置为环绕于所述第二凹槽的外侧。

28、基于上述方案,第一凹槽和/或第二凹槽的设置,有利于容纳电路结构,此外还能降低对金属围墙的高度要求。

29、作为本技术进一步的改进,步骤a1中:在所述第一衬底的第一表面上沉积第一超导薄膜之前还包括:在所述第一衬底的第一表面上制备第三凹槽,所述第一金属围墙坐落于所述第三凹槽内;

30、步骤b1中,在所述第二衬底的第一表面上沉积第二超导薄膜之前还包括:在所述第二衬底的第一表面上制备第四凹槽,所述第二金属围墙坐落于所述第四凹槽内。

31、基于上述方案,倒装焊压焊的过程中,受第三凹槽、第四凹槽的影响,金属柱能被限定到第三凹槽、第四凹槽内,实现对金属围墙压缩高度及占位面积的精确控制。

32、作为本技术进一步的改进,步骤a1中:在所述第一衬底的第一表面上沉积第一超导薄膜之前还包括:在所述第一衬底上制备tsv通孔,所述第一金属围墙设置为环绕于所述tsv通孔的外侧,并用超导材料填充所述tsv通孔。

33、作为本技术进一步的改进,下底片的制备中,还包括步骤a3:将所述第一衬底的第二表面清洁后,在所述第一衬底的第二表面上沉积第三超导薄膜,在所述第三超导薄膜上制备第三电路层。

34、作为本技术进一步的改进,清洁所述衬底表面的方法可以如下:将所述第一衬底和第二衬底浸泡于溶剂中,超声清理,超声清理结束后以氮气吹淋所述第一衬底和第二衬底;优选地,所述溶剂为丙酮或异丙醇;优选地,所述超声的功率为50~1000w,更优选为90w;优选地,所述超声的时间为1~30分钟,更优选为10分钟;或;将所述第一衬底和第二衬底浸泡于缓冲氧化物刻蚀液(boe)中浸泡,冲洗,烘干等。

35、作为本技术进一步的改进,沉积所述第一超导薄膜、所述第二超导薄膜或所述第一超导薄膜的工艺可以为但不仅仅限于磁控溅射、电子束蒸发等中的一种或多种。

36、作为本技术进一步的改进,制备第一凹槽、第二凹槽、第三凹槽、第四凹槽和tsv通孔的工艺可以为但不仅仅限于光刻工艺、刻蚀工艺、深硅刻蚀工艺等中的一种或多种。

37、作为本技术进一步的改进,制备第一电路层、第二电路层、第三电路层、约瑟夫森结的工艺可以为但不仅仅限于光刻工艺、刻蚀工艺、薄膜沉积工艺、氧气氧化工艺、去胶工艺、清洗工艺等中的一种或多种。

38、作为本技术进一步的改进,填充所述tsv通孔的工艺可以为但不仅仅限于金属熔融填充、pvd、cvd、ald、电镀等中的一种或多种。

39、作为本技术进一步的改进,第一凹槽、第二凹槽、第三凹槽、第四凹槽的深度可以根据具体电路结构进行调整,如:第一凹槽的深度可以为2μm~12μm,第二凹槽的深度可以为2μm~12μm,第三凹槽的深度可以为0.5μm~5.5μm,第四凹槽的深度可以为0.5μm~5.5μm。

40、作为本技术进一步的改进,第一超导薄膜、第二超导薄膜、第三超导薄膜的厚度也可以根据电路结构进行调整,如:第一超导薄膜的厚度可以为50nm~500nm,第二超导薄膜的厚度可以为50nm~500nm,第三超导薄膜的厚度可以为50nm~500nm,等等。

41、作为本技术进一步的改进,金属围墙的形状及高度均可以根据电路结构进行调整,如:金属围墙的形状可以为但不仅仅限于圆形、正方形、长方形等,金属围墙的高度可以为0.5μm~20μm等。

42、作为本技术进一步的改进,制备第一金属围墙和/或第二金属围墙的工艺可以为但不仅仅限于磁控溅射、电子束蒸发等。

43、本技术的有益效果在于:

44、本技术提供了一种包绕式超导量子倒装芯片及其制备方法,包绕式超导量子倒装芯片包括层叠设置的第一衬底、第一超导薄膜、金属围墙、第二超导薄膜、第二衬底,所述第一超导薄膜包括第一电路层;所述第二超导薄膜包括第二电路层和约瑟夫森结;所述金属围墙环绕于所述第一电路层、所述第二电路层以及所述约瑟夫森结的外围。本技术中,将大量排布在电路区内的金属围墙调整到电路外围,可以先制备金属围墙再制备电路层,有效的避免了制备金属柱对比特性能的影响。

- 还没有人留言评论。精彩留言会获得点赞!