用于正交延迟时钟生成的系统及方法与流程

本公开大体上涉及锁相环(pll)系统,包含(但不限于)用于在pll设计中生成时钟信号的系统及方法。

背景技术:

1、锁相环(pll)可用于各种系统,例如(举例来说)通信系统、数据处理及仪器以及测试设备。pll电路系统可与其它集成电路或装置一起工作以提供或促进(例如)用于各种处理操作的定时同步。pll可取决于其用途在设计及功能上变动。

技术实现思路

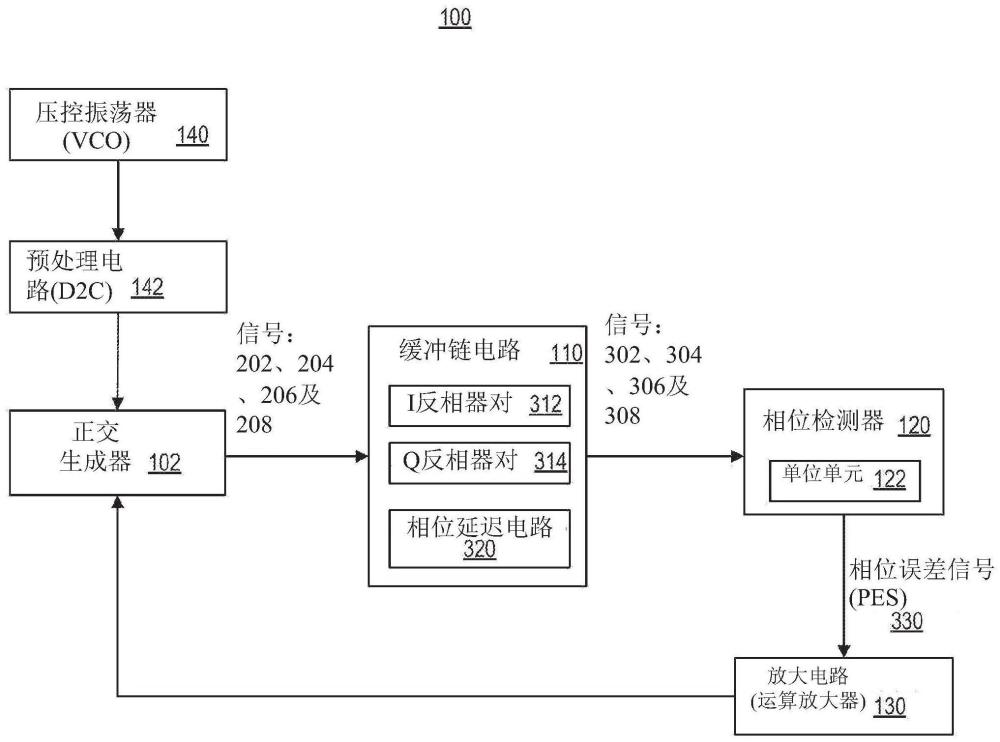

1、本公开涉及一种用于提供正交延迟高速时钟生成的解决方案。当设计具有在约40到50ghz或更高下操作的压控振荡器(vco)的pll以提供约160到200gbps或更高的数据速率时,电路系统的噪声、寄生电容及窄调谐范围(例如正交延迟设计)可能使得难以在大于34ghz的频率下操作vco,将数据速率限制在约136gbps。为了克服此挑战,本解决方案提供具有成对同相反相器及正交反相器的缓冲链电路,其中相位延迟电路位于缓冲链的同相侧上。本解决方案提供具有用于处理缓冲链输出信号的多个单元的相位检测器,其中每一单元可包含一或多个(例如一对)p型金属氧化物半导体(pmos)晶体管,所述晶体管使栅极系结到电压源电源(vss),也称为接地或零电压。为此,本解决方案允许pll的vco在约40到50ghz或更高频率下操作,且提供约160到200gbps或更高的数据速率,允许约20%的频率调谐范围及改进的性能,同时节省能量。

2、在一些方面,本解决方案涉及一种电路系统或系统。所述电路系统或所述系统可包含第一多对反相器,其经配置以根据第一时钟信号输出同相信号(i)。所述第一时钟信号可作为第一输入被接收。所述第一多对反相器可经配置以根据第二时钟信号输出反相i信号(反相i)。所述第二时钟信号可作为第二输入被接收。所述第一多对反相器中的每一对可由第一电路并联耦合以控制所述i与所述反相i之间的相位延迟。所述电路系统或所述系统可包含第二多对反相器,其经配置以根据第三时钟信号输出正交信号(q)。所述第三时钟信号可作为第三输入被接收。所述第二多对反相器可根据第四时钟信号输出反相q信号(反相q)。所述第四时钟信号可作为第四输入被接收。所述电路系统或所述系统可包含第二电路,所述第二电路包括多个单元。所述多个单元中的每一者可经配置以接收所述i信号、所述反相i信号、所述q信号或所述反相q信号中的至少一者。每一单元可包含至少一或多个晶体管,所述晶体管使栅极连接到接地。

3、所述第一多对反相器可包含以第一串联连接以提供所述i的第一组四个反相器。所述第一多对反相器可包含以第二串联连接以提供所述反相i的第二组四个反相器。所述第二多对反相器可包含以第三串联连接以提供所述q的第一组三个反相器及以第四串联连接以提供所述反相q的第二组三个反相器。

4、用以控制所述相位延迟的所述第一电路可包含反向偏压定向的变容二极管或电容器及二极管的组合中的一者。用以控制所述相位延迟的所述第一电路包含第一电容器,所述第一电容器连接到正向偏压定向的第一二极管,所述第一二极管连接到反向偏压定向的第二二极管,所述第二二极管连接到第二电容器。

5、所述电路系统或所述系统可包含所述第一多对反相器中的第一对中的第一反相器。所述第一反相器可包含连接到所述第一电容器的第一输出且配置在以第一串联以提供所述i的第一组反相器中。所述电路系统或所述系统可包含所述第一多对反相器中的所述第一对中的第二反相器。所述第二反相器可包含连接到所述第二电容器的第二输出且配置在以第二串联连接以提供所述反相i的第二组反相器中。

6、所述第二电路的每一单元的所述至少一或多个晶体管可包含两个p沟道金属氧化物半导体(pmos)晶体管。所述两个pmos晶体管中的每一者可经配置以在三极管区中操作。所述多个单元中的每一单元可包含第一n沟道金属氧化物半导体(nmos)晶体管,其使所述第一nmos晶体管的漏极连接到所述两个pmos晶体管中的第一pmos晶体管的漏极且使所述第一nmos晶体管的栅极耦合到所述两个pmos晶体管中的第二pmos晶体管的源极。所述多个单元中的每一单元可包含第二nmos晶体管,其使所述第二nmos晶体管的漏极耦合到所述第二pmos晶体管的漏极且使所述第二nmos晶体管的栅极耦合到所述第一pmos晶体管的源极。

7、所述第二电路的所述多个单元可包含第一单元、第二单元、第三单元及第四单元,其经配置使得所述第一单元的所述第一pmos晶体管的源极与所述第四单元的所述第二pmos晶体管的源极连接且所述第一单元的所述第二pmos晶体管的源极与所述第二单元的所述第一pmos晶体管的源极连接。所述多个单元还可包含所述第三单元的所述第一pmos晶体管的源极,所述源极与所述第二单元的所述第二pmos晶体管的源极及所述第三单元的所述第二pmos晶体管的源极连接,所述第三单元的所述第二pmos晶体管的所述源极与所述第四单元的所述第一pmos晶体管的源极连接。

8、所述电路系统或所述系统可包含锁相环(pll)的正交生成器。所述正交生成器可包含电感器以提供所述第一时钟信号、所述第二时钟信号、所述第三时钟信号及所述第四时钟信号作为输出。所述第一多对及所述第二多对可为锁相环(pll)的缓冲链电路的部分。所述缓冲链电路可经配置以依40千兆赫与50千兆赫之间的频率向所述pll的相位检测器提供所述i、所述反相i、所述q及所述反相q中的至少一者。

9、在一些方面,本解决方案涉及一种方法,例如一种用于提供正交延迟高速时钟生成的方法。所述方法可包含第一多对反相器根据作为第一输入被接收的第一时钟信号提供同相信号(i)作为输出。所述方法可包含所述第一多对反相器根据作为第二输入被接收的第二时钟信号提供反相i信号(反相i)作为输出。所述第一多对反相器中的每一对可由第一电路并联耦合以控制所述i与所述反相i之间的相位延迟。所述方法可包含由第二多对反相器根据作为第三输入被接收的第三时钟信号提供正交信号(q)作为输出。所述方法可包含由所述第二多对反相器根据作为第四输入被接收的第四时钟信号提供反相q信号(反相q)作为输出。所述方法可包含由第二电路的多个单元接收所述反相i信号、所述q信号及所述反相q信号以产生输出。所述多个单元中的每一者可经配置以接收所述i信号、所述反相i信号、所述q信号或所述反相q信号中的至少一者且包含至少一或多个晶体管,所述晶体管使栅极连接到接地。

10、所述方法可包含所述第一多对反相器中的第一组四个反相器提供所述i信号。所述第一组四个反相器可以第一串联连接。所述方法可包含所述第一多对反相器中的第二组四个反相器提供所述反相i信号。所述第二组四个反相器以第二串联连接。所述方法可包含所述第二多对反相器中的第一组三个反相器提供所述q。所述第一组三个反相器可以第三串联连接。所述方法可包含所述第二多对反相器中的第二组三个反相器提供所述反相q。所述第二组三个反相器可以第四串联连接。

11、所述方法可包含用以控制所述相位延迟的所述第一电路包含第一电容器,所述第一电容器连接到正向偏压定向的第一二极管,所述第一二极管连接到反向偏压定向的第二二极管,所述第二二极管连接到第二电容器。所述方法可包含所述第一多对反相器包含所述第一多对中的第一对中的第一反相器。所述第一反相器可包含连接到所述第一电容器的第一输出且配置在以第一串联连接以提供所述i的第一组反相器中。所述方法可包含所述第一多对反相器中的所述第一对中的第二反相器。所述第二反相器可包含连接到所述第二电容器的第二输出且配置在以第二串联连接以提供所述反相i的第二组反相器中。

12、所述第二电路的每一单元的所述至少一或多个晶体管可包含两个p沟道金属氧化物半导体(pmos)晶体管,所述两个pmos晶体管中的每一者经配置以在三极管区中操作。所述多个单元中的每一单元可包含第一n沟道金属氧化物半导体(nmos)晶体管,其使所述第一nmos晶体管的漏极连接到所述两个pmos晶体管中的第一pmos晶体管的漏极且使所述第一nmos晶体管的栅极耦合到所述两个pmos晶体管中的第二pmos晶体管的源极。所述多个单元中的每一单元可包含第二nmos晶体管,其使所述第二nmos晶体管的漏极耦合到所述第二pmos晶体管的漏极且使所述第二nmos晶体管的栅极耦合到所述第一pmos晶体管的源极。

13、所述第二电路的所述多个单元可包含第一单元、第二单元、第三单元及第四单元,其经配置使得所述第一单元的所述第一pmos晶体管的源极与所述第四单元的所述第二pmos晶体管的源极连接且所述第一单元的所述第二pmos晶体管的源极与所述第二单元的所述第一pmos晶体管的源极连接。所述第二电路的所述多个单元可各自包含所述第三单元的所述第一pmos晶体管的源极,所述源极与所述第二单元的所述第二pmos晶体管的源极及所述第三单元的所述第二pmos晶体管的源极连接,所述第三单元的所述第二pmos晶体管的所述源极与所述第四单元的所述第一pmos晶体管的源极连接。

14、所述方法可包含锁相环(pll)的正交生成器包括电感器且提供所述第一时钟信号、所述第二时钟信号、所述第三时钟信号及所述第四时钟信号作为输出。所述第一多对及所述第二多对可为锁相环(pll)的缓冲链电路的部分。所述缓冲链电路可经配置以依40千兆赫与50千兆赫之间的频率向所述pll的相位检测器提供所述i、所述反相i、所述q及所述反相q中的至少一者。

15、在一些方面,本解决方案可涉及一种系统。所述系统可包含用于提供时钟信号的电路系统。所述电路系统可包含压控振荡器,所述压控振荡器利用电感器来生成第一时钟信号、第二时钟信号、第三时钟信号及第四时钟信号。所述电路系统可包含缓冲链电路。所述缓冲链电路可包含第一多对反相器,所述第一多对反相器经配置以根据作为第一输入被接收的第一时钟信号输出同相信号(i)且根据作为第二输入被接收的第二时钟信号输出反相i信号(反相i)。所述第一多对反相器中的每一对可由第一电路并联耦合以控制所述i与所述反相i之间的相位延迟。所述电路系统可包含第二多对反相器,所述第二多对反相器经配置以根据作为第三输入被接收的第三时钟信号输出正交信号(q)且根据作为第四输入被接收的第四时钟信号输出反相q信号(反相q)。所述电路系统可包含相位检测器,所述相位检测器包括多个单元,所述多个单元中的每一者经配置以接收所述i信号、所述反相i信号、所述q信号或所述反相q信号中的至少一者。每一单元可包含至少一或多个晶体管,所述晶体管使栅极连接到接地。

16、所述系统可包含所述第一多对反相器,所述第一多对反相器包含以第一串联连接以提供所述i的第一组四个反相器及以第二串联连接以提供所述反相i的第二组四个反相器。所述系统可包含所述第二多对反相器,所述第二多对反相器包含以第三串联连接以提供所述q的第一组三个反相器及以第四串联连接以提供所述反相q的第二组三个反相器。用以控制所述相位延迟的所述第一电路可包含反向偏压定向的变容二极管或电容器及二极管的组合中的一者。

- 还没有人留言评论。精彩留言会获得点赞!