本技术涉及时钟,特别涉及一种频率选择电路、时钟产生电路及处理器。

背景技术:

1、中央处理器(central processing unit,cpu)中的时钟电路一般包括两个锁相环(phase locked loop,pll)电路。其中一个pll电路能够提供总线访问存储器使用的时钟,另一个pll电路则可以用于提供cpu的核心时钟以及其他调试(debug)时钟等。

2、通常,pll电路提供的cpu的核心时钟的频率为固定频率,导致cpu工作时的灵活性较低。

技术实现思路

1、本技术提供了一种频率选择电路、时钟产生电路及处理器,可以解决cpu的核心时钟的频率为固定频率,导致cpu工作时的灵活性较低的技术问题。所述技术方案如下:

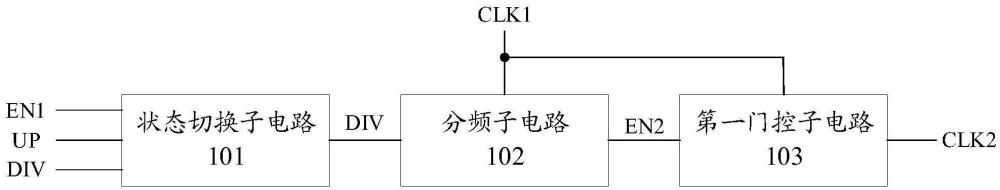

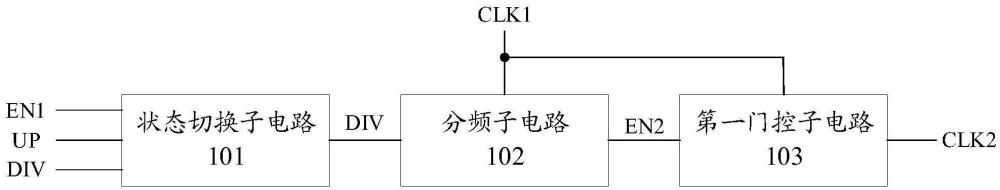

2、第一方面,提供了一种频率选择电路,所述频率选择电路包括:状态切换子电路,分频子电路,第一门控子电路;

3、所述状态切换子电路,用于接收第一使能信号、时钟更新信号和分频值,并用于基于所述第一使能信号和所述时钟更新信号,将所述分频值传输至所述分频子电路;

4、所述分频子电路,用于接收主时钟信号,基于所述主时钟信号对所述分频值进行累加,在所述分频值的累加结果未达到目标值时,向所述第一门控子电路输出具有第一电平的第二使能信号,在所述累加结果达到目标值时,向所述第一门控子电路输出具有第二电平的第二使能信号,并重新对所述分频值进行累加;

5、所述第一门控子电路,用于接收所述主时钟信号,并用于在所述第二使能信号为第二电平时,向处理器中的处理器核输出所述主时钟信号,在所述第二使能信号为第一电平时,向所述处理器核输出无效电平的信号。

6、可选地,所述状态切换子电路,还用于基于所述第一使能信号和所述时钟更新信号,向所述分频子电路依次输出第一选择信号和第二选择信号;

7、所述分频子电路包括:多路选择器和加法器,所述加法器的第一输入端用于接收所述分频值;

8、所述多路选择器用于:在所述第一选择信号的控制下,将所述加法器的第二输入端清零,并向所述第一门控子电路输出具有第一电平的第二使能信号,以及在所述第二选择信号的控制下,将所述加法器输出的和数传输至所述加法器的第二输入端,并将所述加法器输出的进位作为所述第二使能信号输出至所述第一门控子电路。

9、可选地,所述频率选择电路还包括:更新子电路;

10、所述更新子电路分别与所述分频子电路和所述第一门控子电路连接,所述更新子电路用于接收所述第一使能信号,并用于在所述第一使能信号为第二电平时,向所述第一门控子电路输出来自所述分频子电路的所述第二使能信号,在所述第一使能信号为第一电平时,向所述第一门控子电路输出具有第二电平的信号。

11、可选地,所述频率选择电路还可以包括:第二门控子电路,第一同步子电路和第二同步子电路;

12、所述第二门控子电路,用于基于所述第一使能信号,分别向第一同步子电路、所述第二同步子电路和所述状态切换子电路输出所述主时钟信号;

13、所述第一同步子电路,用于基于所述主时钟信号,对所述时钟更新信号进行同步,并将同步后的所述时钟更新信号传输至所述状态切换子电路;

14、所述第二同步子电路,用于基于所述主时钟信号,对所述多路选择器输出的信号进行同步后,传输至所述加法器的第二输入端。

15、可选地,所述频率选择电路还包括:第三同步子电路、第四同步子电路和第一或门;

16、所述第三同步子电路用于基于所述主时钟信号,对所述第一使能信号进行同步,并将同步后的所述第一使能信号传输至所述第二门控子电路和所述第四同步子电路;

17、所述第四同步子电路用于基于所述主时钟信号,对所述第一使能信号进行同步,并将同步后的所述第一使能信号传输至所述状态切换子电路;

18、所述第一或门的第一输入端用于接收测试模式信号,所述第一或门的第二输入端与所述第三同步子电路的输出端连接,所述第一或门的输出端与所述第二门控子电路的使能端连接。

19、可选地,所述频率选择电路还包括:第五同步子电路,第二或门,第三或门;

20、所述第五同步子电路用于基于所述主时钟信号,对所述第二使能信号进行同步,并将同步后的所述第二使能信号传输至所述第二或门的第一输入端;

21、所述第二或门的第二输入端为反相输入端,所述反相输入端用于接收所述第一使能信号,所述第二或门的输出端与所述第三或门的第一输入端连接;

22、所述第三或门的第二输入端用于接收测试模式信号,所述第三或门的输出端与所述第一门控子电路的使能端连接。

23、第二方面,提供了一种时钟产生电路,所述时钟产生电路包括:第一锁相环,以及如上述第一方面所述的频率选择电路;

24、其中,所述第一锁相环用于为所述频率选择电路提供第一主时钟信号。

25、可选地,所述时钟产生电路还包括:第一门控电路,第一时钟切换电路,以及至少一个第一时钟电路组,每个所述第一时钟电路组包括一个第二门控电路和一个第一时钟控制器;

26、其中,所述第一门控电路连接在所述第一锁相环和所述频率选择电路之间,所述第一门控电路用于基于第一门控使能信号,将所述第一锁相环输出的所述第一主时钟信号传输至所述频率选择电路;

27、所述第一时钟切换电路分别与所述频率选择电路和所述至少一个第一时钟电路组连接,用于基于接收到的第一选择信号,将晶振时钟信号或者所述分频时钟信号输出至所述至少一个第一时钟电路组;

28、所述至少一个第一时钟电路组中的每个第一时钟电路组,用于向处理器中的一个处理器核提供核心时钟信号。

29、可选地,所述时钟产生电路还包括:第三门控电路,第二时钟切换电路,以及至少一个第二时钟电路组,每个所述第二时钟电路组包括一个第四门控电路和一个第二时钟控制器;

30、所述第三门控电路连接在所述第一锁相环和所述第二时钟切换电路之间,所述第三门控电路用于基于第二门控使能信号,将所述第一锁相环输出的第二主时钟信号传输至所述第二时钟切换电路;

31、所述第二时钟切换电路与所述至少一个第二时钟电路组连接,用于基于接收到的第二选择信号,将所述晶振时钟信号或者所述第二主时钟信号输出至所述至少一个第二时钟电路组;

32、所述至少一个第二时钟电路组中的每个第二时钟电路组,用于输出一个第一类时钟信号。

33、可选地,所述时钟产生电路还包括:第二锁相环,第五门控电路,第三时钟切换电路,第六门控电路和第三时钟控制器;

34、所述第二锁相环用于输出第三主时钟信号;

35、所述第五门控电路连接在所述第二锁相环和所述第三时钟切换电路之间,所述第五门控电路用于基于第三门控使能信号,向所述第三时钟切换电路输出所述第三主时钟信号;

36、所述第三时钟切换电路还与所述第六门控电路连接,用于基于接收到的第三选择信号,将所述晶振时钟信号或者所述第三主时钟信号输出至所述第六门控电路;

37、所述第六门控电路和所述第三时钟控制器,用于输出第二类时钟信号。

38、可选地,所述时钟产生电路还包括:第一扩频调制器和第二扩频调制器;

39、所述第一扩频调制器与所述第一锁相环连接,用于调制所述第一锁相环;

40、所述第二扩频调制器与所述第二锁相环连接,用于调制所述第二锁相环。

41、第三方面,提供了一种处理器,所述处理器包括:至少一个处理器核,以及如上述第二方面所述的时钟产生电路;其中,所述时钟产生电路用于为所述至少一个处理器核提供时钟信号。

42、本技术提供的技术方案带来的有益效果至少包括:

43、本技术提供了一种频率选择电路、时钟产生电路及处理器。该频率选择电路中的分频子电路能够基于主时钟信号对分频值进行累加,并能够在该分频值的累加结果为目标值时,向第一门控子电路输出具有第二电平的第二使能信号,以使第一门控子电路向处理器核输出该主时钟信号。在累加结果不为该目标值时,分频子电路向第一门控子电路输出的第二使能信号为第一电平,以使第一门控子电路向处理器核输出无效电平的信号。由此可知,该频率选择电路最终输出的分频时钟信号的频率低于主时钟信号的频率,且该分频时钟信号的频率能基于分频值灵活调节。由此,实现了对处理器核的时钟频率的灵活调节,从而有效提高了处理器工作时的灵活性,且显著降低了处理器的功耗。