半浮栅多晶硅栅的制造方法与流程

本发明涉及一种半导体集成电路的制造方法,特别是涉及一种半浮栅(semi-floating gate)多晶硅栅(poly gate)的制造方法。

背景技术:

1、电容是传统dram发展的瓶颈,半浮栅晶体管不使用电容,能和标准逻辑工艺集成且更容易微缩,是一种有潜力的dram。对u型沟槽(u-trench)中半浮栅poly gate进行充放电可以实现器件逻辑1和0状态的转变,半浮栅poly gate通过半浮栅介质窗口(c-window)与半导体衬底材料如si直接接触形成pn结控制电荷进出

2、现有方法中,在存储单元区即阵列区(array)和逻辑区(logic)兼容的半浮栅工艺中,u-trench形成后生长栅氧化层(gate ox),随后半浮栅多晶硅(poly)第一次沉积(deposition,dep)填充u-trench,接着进行c-window刻蚀(etch,et)工艺刻蚀gate ox,在进行半浮栅poly第二次deposition实现半浮栅poly与si接触形成pn结,由于poly填充u-trench和c-window沟槽(trench)后,表面有较严重蝶形凹陷(dishing),需要通过poly化学机械研磨(cmp)将表面平坦化以消除dishing,最后通过无掩膜刻蚀(blanket et)工艺将array半浮栅poly厚度刻蚀到从而得到最终半浮栅poly gate

3、现有方法具有如下工艺风险:

4、在一些具体工艺中,形成u-trench时用于保护存储单元区的场氧的硬质掩膜层(hm)即u-trench hm的厚度达半浮栅poly第一次deposition后,array区域的poly厚度将会被u-trench hm抬高到会显著增大c-window et刻蚀深宽比,从而增加刻蚀难度。

5、同时,半浮栅poly第二次deposition,需要填深度为和宽度为40nm的trench,由于高深宽比,容易形成空洞(void),从而填充难度大且容易出现填充缺陷。

6、由于在逻辑/array集成工艺中,需要保护logic区域,logic区域的台阶(step)高度(height)要高于array区域。在poly cmp过程中,cmp停止在(stop on)logic区域的sin层上,由于step height的存在,array区的表面上总是有氧化层(ox)剩余(remain),即使有过研磨(over polish),array区上ox膜厚的波动范围(range)也很大,在blanket et后,半浮栅poly厚度的range也会比较大,而半浮栅poly gate厚度要求做到厚度很难控制,wafer面内均匀性也很难保证

技术实现思路

1、本发明所要解决的技术问题是提供一种半浮栅多晶硅栅的制造方法,能降低半浮栅介质窗口的深宽比从而能降低半浮栅介质窗口的刻蚀和填充的难度,还能改善半浮栅多晶硅栅的厚度的控制难度并提高半浮栅多晶硅栅的厚度的控制精度和面内均匀性。

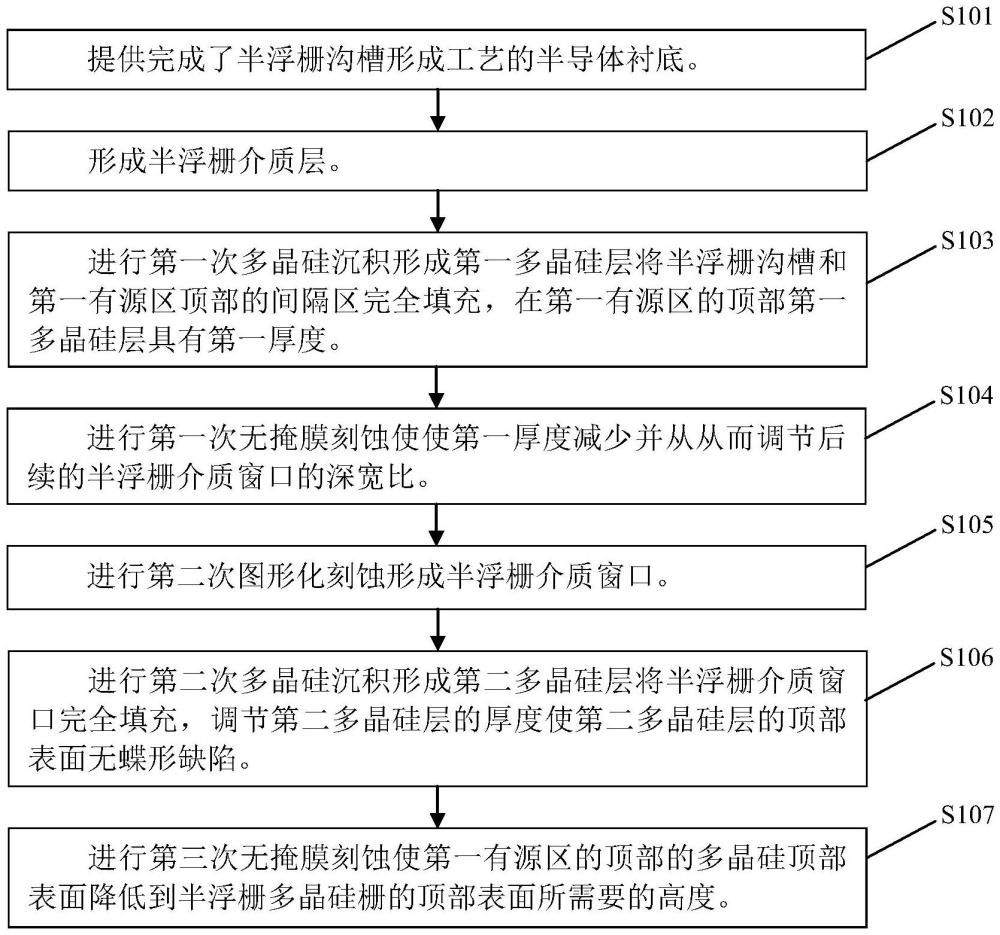

2、为解决上述技术问题,本发明提供的半浮栅多晶硅栅的制造方法包括步骤:

3、提供完成了半浮栅沟槽形成工艺的半导体衬底,在存储单元区中,所述半导体衬底上形成有由场氧定义的第一有源区,所述第一有源区平行排列,在所述场氧顶部形成有硬质掩膜层,所述半浮栅沟槽形成于所述第一有源区的选定区域中。

4、形成半浮栅介质层,所述半浮栅介质层形成于所述半浮栅沟槽的内侧表面并延伸到所述半浮栅沟槽外的所述第一有源区的表面。

5、进行第一次多晶硅沉积形成第一多晶硅层,所述第一多晶硅层将所述半浮栅沟槽完全填充以及将所述场氧之间的所述第一有源区顶部的间隔区完全填充并延伸到所述场氧的顶部表面之上;在所述第一有源区的顶部所述第一多晶硅层具有第一厚度,在所述场氧的顶部所述第一多晶硅层具有第二厚度,所述第二厚度小于所述第一厚度。

6、进行第一次无掩膜刻蚀使所述第一多晶硅层的顶部表面降低并使所述第一厚度减少;通过减少所述第一厚度来调节后续的半浮栅介质窗口的深宽比,且将所述半浮栅介质窗口的深宽比调节到满足在后续的第二多晶硅沉积中实现对所述半浮栅介质窗口进行完全填充。

7、进行第二次图形化刻蚀形成半浮栅介质窗口;所述半浮栅介质窗口穿过所在区域的所述第一多晶硅层和所述半浮栅介质层并将底部的所述第一有源区的顶部表面露出。

8、进行第二次多晶硅沉积形成第二多晶硅层,所述第二多晶硅层将所述半浮栅介质窗口完全填充且延伸到所述半浮栅介质窗口外,调节所述第二多晶硅层的厚度使所述第二多晶硅层的顶部表面无蝶形缺陷。

9、进行第三次无掩膜刻蚀使所述第一有源区的顶部的所述第二多晶硅层和所述第一多晶硅层的叠加层的顶部表面降低到半浮栅多晶硅栅的顶部表面所需要的高度。

10、进一步的改进是,所述半导体衬底包括硅衬底。

11、进一步的改进是,所述场氧包括浅沟槽隔离。

12、进一步的改进是,所述硬质掩膜层由氧化层或氮化层叠加而成。

13、进一步的改进是,所述半浮栅介质层包括内衬氧化层。

14、进一步的改进是,所述第二厚度为所述第一次多晶硅沉积的厚度,所述第一次多晶硅沉积完成后的所述第一厚度为所述第二厚度和所述硬质掩膜层的第三厚度的和。

15、所述第一次无掩膜刻蚀的厚度大于所述第二厚度;所述第一次无掩膜刻蚀完成后,所述硬质掩膜层顶部的所述第一多晶硅层被去除且所述硬质掩膜层的顶部表面和所述第一有源区顶部的所述第一多晶硅层的顶部表面相平。

16、进一步的改进是,所述半浮栅介质窗口的深宽比为1.6以下。

17、进一步的改进是,所述第二次多晶硅沉积的厚度的最大值达以上。

18、进一步的改进是,在所述半浮栅沟槽和所述半浮栅介质窗口外部,所述半浮栅多晶硅栅的顶部表面距离所述半浮栅介质层的顶部表面的厚度的最小值达以下。

19、进一步的改进是,所述半浮栅介质窗口的宽度的最小值达40nm以下。

20、进一步的改进是,所述第三次无掩膜刻蚀还将所述场氧顶部的所述第二多晶硅层去除且所述场氧顶部的所述硬质掩膜层的顶部表面和所述半浮栅多晶硅栅的顶部表面相平。

21、进一步的改进是,所述硬质掩膜层的厚度最大值达以上。

22、和现有技术中,第一次多晶硅沉积后直接进行半浮栅介质窗口的刻蚀和填充不同,本发明在第一次多晶硅沉积后,增加了第一次无掩膜刻蚀,第一次无掩膜刻蚀会使第一多晶硅层的厚度降低,其中位于第一有源区的顶部的第一多晶硅层的第一厚度降低后能调节后续形成的半浮栅介质窗口的深宽比,在使半浮栅介质窗口的深宽比调节到要求值的条件下,不仅能降低形成半浮栅介质窗口的第二次图形化刻蚀的工艺难度,还能保证第二次多晶硅沉积实现对半浮栅介质窗口的无缝隙的完全填充,所以本发明能降低半浮栅介质窗口的深宽比从而能降低半浮栅介质窗口的刻蚀和填充的难度。

23、本发明还能增加第二次多晶硅沉积的厚度,以使形成的第二多晶硅层的顶部表面无蝶形缺陷,这样就能取消现有方法中为了消除蝶形缺陷而引入的cmp工艺,不仅能降低工艺成本,还能消除cmp工艺引入后所带来的对半浮栅多晶硅栅的厚度控制的不利影响,最后能改善半浮栅多晶硅栅的厚度的控制难度并提高半浮栅多晶硅栅的厚度的控制精度和面内均匀性。

- 还没有人留言评论。精彩留言会获得点赞!