一种多栅控晶体管结构的高线性度低噪声放大器

本发明属于射频集成电路,具体涉及一种多栅控晶体管结构的高线性度低噪声放大器。

背景技术:

1、在快速发展的无线通信领域,cmos(互补金属氧化物半导体)工艺因其低成本、高集成度和可扩展性等优势,成为毫米波射频集成电路设计的首选。然而,随着通信系统向更高频率和更宽带宽的方向发展,cmos工艺下的毫米波宽带低噪声放大器设计面临诸多挑战。

2、毫米波宽带低噪声放大器需要在保持低噪声系数的同时,提供足够的增益和宽带宽,以适应多频段和多模式的通信需求。此外,高线性度是另一个关键指标,它确保放大器在处理大动态范围信号时,不会引入额外的非线性失真,这对于维持通信质量至关重要。在cmos工艺中,由于器件尺寸的缩小,寄生效应和工艺变异性对电路性能的影响变得更加显著,这增加了设计高线性度低噪声放大器的复杂性。

3、公开号为cn113630090a的专利申请文件,公开了一种基于无源balun的宽带高增益高线性度低噪声放大器,采用电阻反馈结构提高非线性性能,采用balun作为负载,拥有更高的线性度。然而电阻反馈结构会导致增益降低。

技术实现思路

1、为了克服上述现有技术的不足,本发明的目的在于提供一种多栅控晶体管结构的高线性度低噪声放大器,通过采用多栅控晶体管结构,结合宽带匹配、跨导增强等技术,能够使晶体管的非线性失真叠加相消,提升宽带低噪声放大器线性度,且不会使功耗和增益性能恶化。

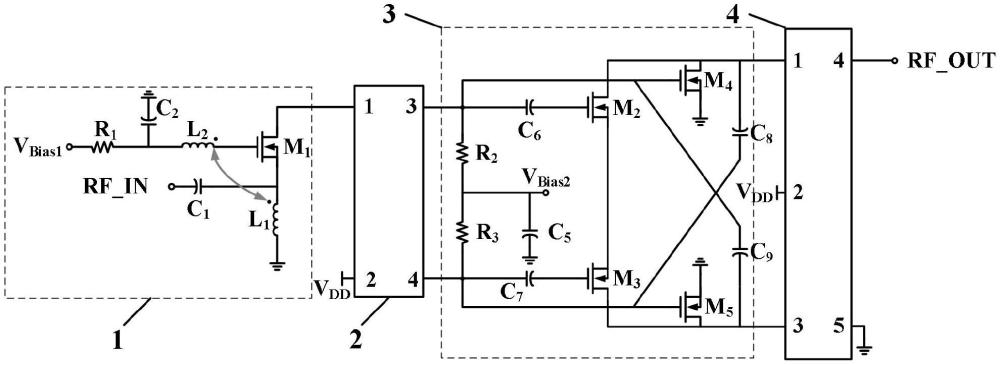

2、一种多栅控晶体管结构的高线性度低噪声放大器,包括:

3、输入增益级电路1,采用跨导增强的共栅极放大器结构,一端连接输入单端射频信号,另一端连接级间匹配磁耦合谐振器2,用于输入并放大单端射频信号,并将单端射频信号传递给级间匹配磁耦合谐振器2;

4、级间匹配磁耦合谐振器2,采用基于对称变压器的电感耦合谐振器结构,一端连接单端的输入增益级电路1,另一端连接差分的线性度提升电路3,用于接收输入增益级电路1输出的单端射频信号,并将单端射频信号转换为差分信号;

5、线性度提升电路3,采用多栅控晶体管结构,一端连接级间匹配磁耦合谐振器2的差分输出端,另一端连接输出匹配磁耦合谐振器4的差分输入端,用于接收级间匹配磁耦合谐振器2输出的差分信号并放大;

6、输出匹配磁耦合谐振器4,采用基于对称变压器的电感耦合谐振器结构,一端连接线性度提升电路3的差分输出端,另一端单端输出射频信号,用于接收线性度提升电路3输出的差分信号,并将差分信号转换为单端信号输出。

7、输入增益级电路1包括第一电容c1、第二电容c2、第一电感l1、第二电感l2、第一电阻r1和第一晶体管m1;所述第一电容c1的第一端连接射频信号输入端口,第一电容c1的第二端连接第一电感l1的第一端、第一晶体管m1的源端和第一晶体管m1的体端;所述第一电感l1的第二端接地;所述第一晶体管m1的栅端连接第二电感l2的第二端,第一晶体管m1的漏端连接级间匹配磁耦合谐振器2的1端口;所述第二电感l2的第一端连接第二电容c2的第一端和第一电阻r1的第二端;所述第二电容c2的第二端接地;所述第一电阻r1的第一端连接偏置电压vbias1。

8、所述级间匹配磁耦合谐振器2包括第三电容c3、第四电容c4、第三电感l3和第四电感l4;所述第三电容c3的第一端连接第三电感l3的第一端和级间匹配磁耦合谐振器2的1端口,第三电容c3的第二端连接第三电感l3的第二端和级间匹配磁耦合谐振器2的2端口;第四电容c4的第一端连接第四电感l4的第一端和级间匹配磁耦合谐振器2的3端口,第四电容c4的第二端连接第四电感l4的第二端和级间匹配磁耦合谐振器2的4端口;所述级间匹配磁耦合谐振器2的2端口连接电源vdd。

9、所述线性度提升电路3包括第二电阻r2、第三电阻r3、第五电容c5、第六电容c6、第七电容c7、第八电容c8、第九电容c9、第二晶体管m2、第三晶体管m3、第四晶体管m4和第五晶体管m5;所述第二电阻r2的第一端连接级间匹配磁耦合谐振器2的3端口,该节点定义为第一节点,第二电阻r2的第二端连接第三电阻r3的第二端、第五电容c5的第一端和偏置电压vbias2;所述第三电阻r3的第一端连接级间匹配磁耦合谐振器2的4端口,该节点定义为第二节点;所述第五电容c5的第二端接地;所述第六电容c6的第一端连接第一节点,第六电容c6的第二端连接第二晶体管m2的栅端;所述第七电容c7的第一端连接第二节点,第七电容c7的第二端连接第三晶体管m3的栅端;所述第八电容c8的第一端连接第二节点,第八电容c8的第二端连接第二晶体管m2的漏端、第四晶体管m4的漏端和输出匹配磁耦合谐振器4的1端口;所述第九电容c9的第一端连接第一节点,第九电容c9的第二端连接第三晶体管m3的漏端、第五晶体管m5的漏端和输出匹配磁耦合谐振器4的3端口;所述第二晶体管m2的源端连接第二晶体管m2的体端、第三晶体管m3的源端和第三晶体管m3的体端;所述第四晶体管m4的栅端连接第一节点,第四晶体管m4的源端接地,第四晶体管m4的体端接地;所述第五晶体管m5的栅端连接第二节点,第五晶体管m5的源端接地,第五晶体管m5的体端接地。

10、所述输出匹配磁耦合谐振器4包括第十电容c10、第十一电容c11、第五电感l5和第六电感l6;所述第十电容c10的第一端连接第五电感l5的第一端和输出匹配磁耦合谐振器4的1端口,第十电容c10的第二端连接第五电感l5的第二端和输出匹配磁耦合谐振器4的3端口;所述第五电感l5的抽头连接输出匹配磁耦合谐振器4的2端口;所述第十一电容c11的第一端连接第六电感l6的第一端和输出匹配磁耦合谐振器4的4端口,第十一电容c11的第二端连接第六电感l6的第二端和输出匹配磁耦合谐振器4的5端口;所述输出匹配磁耦合谐振器4的2端口接电源vdd,输出匹配磁耦合谐振器4的4端口接射频信号输出端,输出匹配磁耦合谐振器4的5端口接地。

11、所述输入增益级电路1中第一电感l1与第二电感l2相互耦合。

12、所述级间匹配磁耦合谐振器2中第三电感l3与第四电感l4相互耦合,构成基于对称变压器的电感耦合谐振器结构。

13、所述输出匹配磁耦合谐振器4中第五电感l5与第六电感l6相互耦合,构成基于对称变压器的电感耦合谐振器结构。

14、所述第一晶体管m1、第二晶体管m2、第三晶体管m3、第四晶体管m4和第五晶体管m5均为深n阱金属-氧化物-半导体场效应管。

15、与现有技术相比,本发明具有以下优点:

16、第一,本发明通过将输入增益级电路1采用跨导增强的共栅极放大器结构,使该电路完成宽带输入匹配的同时还能减小噪声。共栅极放大器具有良好的宽带匹配特性,结合跨导增强技术,即第一电感l1与第二电感l2相互耦合,它们之间的磁耦合提供了第一晶体管的栅极和源极之间的反相增益,有效地增强了第一晶体管的跨导,在整体增益不变的情况下消耗更少的偏置电流,较小的偏置电流意味着来自输入晶体管的通道噪声较小,因此优化了噪声性能。

17、第二,本发明通过将线性度提升电路3采用多栅控晶体管结构,使该技术提升线性度的同时不会增加功耗和降低增益。其中第四晶体管m4和第五晶体管m5组成了差分信号处理架构,能够减小偶数阶非线性引起的偶数阶失真,提升了电路的线性度;第二晶体管m2、第三晶体管m3为补偿晶体管,与差分信号处理架构构成并联关系,在适当偏置和尺寸下能够最小化三阶互调失真,进一步提升电路的线性度;此外,补偿晶体管m2和m3偏置在亚阈值区,差分信号处理晶体管m4和m5偏置在饱和区,因此该技术不会对功耗和增益造成影响。

18、第三,本发明通过将级间匹配磁耦合谐振器2和输出匹配磁耦合谐振器4采用基于对称变压器的电感耦合谐振器,实现了良好的宽带匹配效果。所述级间匹配磁耦合谐振器2中第三电感l3与第四电感l4相互耦合,输出匹配磁耦合谐振器4中第五电感l5与第六电感l6相互耦合,构成基于对称变压器的电感耦合谐振器结构,形成高阶匹配网络,变压器的加入提供了更多的设计自由度,同时只占据与单个电感相似的芯片面积,因此实现了良好的宽带匹配。

19、综上,本发明通过采用多栅控晶体管结构,结合宽带匹配、跨导增强等技术,在不增加直流功耗的前提下,使主、次级晶体管的谐波相互叠加而抵消,减小了电路中主要的非线性分量,改善了射频前端电路的动态范围,具有提升宽带低噪声放大器线性度的效果,且不会使功耗和增益性能恶化。

- 还没有人留言评论。精彩留言会获得点赞!