用于NR的LDPC基础图的使用的制作方法

本发明涉及与在网络(诸如nr网络)中使用ldpc基础图(base graph)有关的装置、方法和计算机程序产品。

背景技术:

1、本规范中使用的缩写的以下含义适用:

2、3gpp第三代合作伙伴计划

3、5g 第五代

4、bg 基础图

5、cb 码块

6、cbg 码块组

7、cbs 码块大小

8、crc 循环冗余校验

9、gf(2) 伽罗华域(2)

10、gnb 5g基站

11、ffs 有待进一步研究

12、ldpc 低密度奇偶校验

13、lte 长期演进

14、mcs 调制和编码方案

15、nr 新无线电

16、pc 极化码

17、pcm 奇偶校验矩阵

18、tb 运输块

19、tbs 传输块大小

20、ue 用户设备

21、urllc超可靠和低延迟通信

22、本发明的实施例涉及网络(诸如5g)中的信道编码优化,但不限于此。在下文中,通过参考参考文献[1]:r1-1711533“crc attachment for smaller tbs”nokia,alcatel-lucent shanghai bell,给出了有关较小tb的crc附接的一些考虑。

23、在ran1 nr ad-hoc#2会议中,商定两个ldpc基础图来支持5g中的数据信道。商定的其使用方式如下。

24、协议:

25、·基础图#1在以下情况下被用于相同tb的初始传输和后续重传:

26、–cbs>x或初始传输的码速率>y

27、·基础图#2在以下情况下被用于在以下情况下同一tb的初始传输和后续重传:

28、–cbs<=x并且初始传输的码速率<=y

29、·工作假设:x=2560并且y=0.67

30、–在pcm判决x是否可以被扩展到3840和/或y是否可以被扩展到0.75之后,有待进一步研究

31、将检查接收器在每种情况下如何知道初始传输的码速率,以及其如何被精确定义。

32、一些ue能力是否可能不需要实现两个基础图,有待进一步研究。

33、针对crc附接,ldpc码具有固有的错误检测能力,并且可以被用于减少crc开销。在ran1#88bis会议中,达成了关于当tb大于阈值时,针对tb进行附接24个crc比特的协议。然而,该阈值未被商定。特别是,ran1#88bis中的协议是,

34、协议:

35、·至少针对大于阈值的tb(例如,约512比特),tb级crc的比特数为:ltb,crc=24比特

36、·针对小于阈值的tb的ltb,crc值,以及阈值的值(不排除0)有待进一步讨论

37、·在码块(cb)分段后,如果tb被分段为2个或多个cb,则:

38、–cb级crc被应用,即crc比特个体地被附接到每个码块(如lte中一样)

39、–cb级crc的比特数为:0<lcb,crc<=24比特

40、·商定基础图后,考虑到固有的ldpc pc能力,将商定(多个)确切的lcb,crc

41、·针对包含2个或多个cb但不是tb的所有cb的码块组(cbg),

42、是否将任何附加crc比特附接到cbg有待进一步讨论

43、–将在(多个)lcb,crc的值判决后被判决

44、在mcs表上,lte使用5比特来指示控制有效载荷中的mcs。所有这些将使用turbo码,并且与mcs表和编码方案的使用无关。针对nr,如何利用该mcs字段需要更多讨论,因为所使用的基础图可以不同。

45、为了优化性能,在定义nr的其他细节时必须考虑两个基础图的使用。

技术实现思路

1、本发明的实施例解决了这种情形,并且旨在克服上述问题,以及优化编码信道上的性能。

2、根据本发明的第一方面,提供了一种装置,该装置包括至少一个处理器、包括计算机程序代码的至少一个存储器,并且该至少一个处理器与至少一个存储器和计算机程序代码一起被布置为,使装置至少执行:生成码块,该码块包括信息比特和奇偶校验比特,该奇偶校验比特通过对信息比特执行循环冗余校验而被生成;基于应用的线性纠错码基础图和/或基于信息比特的数目,来确定在生成码块中所使用的奇偶校验比特的数目;以及通过使用应用的线性纠错码基础图来对码块编码。

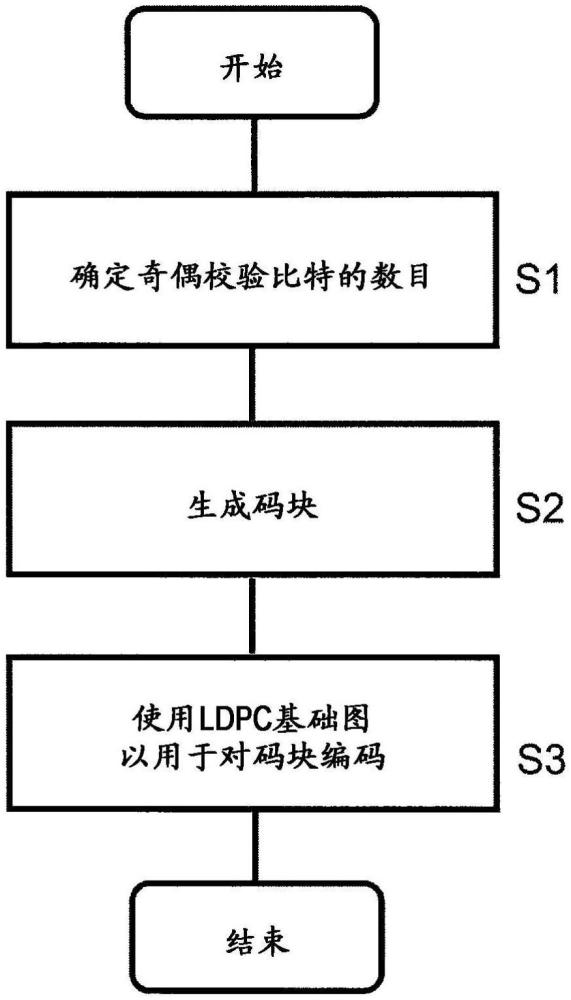

3、根据本发明的第二方面,提供了一种方法,该方法包括:

4、生成码块,所述码块包括信息比特和奇偶校验比特,奇偶校验比特通过对信息比特执行循环冗余校验而被生成,

5、基于应用的线性纠错码基础图和/或基于信息比特的数目,来确定在生成码块时所使用的奇偶校验比特的数目,以及

6、通过使用应用的线性纠错码基础图来对码块编码。

7、该第一方面和第二方面可以被修改如下:

8、例如,在生成码块中所使用的奇偶校验比特的数目可以基于信息比特的数目与阈值的比较而被确定,其中阈值可以通过由应用的线性纠错码基础图支持的最大码块大小而被定义。

9、应用的线性纠错码基础图可以从第一线性纠错码基础图和第二线性纠错码基础图中被选择,其中针对第二线性纠错码基础图生成码块中所使用的奇偶校验比特的数目可以小于针对第一线性纠错码基础图生成码块中所使用的奇偶校验比特的数目。

10、应用的线性纠错码基础图可以基于信息比特的数目而从第一线性纠错码基础图和第二线性纠错码基础图中被选择。

11、信息比特可以被包括在传输块中,并且当第二线性纠错码基础图被使用时,传输块大小的分段可以不被应用。

12、信息比特可以被包括在传输块中,并且当第二线性纠错码基础图被使用时,将传输块分段成至少两个码块可以被执行,其中在这种情况下,与在不应用分段的情况下相同,相同数目的奇偶校验比特可以被用于每个码块。

13、用于第一线性纠错码基础图的奇偶校验比特的数目可以是24,和/或用于第二线性纠错码基础图的奇偶校验比特的数目可以是16。

14、当基于应用的线性纠错码基础图来确定在生成码块中所使用的奇偶校验比特的数目时,可以引用基于应用的线性纠错码基础图的调制和编码方案表。

15、可以引用用于提供关于调制和编码方案的信息的调制和编码方案表,其中该表指定关于包括嵌套结构的调制和编码方案的信息,其中不同的调制和编码方案由相应的索引引用,其中索引由多个比特构成,并且指示与第二线性纠错码基础图有关的调制和编码方案的索引由若干比特指示,该若干比特少于指示与第一线性纠错码基础图有关的调制和编码方案的索引比特的数目。

16、当被用于指示与第二线性纠错码基础图有关的调制和编码方案的索引的比特数目被定义为y,并且被用于指示与第一线性纠错码基础图有关的调制和编码方案的索引的比特数目被定义为x时,指示与第二线性纠错码基础图有关的调制和编码方案的索引中的第一x-y前导比特可以被设置为0。

17、线性纠错码可以包括ldpc(低密度奇偶校验)码和/或极化码。

18、根据本发明的第三方面,提供了一种装置,该装置包括至少一个处理器、包括计算机程序代码的至少一个存储器,并且该至少一个处理器与至少一个存储器和计算机程序代码一起被布置为,使该装置至少执行:提供调制和编码方案表,该调制和编码方案表包括关于调制和编码方案的信息,其中该表指定关于包括嵌套结构的调制和编码方案的信息,其中不同的调制和编码方案由相应索引引用,其中索引由多个比特构成,并且指示与第二线性纠错码基础图有关的调制和编码方案的索引由若干比特指示,该若干比特少于指示与第一线性纠错码基础图有关的调制和编码方案的索引比特的数目。

19、根据本发明的第四方面,提供了一种方法,该方法包括:

20、提供包括关于调制和编码方案的信息的调制和编码方案表,

21、其中该表指定关于包括嵌套结构的调制和编码方案的信息,其中不同的调制和编码方案由相应索引引用,其中索引由多个比特构成,并且指示与第二线性纠错码基础图有关的调制和编码方案的索引由比特的数目所指示,该比特的数目小于指示与第一线性纠错码基础图有关的调制和编码方案的索引比特的数目。

22、第三方面和第四方面可以被修改如下:

23、当用于指示与第二线性纠错码基础图有关的调制和编码方案的索引的比特数目被定义为y,并且用于指示与第一线性纠错码基础图有关的调制和编码方案的索引的比特数目被定义为x时,指示与第二线性纠错码基础图有关的调制和编码方案的索引中的第一x-y前导比特可以被设置为0。

24、线性纠错码可以包括ldpc(低密度奇偶校验)码和/或极化码。

25、根据本发明的第五方面,提供了一种计算机程序产品,该计算机程序产品包括用于当在处理部件或模块上运行时执行根据第二方面和/或第四方面的方法的代码部件。该计算机程序产品可以被实施在计算机可读介质上,和/或该计算机程序产品可直接加载到计算机的内部存储器中和/或可以通过上传、下载和推送过程中的至少一项经由网络可传输。

26、根据本发明的第六方面,提供了一种装置,该装置包括:

27、用于生成包括信息比特和奇偶校验比特的码块的部件,奇偶校验比特通过对信息比特执行循环冗余校验而被生成,

28、用于基于应用的线性纠错码基础图和/或基于信息比特的数目来确定在生成码块时所使用的奇偶校验比特的数目的部件,以及

29、用于通过使用应用的线性纠错码基础图来对码块编码的部件。

30、根据本发明的第七方面,提供了一种装置,该装置包括

31、用于提供包括关于调制和编码方案的信息的调制和编码方案表的部件,

32、其中该表指定关于包括嵌套结构的调制和编码方案的信息,其中不同的调制和编码方案由相应的索引引用,其中索引由多个比特构成,并且指示与第二线性纠错码基础图有关的调制和编码方案的索引由若干比特指示,该若干比特少于指示与第一线性纠错码基础图有关的调制和编码方案的索引比特的数目。

- 还没有人留言评论。精彩留言会获得点赞!