分频器、分频方法以及本地信号发生器与流程

本发明涉及无线通信,特别是涉及一种分频器、分频方法以及本地信号发生器。

背景技术:

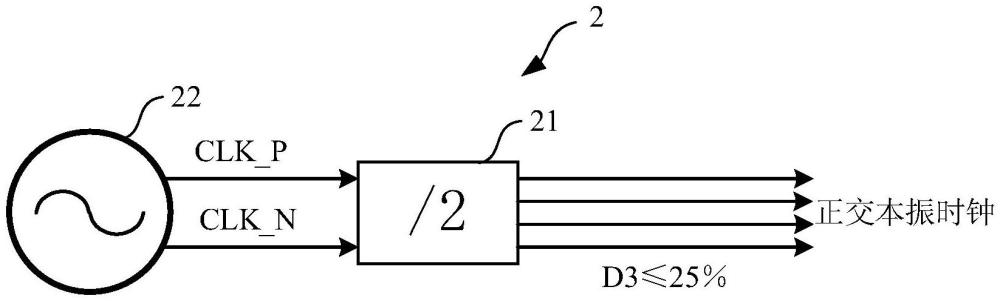

1、无线通信系统在传输信号时,需要将低频基带信号调制到高频载波上,然后将调制信号以电磁波的形式天线辐射出去,这样的技术使得信号能够在无线环境中有效传播。在接收端,接收到的射频频段信号需要被解调并下变频到中频频段。混频器在这个过程中起到了关键作用,特别是在低中频接收机中,混频器通过将射频频段信号下变频到中频频段,配合复数混频器和复数滤波器,可以有效解决镜像干扰的问题。具体而言,混频器主要用于将接收到的射频频段信号与一个本地振荡器(lo)信号混合,从而将射频频段信号的频率转换到较低的中频(if)或基频。在这一过程中,相对于50%占空比的正交本振时钟,25%占空比的正交本振时钟保证了不同的混频器开关不会同时导通,在下变频时的转换增益高3db,这就降低了后级放大器的噪声贡献,同时混频器自身贡献的噪声也相对较小;进一步而言,如果本振时钟占空比小于25%并且相位相差90°,这就可以保证在任何情况下,不同的混频器开关不会同时导通,从而使射频前端优化到最大的增益和最小的噪声系数。

2、但是现有的25%占空比本振时钟往往是将射频锁相环振荡在2倍的本振频率上的差分输出通过除二分频器得到50%占空比的正交本振时钟,再通过组合逻辑电路把正交本振时钟的占空比调整到25%。这一过程中,除二分频器往往有多个工作在最高频率的反相器,这些反相器相互交叉连接,组成触发或锁存逻辑,消耗了巨大的功耗。除此之外,组合逻辑电路也并不能实现将占空比调节至25%以下。

3、应该注意,上面对技术背景的介绍只是为了方便对本技术的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的。不能仅仅因为这些方案在本技术的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种分频器、分频方法以及本地信号发生器,用于解决现有技术中正交本振时钟的功耗大且无法基于逻辑电路实现小于25%占空比的正交本振时钟输出的问题。

2、为实现上述目的及其他相关目的,本发明提供一种分频器,包括:第一分频模块、第二分频模块以及四个占空比调节模块;

3、所述第一分频模块接收第一时钟输入信号并得到第一时钟输出信号以及第二时钟输出信号,所述第二分频模块接收第二时钟输入信号并得到第三时钟输出信号以及第四时钟输出信号,所述第一时钟输入信号以及所述第二时钟输入信号的周期相同;所述第一分频模块以及所述第二分频模块相互配合,使得所述第一时钟输出信号、所述第三时钟输出信号、所述第二时钟输出信号以及所述第四时钟输出信号的相位依次延迟,且各时钟输出信号的周期均为对应的时钟输入信号分频后的周期;

4、四个所述占空比调节模块中:两个所述占空比调节模块对应连接所述第一分频模块输出的两个时钟输出信号,还连接所述第二时钟输入信号;另外两个所述占空比调节模块对应连接所述第二分频模块输出的两个时钟输出信号,还连接所述第一时钟输入信号;各所述占空比调节模块基于对应连接的时钟输入信号的跳变沿,调节对应连接的时钟输出信号的占空比。

5、可选地,所述第一分频模块包括第一时钟触发单元、第一锁存单元以及第一感应单元,所述第二分频模块包括第二时钟触发单元、第二锁存单元以及第二感应单元;

6、所述第一时钟触发单元接收所述第一时钟输入信号,并在感应到所述第一时钟输入信号的跳变沿后发出两路第一时钟触发信号;

7、所述第二时钟触发单元接收所述第二时钟输入信号,并在感应到所述第二时钟输入信号的跳变沿后发出两路第二时钟触发信号;

8、所述第一锁存单元接收所述第一时钟触发单元发出的两路第一时钟触发信号,以输出所述第一时钟输出信号以及所述第二时钟输出信号;

9、所述第二锁存单元接收所述第二时钟触发单元发出的两路第二时钟触发信号,以输出所述第三时钟输出信号以及所述第四时钟输出信号;

10、所述第一感应单元分别接收所述第三时钟输出信号以及所述第四时钟输出信号,并连接所述第一时钟输出信号以及第二时钟输出信号,基于所述第三时钟输出信号以及所述第四时钟输出信号的电平状态控制所述第一时钟输出信号以及第二时钟输出信号的电平持续时间;

11、所述第二感应单元分别接收所述第一时钟输出信号以及所述第二时钟输出信号,并连接所述第三时钟输出信号以及第四时钟输出信号,基于所述第一时钟输出信号以及所述第二时钟输出信号的电平状态控制所述第三时钟输出信号以及第四时钟输出信号的电平持续时间。

12、可选地,所述第一时钟触发模块及所述第二时钟触发模块的结构相同;所述第一时钟触发模块及所述第二时钟触发模块均包括第一mos管及第二mos管,其中,所述第一mos管及所述第二mos管的器件类型相同;

13、当所述第一mos管及所述第二mos管均为pmos管时,两个mos管的栅极相连并接收对应的时钟输入信号,两个mos管的源极均连接供电电压,漏极分别输出对应的时钟触发信号;

14、当所述第一mos管及所述第二mos管均为nmos管时,两个mos管的栅极相连并接收对应的时钟输入信号,两个mos管的源极均连接参考地,漏极分别输出对应的时钟触发信号。

15、可选地,所述第一锁存单元及所述第二锁存单元的结构相同,包括第一pmos管、第二pmos管、第一nmos管以及第二nmos管;

16、当所述第一时钟触发单元包括两个pmos管时,所述第一pmos管的源极以及所述第二pmos管的源极分别连接对应的时钟触发信号;所述第一pmos管的栅极连接所述第二pmos管的漏极;所述第二pmos管的栅极连接所述第一pmos管的漏极;所述第一pmos管的漏极还连接所述第一nmos管的漏极;所述第二pmos管的漏极还连接所述第二nmos管的漏极;所述第一nmos管的栅极连接所述第二nmos管的漏极;所述第二nmos管的栅极连接所述第一nmos管的漏极;所述第一nmos管的源极以及所述第二nmos管的源极均连接参考地;其中,所述第一nmos管的漏极以及所述第二nmos管的漏极分别输出不同的时钟输出信号;

17、当所述第一时钟触发单元包括两个nmos管时,所述第一nmos管的源极以及所述第二nmos管的源极分别连接对应的时钟触发信号;所述第一nmos管的栅极连接所述第二nmos管的漏极;所述第二nmos管的栅极连接所述第一nmos管的漏极;所述第一nmos管的漏极还连接所述第一pmos管的漏极;所述第二nmos管的漏极还连接所述第二pmos管的漏极;所述第一pmos管的栅极连接所述第二pmos管的漏极;所述第二pmos管的栅极连接所述第一pmos管的漏极;所述第一pmos管的源极以及所述第二pmos管的源极均连接供电电压;其中,所述第一pmos管的漏极以及所述第二pmos管的漏极分别输出不同的时钟输出信号。

18、可选地,所述第一感应单元及所述第二感应单元的结构相同;所述第一感应单元及所述第二感应单元均包括第三mos管及第四mos管,其中,所述第三mos管及所述第四mos管的器件类型相同;

19、当所述第三mos管及所述第四mos管均为nmos管时,两个mos管的源极均连接参考地,栅极分别接收所述第三时钟输出信号以及所述第四时钟输出信号,漏极分别连接所述第一锁存单元输出的时钟输出信号;

20、当所述第三mos管及所述第四mos管均为pmos管时,两个mos管的源极均连接供电电压,栅极分别接收所所述第一时钟输出信号以及所述第二时钟输出信号,漏极分别连接所述第一锁存单元输出的时钟输出信号。

21、可选地,所述占空比调节模块包括超前晶体管以及反相器单元;

22、所述超前晶体管为pmos管;所述反相器单元包括串联设置的第一反相器以及第二反相器;所述第一反相器的输入端连接各占空比调节模块对应接收的时钟输出信号,所述第二反相器的输出端输出已调节占空比的正交本征时钟信号;所述超前晶体管的栅极连接对应的时钟输入信号,源极连接供电电压,漏极连接所述第一反相器以及所述第二反相器之间的节点;

23、所述超前晶体管设置为nmos管;所述反相器单元包括串联设置的第三反相器、第四反相器以及第五反相器;所述第三反相器的输入端连接各占空比调节模块对应接收的时钟输出信号,所述第五反相器的输出端输出已调节占空比的正交本征时钟信号;所述超前晶体管的栅极连接对应的时钟输入信号,源极连接参考地,漏极连接所述第三反相器以及所述第四反相器之间的节点。

24、可选地,所述第一时钟输入信号以及所述第二时钟输入信号设置为差分信号。

25、可选地,所述第一时钟输出信号、所述第二时钟输出信号、所述第三时钟输出信号以及所述第四时钟输出信号之间相互正交。

26、可选地,所述占空比调节至小于各时钟输出信号周期的1/4。

27、为实现上述目的及其他相关目的,本发明提供一种分频方法,包括:接收第一时钟输入信号以及所述第二时钟输入信号,并对所述第一时钟输入信号以及所述第二时钟输入信号进行路数倍增以及信号分频得到所述第一时钟输出信号、所述第二时钟输出信号、所述第三时钟输出信号以及所述第四时钟输出信号,其中,所述第一时钟输入信号以及所述第二时钟输入信号的周期相同,所述第一时钟输出信号、所述第三时钟输出信号、所述第二时钟输出信号以及所述第四时钟输出信号的相位依次延迟,所述第一时钟输出信号以及所述第二时钟输出信号的周期为所述第一时钟输入信号分频后的周期,所述第三时钟输出信号以及所述第四时钟输出信号的周期为所述第二时钟输入信号分频后的周期;

28、基于所述第一时钟输入信号以及所述第二时钟输入信号的跳变沿,所述占空比调节模块调节对应连接的时钟输出信号的占空比。

29、为实现上述目的及其他相关目的,本发明提供一种本地信号发生器,包括:上述的分频器。

30、如上所述,本发明的分频器、分频方法以及本地信号发生器,具有以下有益效果:

31、1、本发明通过第一分频模块以及第二分频模块相互配合,通过四路时钟输出信号之间的充放电构成的循环周期,将2路时钟输入信号完成路数倍增以及信号分频,直接得到四路时钟输出信号并基于超前晶体管进行占空比调节。

32、2、本发明充分利用了晶体管的开关特性,使得工作在最高频率的晶体管能较大程度地减少,充分降低了分频器的功耗,同时,在输出反相器单元中加入了时钟驱动的超前晶体管,使得正交本振时钟信号在拥有正交特性以外,其占空比小于25%,有利于构建最大转换增益和最小噪声系数的射频前端,避免了传统的除二分频器内部多个工作在最高频率的反相器造成的巨大的功耗。同时,由于本发明不需要额外设置组合逻辑,进一步减少了额外的电路功耗以及避免了传统逻辑电路无法输出占空比小于25%的正交本振时钟的问题。

- 还没有人留言评论。精彩留言会获得点赞!