闪存单元的写入方法与流程

本公开涉及半导体技术的领域,具体地,本公开涉及闪存单元的写入方法。

背景技术:

1、快闪存储器,简称闪存,是一种非易失性存储器,即在电源断开的情况下仍然不会丢失所存储的数据,特别适用于移动通讯和计算机存储部件等领域。此外,有些快闪存储器还具有高密度存储能力,适用于大容量移动存储介质等方面的应用。

2、传统的快闪存储器采用浮栅型单元结构。浮栅型非易失性存储器起源于d.kahng与s.sze在1967年提出的mimis(metal-insulator-metal-insulator-semiconductor:金属-绝缘体-金属-绝缘体-半导体)结构。该结构在传统的mosfet(metal-oxide-semiconductor field effect transistor:金属氧化物半导体场机制晶体管)的基础上增加一个金属浮栅和一个超薄的隧穿氧化物层,从而利用金属浮栅来存储电荷。基于此,masuoka等人在1984年首次提出快闪存储器(flash memory)的概念,即通过按块(sector)擦除按位写入(编程)来实现高速擦除能力,并且消除了eeprom(erasable programmableread-only memory:可擦除可编程只读存储器)中必需的选择管,从而具有更小的存储单元尺寸。快闪存储器出现以后,以其高写入速度、高集成度和优越的性能迅速得到发展。intel公司在1988年提出了etox结构闪存单元(etox:electron tunneling oxide device,电子隧穿氧化物器件),成为至今大部分的浮栅型闪存单元结构的发展基础。

3、然而,浮栅型快闪存储器具有如下缺点:工艺较为复杂;由于闪存单元中的浮栅结构的存在增加了栅结构的纵向高度,不利于按比例缩小工艺尺寸和单元面积;同时因为浮栅的导电性,存储的电荷可以在浮栅中自由移动,因而不利于提高存储器的可靠性。为解决浮栅型快闪存储器的工艺复杂、可靠性差等问题,研究人员提出一种利用氮化硅介质存储电荷的电荷俘获型存储器(ctm:charge-trapping-memory),也称为sonos型(silicon-oxide-nitride-oxide-silicon:硅-氧化物-氮化物-氧化物-硅)快闪存储器。基于此,b.eitan等人在2000年提出了一种两位存储单元结构nrom(nitride-read-only-memory:氮化硅只读存储器),该单元结构利用绝缘氮化硅存储介质不导电的特性在一个存储晶体管的源极端和漏极端分别实现两个存储位,然而该单元结构存在其中两个存储位相互干扰,器件尺寸无法缩小等缺点。另一方面,现有sonos型闪存单元一般采用沟道热电子注入(che)物理效应进行写入操作,采用带带隧穿热空穴注入(bbhh)物理效应或fn隧穿物理效应进行擦除操作,由于擦写采用的物理机制不同,写入操作注入的陷阱电子电荷和擦除操作注入的陷阱空穴电荷分布不一致,即容易产生陷阱电荷失配效应(tcme),导致闪存单元耐久性和保持可靠性退化。

4、然而,现有的浮栅型etox快闪存储器和sonos型nrom快闪存储器都存在工艺尺寸无法缩小、单元面积大、写入功耗大及阵列面积开销大的问题,无法实现吉比特(gb)容量以上的高密度集成。

5、随着移动智能终端、可穿戴设备、智能传感器网络等应用的迅速发展,对快闪存储器的功耗、存储容量、成本均提出了更高的要求,因此需要一种具有功耗低、单元面积小、工艺尺寸可缩小、阵列集成密度高、容量大等优点的快闪存储器技术。

技术实现思路

1、在本背景技术部分中公开的以上信息仅用于理解发明构思的背景,并且因此它可能包含不构成现有技术的信息。

2、为了解决现有技术中存在的以上问题,本公开提出了闪存单元的写入方法,又称编程方法。

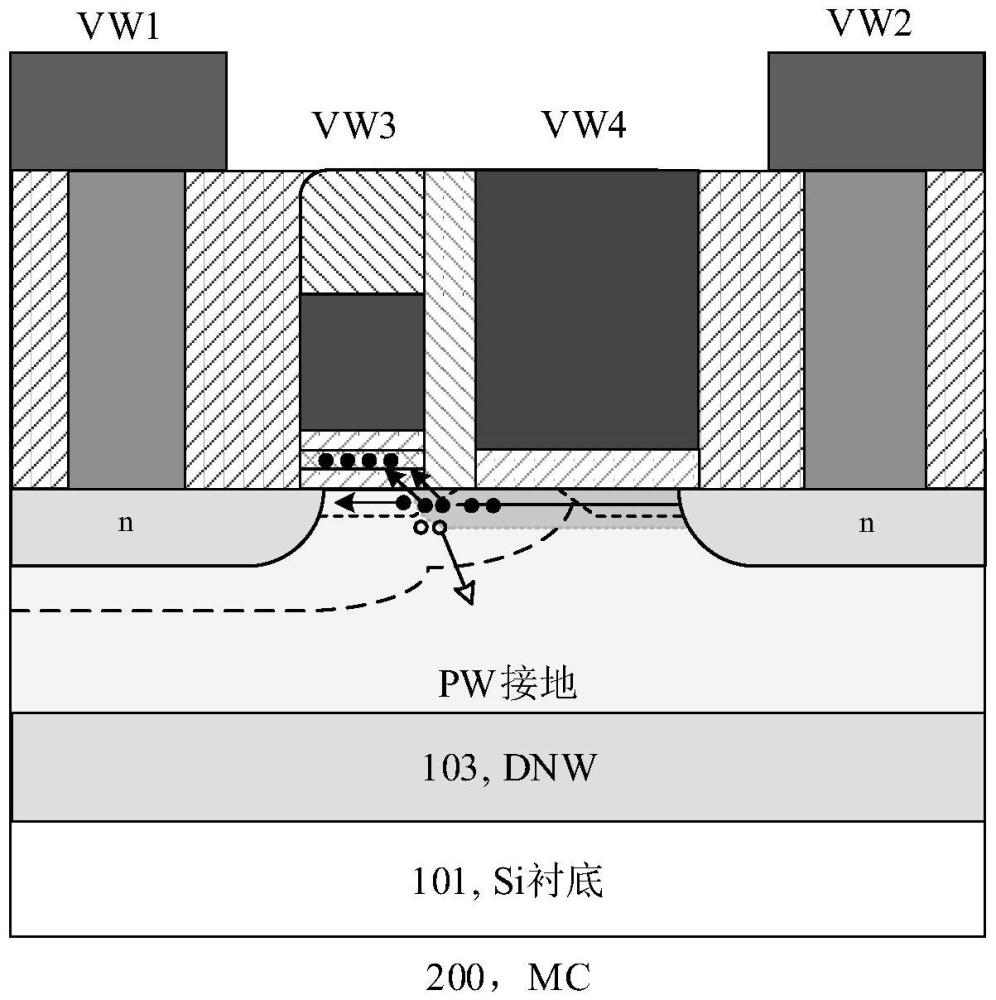

3、根据本公开的一个方面,提供了一种闪存单元的写入方法,该闪存单元包括:衬底,包括深阱区和设置在深阱区上的阱区;存储晶体管,设置在阱区上并且被配置为存储数据;以及选通晶体管,在阱区上沿水平方向设置在存储晶体管一侧,被配置为对存储晶体管执行选通操作,其中,存储晶体管和选通晶体管串联连接,其中,存储晶体管的源极区连接到闪存单元的第一电极,选通晶体管的漏极区连接到闪存单元的第二电极,该写入方法包括:第一写入步骤,通过将第一写入电压施加到第一电极,将第二写入电压施加到第二电极,将第三写入电压施加到存储晶体管的栅电极,以及将第四写入电压施加到选通晶体管的栅电极,对存储晶体管执行写入操作;以及第二写入步骤,通过将第一写入电压施加到第一电极,将第二写入电压施加到第二电极,将高于第三写入电压的第六写入电压施加到存储晶体管的栅电极,以及将第四写入电压施加到选通晶体管的栅电极,对存储晶体管执行写入操作,其中,第四写入电压等于或低于第一电源电压,第二写入电压等于或高于第二电源电压,第一写入电压高于预设电压,第三写入电压高于第一写入电压,其中,第一电源电压高于第二电源电压,其中,预设电压是根据衬底与存储晶体管的栅介质叠层之间的界面处的载流子势垒高度预先设定的,其中,第一写入电压和第四写入电压高于第二写入电压,以及其中,在闪存单元的写入操作期间,存储晶体管和选通晶体管均导通。

4、根据本公开的另一方面,提供了一种闪存单元的写入方法,该闪存单元包括:衬底,包括深阱区和设置在深阱区上的阱区;第一存储晶体管,设置在阱区上并且被配置为存储第一数据;第二存储晶体管,设置在阱区上并且被配置为存储第二数据;以及选通晶体管,在阱区上沿水平方向设置在第一存储晶体管和第二存储晶体管之间,被配置为隔离第一存储晶体管和第二存储晶体管并且对第一存储晶体管和第二存储晶体管执行选通操作,其中第一存储晶体管、选通晶体管和第二存储晶体管依次串联连接,其中第一存储晶体管的源极区连接到闪存单元的第一电极,第二存储晶体管的漏极区连接到闪存单元的第二电极,该写入方法包括:第一写入步骤,通过将第一写入电压施加到第一电极或第二电极,将第二写入电压施加到第二电极或第一电极,将第三写入电压施加到第一存储晶体管或第二存储晶体管的栅电极,将第四写入电压施加到选通晶体管的栅电极,以及将第五写入电压施加到第二存储晶体管或第一存储晶体管的栅电极,对第一存储晶体管或第二存储晶体管执行写入操作;以及第二写入步骤,通过将第一写入电压施加到第一电极或第二电极,将第二写入电压施加到第二电极或第一电极,将高于第三写入电压的第六写入电压施加到第一存储晶体管或第二存储晶体管的栅电极,将第四写入电压施加到选通晶体管的栅电极,以及将第五写入电压施加到第二存储晶体管或第一存储晶体管的栅电极,对第一存储晶体管或第二存储晶体管执行写入操作,其中,第四写入电压等于或低于第一电源电压,第二写入电压等于或高于第二电源电压,第一写入电压高于预设电压,第三写入电压高于第一写入电压,其中,第一电源电压高于第二电源电压,其中,预设电压是根据衬底与第一存储晶体管和第二存储晶体管的栅介质叠层之间的界面处的载流子势垒高度预先设定的,其中,第一写入电压、第四写入电压和第五写入电压高于第二写入电压,以及其中,在闪存单元的写入操作期间,第一存储晶体管、第二存储晶体管和选通晶体管均导通。

5、根据本公开的闪存单元的写入方法采用双重的沟道热载流子注入机制的写入步骤,较现有的写入方法可以在存储晶体管的存储介质层中在靠近选通晶体管的一侧形成较低的陷阱电荷浓度,而在远离选通晶体管的一侧形成较高的陷阱电荷浓度,因此可以增大存储窗口、能够减轻陷阱电荷失配效应(tcme)的影响,从而能够提高耐久性和保持可靠性。

6、然而,本公开的效果不限于上述效果,并且可以在不脱离本公开的精神和范围的情况下进行各种扩展应当理解,前面的一般描述和下面的详细描述都是示例性和解释性的,并且旨在提供对要求保护的本发明的进一步说明。

- 还没有人留言评论。精彩留言会获得点赞!