一种基于FPGA的Turbo编码设备及解码设备的制作方法

本技术属于数据链通信,更具体地,涉及一种基于fpga的turbo编码设备及解码设备。

背景技术:

1、随着通信技术的不断发展,在数据链领域,物理层通信技术也越来越受到人们的广泛关注,尤其是信息处理方面,不同信息处理方式不同,信息处理内容一般包括信息校验、信道纠错编码和信道交织三个方面的处理。

2、其中,信道纠错编码是保证信息传输速率接近理想信道容量的关键。目前,在数据链通信技术领域,为保证系统具有较好的误码率性能,信道编解码技术常用turbo码编解码来实现。如何基于现场可编程门阵列(field programmable gate array,fpga)实现turbo编解码是本领域亟待解决的技术问题。

技术实现思路

1、针对现有技术的缺陷,本技术的目的在于基于fpga实现turbo编解码。

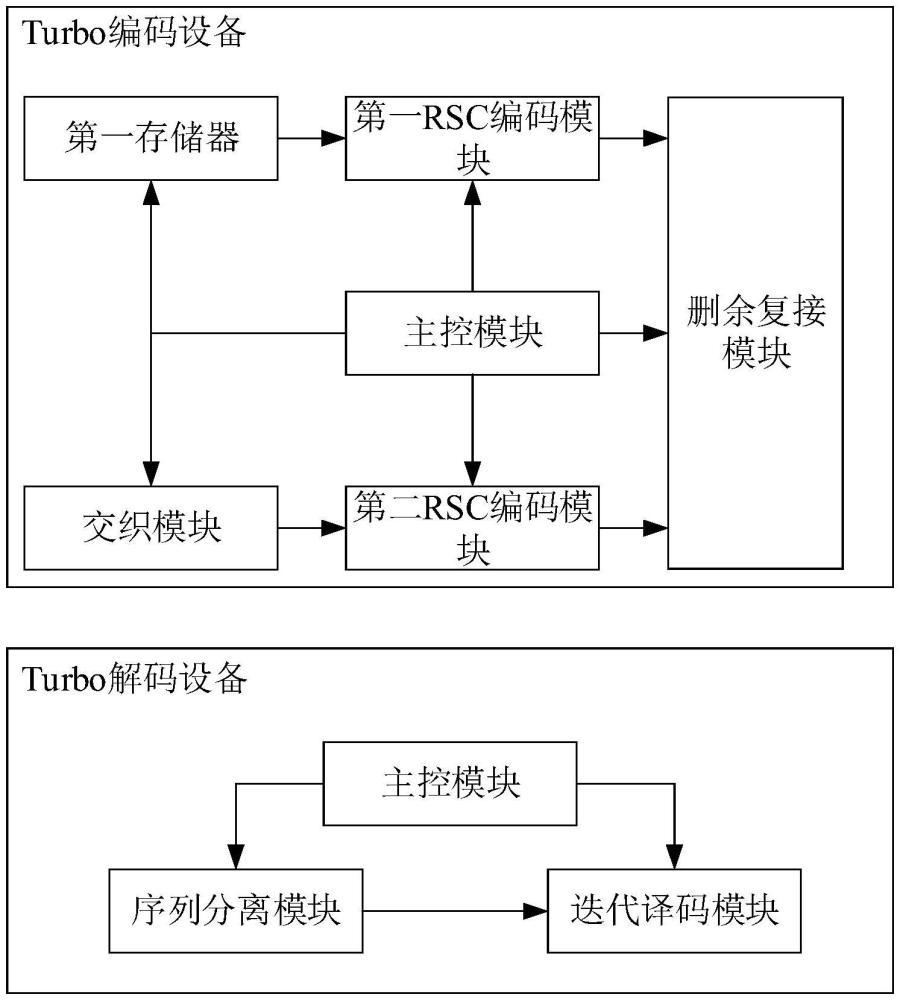

2、为实现上述目的,第一方面,本技术提供了一种基于fpga的turbo编码设备,在turbo编码设备的fpga上配置有主控模块、第一存储器(meg_ram)、交织模块、第一rsc编码模块、第二rsc编码模块和删余复接模块;

3、第一存储器用于缓存第一信息序列(ck);

4、交织模块用于缓存第一信息序列,并基于交织地址,对第一信息序列进行交织映射,获取第二信息序列(c′k);

5、第一rsc编码模块用于从第一存储器读取第一信息序列,并基于第一信息序列进行turbo编码,获取第一系统序列(xk)和第一校验序列(zk);

6、第二rsc编码模块用于从交织模块读取第二信息序列,并基于第二信息序列进行turbo编码,获取第二系统序列(x′k)和第二校验序列(z′k);

7、删余复接模块用于基于第一系统序列、第一校验序列、第二系统序列和第二校验序列,进行删余处理以及复接处理,获取turbo编码结果;

8、主控模块用于控制各个编码模块的工作状态以及控制本设备中各个存储器的读写地址。

9、在一种可能的实现方式中,交织模块包括第二存储器(rom)和第三存储器(ram_0);

10、第二存储器用于存放交织地址;

11、第三存储器用于缓存第一信息序列,以及按照交织地址对第一信息序列进行交织映射,获取第二信息序列。

12、在一种可能的实现方式中,删余复接模块包括用于缓存第一系统序列的第四存储器(ram_1)、用于缓存第一校验序列的第五存储器(ram_2)、用于缓存第二系统序列的第六存储器(ram_3)、用于缓存第二校验序列的第七存储器(ram_4)和删余复接单元;

13、删余复接单元用于从第四存储器、第五存储器、第六存储器和第七存储器读取出第一系统序列、第一校验序列、第二系统序列和第二校验序列,并对读取出的序列进行删余处理以及复接处理,获取turbo编码结果。

14、第二方面,本技术提供一种turbo编码方法,应用于第一方面或第一方面的任一种可能的实现方式所描述的基于fpga的turbo编码设备,该方法包括:

15、获取第一信息序列;

16、基于交织地址,对第一信息序列进行交织映射,获取第二信息序列;

17、基于第一信息序列进行编码,获取第一系统序列和第一校验序列;以及基于第二信息序列进行编码,获取第二系统序列和第二校验序列;

18、基于第一系统序列、第一校验序列、第二系统序列和第二校验序列,进行删余处理以及复接处理,获取turbo编码结果。

19、第三方面,本技术提供一种基于fpga的turbo解码设备,在turbo解码设备的fpga上配置有序列分离模块(decoder_algorithm模块)、迭代译码模块(decoder_maxlogmap模块)和主控模块;

20、序列分离模块用于接收待解码的第三信息序列,从接收到的第三信息序列中分离出系统序列和校验序列,并输出系统序列和校验序列至迭代译码模块;

21、迭代译码模块用于基于系统序列、校验序列和先验信息,进行siso迭代译码,获取turbo解码结果;

22、主控模块用于控制各个解码模块的工作状态以及控制本设备中各个存储器的读写地址。

23、在一种可能的实现方式中,siso迭代译码具体采用max-log-map算法。

24、第四方面,本技术提供一种turbo解码方法,应用于第三方面或第三方面的任一种可能的实现方式所描述的基于fpga的turbo解码设备,该方法包括:

25、获取待解码的第三信息序列;

26、从第三信息序列中分离出系统序列和校验序列;

27、基于系统序列、校验序列和先验信息,进行siso迭代译码,获取turbo解码结果。

28、第五方面,本技术还提供一种基于fpga的编解码系统,该系统包括:基于fpga的turbo编码设备和基于fpga的turbo解码设备,turbo编码设备和turbo解码设备通信连接,通过turbo编码设备和turbo解码设备实现对信息比特的一个编解码处理。

29、turbo编码设备具体用于:获取第一信息序列;基于交织地址,对第一信息序列进行交织映射,获取第二信息序列;基于第一信息序列进行编码,获取第一系统序列和第一校验序列;以及基于第二信息序列进行编码,获取第二系统序列和第二校验序列;基于第一系统序列、第一校验序列、第二系统序列和第二校验序列,进行删余处理以及复接处理,获取turbo编码结果;

30、turbo解码设备具体用于:获取待解码的第三信息序列;从第三信息序列中分离出系统序列和校验序列;基于系统序列、校验序列和先验信息,进行siso迭代译码,获取turbo解码结果。

31、在一种可能的实现方式中,在turbo编码设备的fpga上配置有主控模块、第一存储器、交织模块、第一rsc编码模块、第二rsc编码模块和删余复接模块;

32、第一存储器用于缓存第一信息序列;

33、交织模块用于缓存第一信息序列,并基于交织地址,对第一信息序列进行交织映射,获取第二信息序列;

34、第一rsc编码模块用于从第一存储器读取第一信息序列,并基于第一信息序列进行编码,获取第一系统序列和第一校验序列;

35、第二rsc编码模块用于从交织模块读取第二信息序列,并基于第二信息序列进行编码,获取第二系统序列和第二校验序列;

36、删余复接模块用于基于第一系统序列、第一校验序列、第二系统序列和第二校验序列,进行删余处理以及复接处理,获取turbo编码结果;

37、主控模块用于控制各个编码模块的工作状态以及控制本设备中各个存储器的读写地址。

38、在一种可能的实现方式中,在turbo解码设备的fpga上配置有序列分离模块、迭代译码模块和主控模块;

39、序列分离模块用于接收待解码的第三信息序列,从接收到的第三信息序列中分离出系统序列和校验序列,并输出系统序列和校验序列至迭代译码模块;

40、迭代译码模块用于基于系统序列、校验序列和先验信息,进行siso迭代译码,获取turbo解码结果;

41、主控模块用于控制各个解码模块的工作状态以及控制本设备中各个存储器的读写地址。

42、总体而言,通过本技术所构思的以上技术方案与现有技术相比,具有以下有益效果:

43、(1)通过在turbo编码设备的fpga上配置主控模块、第一存储器(meg_ram)、交织模块、第一rsc编码模块、第二rsc编码模块和删余复接模块,可以获取第一信息序列,进而基于交织地址,对第一信息序列进行交织映射,获取第二信息序列,进而基于第一信息序列进行编码,获取第一系统序列和第一校验序列;以及基于第二信息序列进行编码,获取第二系统序列和第二校验序列,进而基于第一系统序列、第一校验序列、第二系统序列和第二校验序列,进行删余处理以及复接处理,获取编码结果,能够基于fpga实现turbo编码。

44、(2)通过在turbo解码设备的fpga上配置有序列分离模块(decoder_algorithm模块)、迭代译码模块(decoder_maxlogmap模块)和主控模块,可以获取待解码的第三信息序列,进而从第三信息序列中分离出系统序列和校验序列,进而基于系统序列、校验序列和先验信息,进行siso迭代译码,获取解码结果,能够基于fpga实现turbo解码。

45、(3)采用本技术提供的turbo编解码设备,能够提高系统信息处理能力,同时能保证系统获得较好的误码率性能;本技术结构简单,可以使用硬件描述语言verilog语言,搭建硬件环境实现,具有较高的实用性。

- 还没有人留言评论。精彩留言会获得点赞!