一种数模转换器的电流折叠校准方法及系统与流程

本发明涉及dac校准,尤其是涉及一种数模转换器的电流折叠校准方法及系统。

背景技术:

1、世界中信息主要是以模拟的方式存在,而非离散的数字信号。因此,在处理信息时需要工具在模拟与数字之间搭建起一座信号传递的桥梁,而数模转换器(digital-to-analog converter,dac)正是在其中发挥作用的工具。例如有线或者无线通讯、视频信号处理、直接数字信号合成等,高速高精度转换器的性能很大程度上决定了整个系统的性能,在高速高精度通讯领域,转换器的性能甚至可能成为系统整体性能的瓶颈。因此,无论在学术界还是工业界,对转换器性能的研究一直以来都是热点。

2、在cmos工艺制造过程中,由于器件失配,掺杂浓度分布不均,温度分布不均,ir电压降等工艺制造的原因,这些非理想因素影响了dac的匹配特性,对dac的性能造成比较大的影响。近年来,随着半导体工艺的不断发展,晶体管特征尺寸越来越小,器件尺寸的缩小使dac 具有更快的转换频率以及更大的信号带宽。但是小尺寸工艺下电源电压也越来越低,器件二级效应越来越突出,导致高速高精度dac 的设计难度越来越大。

3、dac的性能可以通过提高电流源的匹配精度进行优化,增大晶体管尺寸是提高电流源的匹配精度的方式,使得电流镜的复制更准确。可以通过优化版图布局来减小在制造过程中因掺杂浓度偏差等工艺误差导致的dac随机偏差。随着对dac精度和速度的要求越来越高,通过以上方式来达到如此高的匹配要求是非常困难的。因此,在dac设计中使用电流校准技术成为越来越通用的方式。

4、增大晶体管尺寸可以提高电流源的匹配精度进而改善dac的静态性能。但是随着芯片面积越来越小,电流源的栅极面积对于dac设计来说变得更重要。此外,晶体管的尺寸过大会引发更严重的寄生和梯度效应,导致高频情况下的sfdr降低。在版图布局中可以采用调整晶体管布局、增加dummy管等措施来优化匹配情况,但是采用版图优化的方式对消除因掺杂浓度不均、温度分布不均,ir电压降等工艺制造问题导致的匹配偏差优化效果有限。因此,亟需设计一种高精度dac匹配性能的校准方法。

技术实现思路

1、本发明的目的在于克服现有技术中的不足,提供一种数模转换器的电流折叠校准方法及系统,能够基于电流比较将电流源组合成二进制加权阵列,来实现高精度dac的匹配性能。

2、为解决上述技术问题,本发明是采用下述技术方案实现的:

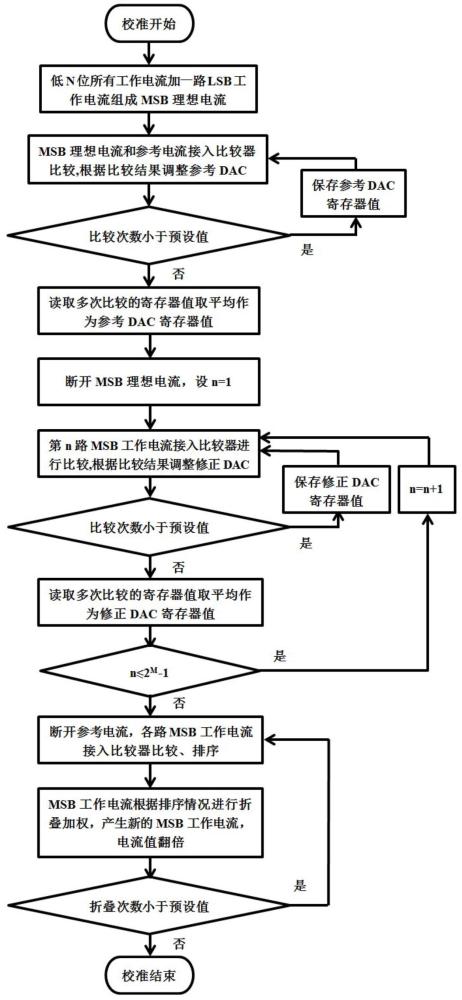

3、一方面,本发明提供了一种数模转换器的电流折叠校准方法,包括:

4、将低n位的工作电流加一路最低有效位工作电流后构成最高有效位理想电流,将所述最高有效位理想电流和参考电流进行比较,得到第一比较结果;根据所述第一比较结果,校准参考电流,得到校准后的参考电流及其对应的dac寄存器值;其中n≥2;

5、将最高有效位工作电流代替最高有效位理想电流和校准后的参考电流进行比较,得到第二比较结果;根据所述第二比较结果,校准最高有效位工作电流,得到校准后的最高有效位工作电流及其对应的dac寄存器值;

6、对校准后的每一路最高有效位工作电流进行排序,得到排序后的最高有效位工作电流;

7、选取排序后的第2m-1路最高有效位工作电流作为高m位中的独立位,将排序后的第1路最高有效位工作电流与排序后的第2m-1路最高有效位工作电流相加、排序后的第2路最高有效位工作电流与排序后的第2m-2路最高有效位工作电流相加、排序后的第3路最高有效位工作电流与排序后的第2m-3路最高有效位工作电流相加、以此类推、直到排序后的第2m-1-1路最高有效位工作电流与排序后的第2m-1+1路最高有效位工作电流相加,得到折叠校准后的电流源组合;其中m≥2。

8、对工作电流进行折叠的原理是折叠后挑选出的中间的电流单元电流值是其余两两相加单元电流值的一半,每个两两相加单元的电流值之间的差值减小,改善了因电流偏差导致的dac性能下降问题。

9、可选的,所述校准后的参考电流及其对应的dac寄存器值的确定步骤包括:

10、根据预设的第一校准次数校准参考电流,得到多个参考电流及其对应的dac寄存器值;

11、将多个参考电流对应的dac寄存器值取平均值作为校准后的参考电流对应的dac寄存器值。

12、重复执行取平均值是为了尽量避免在比较过程中出现随机问题、对比较的结果产生影响、对dac整体引入新的随机误差。

13、可选的,所述校准后的最高有效位工作电流及其对应的dac寄存器值的确定步骤包括:

14、根据预设的第二校准次数校准第n路最高有效位工作电流,得到第n路的多个最高有效位工作电流及其对应的dac寄存器值;

15、将第n路的多个最高有效位工作电流对应的dac寄存器值取平均值作为校准后的第n路最高有效位工作电流对应的dac寄存器值;其中n≤2m-1。

16、可选的,还包括:

17、重新对校准后的每一路最高有效位工作电流进行排序,得到重新排序后的最高有效位工作电流;

18、选取重新排序后的第2m-2路最高有效位工作电流作为高m-1位中的独立位,将重新排序后的第1路最高有效位工作电流与重新排序后的第2m-1-1路最高有效位工作电流相加、重新排序后的第2路最高有效位工作电流与重新排序后的第2m-1-2路最高有效位工作电流相加、重新排序后的第3路最高有效位工作电流与重新排序后的第2m-1-3路最高有效位工作电流相加、以此类推、直到重新排序后的第2m-2-1路最高有效位工作电流与重新排序后的第2m-2+1路最高有效位工作电流相加;

19、重复执行,直至达到预设的折叠次数,得到折叠校准后的电流源组合。

20、可选的,折叠一次得到的所述折叠校准后的电流源组合包括1个第一电流源和2m-1-1个第二电流源,所述第二电流源的电流值为两倍第一电流源的电流值。

21、可选的,利用比较器,将所述最高有效位理想电流和参考电流进行比较、将最高有效位工作电流代替最高有效位理想电流和校准后的参考电流进行比较、对校准后的每一路最高有效位工作电流进行排序。

22、可选的,所述校准后的参考电流对应的dac寄存器值、所述校准后的最高有效位工作电流对应的dac寄存器值和所述折叠校准后的电流源组合分别保存至存储模块。

23、另一方面,本发明提供了一种数模转换器的电流折叠校准系统,所述系统采用第一方面所述的方法进行电流折叠校准,所述系统包括主dac、修正dac、参考dac、比较器和数字校准逻辑电路;

24、所述主dac和所述修正dac连接后与所述比较器的第一输入端连接,所述参考dac与所述比较器的第二输入端连接,所述比较器的输出端与所述数字校准逻辑电路连接。

25、可选的,所述低n位的工作电流和最低有效位工作电流均来源于主dac,所述参考电流来源于参考dac,所述最高有效位工作电流来源于主dac和修正dac;

26、所述参考dac,用于:控制参考电流;

27、所述修正dac,用于:控制最高有效位工作电流;

28、所述比较器,用于:将所述最高有效位理想电流和参考电流进行比较,得到第一比较结果;将最高有效位工作电流代替最高有效位理想电流和校准后的参考电流进行比较,得到第二比较结果;对校准后的每一路最高有效位工作电流进行排序,得到排序后的最高有效位工作电流;

29、所述数字校准逻辑电路,用于:根据所述第一比较结果,校准参考电流,得到校准后的参考电流对应的dac寄存器值;根据所述第二比较结果,校准最高有效位工作电流,得到校准后的最高有效位工作电流及其对应的dac寄存器值;选取排序后的第2m-1路最高有效位工作电流作为高m位中的独立位,将排序后的第1路最高有效位工作电流与排序后的第2m-1路最高有效位工作电流相加、排序后的第2路最高有效位工作电流与排序后的第2m-2路最高有效位工作电流相加、排序后的第3路最高有效位工作电流与排序后的第2m-3路最高有效位工作电流相加、以此类推、直到排序后的第2m-1-1路最高有效位工作电流与排序后的第2m-1+1路最高有效位工作电流相加,得到折叠校准后的电流源。

30、与现有技术相比,本发明所达到的有益效果:

31、本发明降低了对电流源栅极面积的要求,通过对工作电流进行折叠,保证了折叠后挑选出的中间的电流单元电流值是其余两两相加单元电流值的一半,每个两两相加单元的电流值之间的差值减小,改善了因电流偏差导致的dac性能下降问题;能够降低因掺杂浓度、边缘效应、温度梯度等工艺问题导致的系统偏差和随机偏差,每个工作电流之间都会保持相同的比较器偏差,可以降低因比较器偏差导致的系统偏差,将相关寄存器值保存在存储模块中,在工作前读出设置,不会增加工作电流;系统仅使用最低要求的模拟电路和一些数字电路,模拟电路仅仅是增加了比较器和修正dac、参考dac电路,数字逻辑过程也并不复杂。

- 还没有人留言评论。精彩留言会获得点赞!