无过量环路时延补偿的连续时间Σ-Δ调制器的制作方法

本发明涉及σ-δ调制器,尤其是涉及一种无过量环路时延补偿的连续时间σ-δ调制器、模数转换方法、电子设备和存储介质。

背景技术:

1、随着物联网的发展,片上系统(soc)解决方案对高分辨率、宽带宽和低功耗的模数转换器(adc)的需求不断增长。在此类应用中,连续时间σ-δ调制器(ct sdm)因其固有的抗混叠功能以及相对较高且恒定的输入阻抗特性而成为首选,与离散时间(dt)的同类产品相比,简化了adc驱动器设计。对于中高带宽和节能设计目标,过采样率(osr)通常受到限制,为了获得足够的信噪量化比(sqnr),出现了采用了多位量化器(qtz)和高阶环路滤波器的ct sdm。

2、ct sdm的传统架构由于其反馈路径的延迟会导致环路采样脉冲的第一个脉冲时间变短,需要在量化之前进行额外环路时延补偿(eldc),以保证系统稳定性。传统的eldc是由eld dac和求和放大器构成,通过将脉冲输入信号以一定增益通过加法器加入反馈回路来实现,因此需要很高的能耗。此外,也存在一些其他的延时补偿的实现方法来降低功耗,例如在k.xing的a10.4mw50mhz-bw 80db-dr single-opamp third-order ct sdm withsab-eld-merged integrator and 3-stage opamp中,eldc通过额外的前馈路径嵌入到积分器中,取消了直接反馈dac和求和放大器,但同时导致了更高规格的高功耗积分器的使用。亦或者,在y.s.shu的a 28fj/conv-step ctδσmodulator with 78db dr and18mhzbw in 28nm cmos using a highly digital multi-bit quantizer中,提到了使用比较器切换技术来实现eldc来降低功耗,但是这样的设计会导致增大电路的面积以及制造更多的输出负载。

3、上述这些设计都产生了一些数量的额外环路时延,因此总会面临着σ-δ调制时积分时间和环路延迟的权衡,最终导致了用于环路滤波的放大器需要更大的带宽。

技术实现思路

1、本发明旨在至少解决现有技术中存在的技术问题之一。为此,本发明提出了一种无过量环路时延补偿的连续时间σ-δ调制器、模数转换方法、电子设备和存储介质,不需要对额外环路延迟进行补偿,并能够缓解对运算放大器的带宽要求。

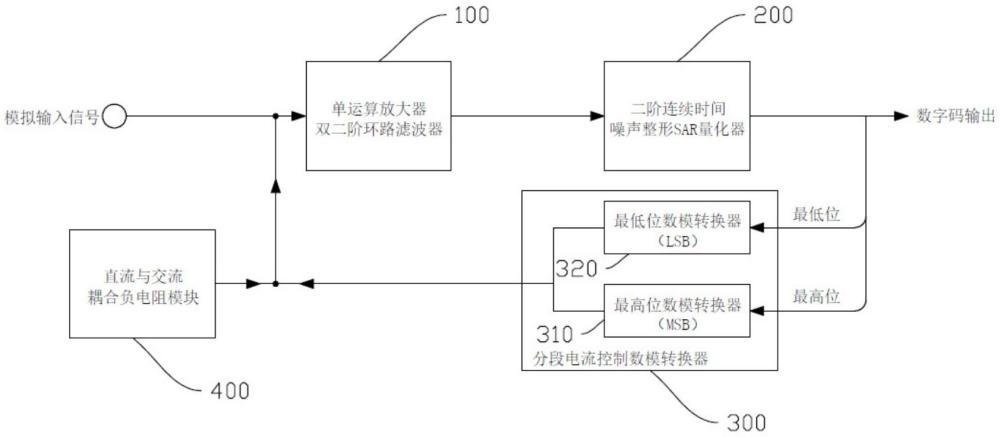

2、一方面,根据本发明实施例的无过量环路时延补偿的连续时间σ-δ调制器,包括:

3、单运算放大器双二阶环路滤波器,输入端用于连接模拟输入信号;

4、二阶连续时间噪声整形sar量化器,输入端与所述单运算放大器双二阶环路滤波器的输出端电连接;

5、分段电流控制数模转换器,输入端与所述二阶连续时间噪声整形sar量化器的输出端电连接,所述分段电流控制数模转换器的输出端与所述单运算放大器双二阶环路滤波器的输入端电连接;

6、直流与交流耦合负电阻模块,输出端与所述分段电流控制数模转换器的输出端及所述单运算放大器双二阶环路滤波器的输入端电连接;

7、其中,所述模拟输入信号与所述分段电流控制数模转换器的输出相减后输入到所述单运算放大器双二阶环路滤波器,经过所述单运算放大器双二阶环路滤波器积分后输出到所述二阶连续时间噪声整形sar量化器,所述二阶连续时间噪声整形sar量化器输出数字码,并将所述数字码反馈到所述分段电流控制数模转换器,由所述分段电流控制数模转换器对所述数字码进行数模转换后,发送到所述单运算放大器双二阶环路滤波器;所述直流与交流耦合负电阻模块用于提供额外电流,以补偿所述单运算放大器双二阶环路滤波器的运算放大器的带宽。

8、根据本发明的一些实施例,所述单运算放大器双二阶环路滤波器包括:

9、运算放大器,所述运算放大器具有同相输入端、反相输入端、同相输出端和反相输出端,所述同相输入端和所述反相输入端分别通过对应的输入电阻连接所述模拟输入信号,所述反相输出端通过相互并联的第一电容和第一电阻与所述同相输入端电连接,所述反相输出端通过相互串联的第二电阻和第二电容与所述反相输入端电连接,所述同相输出端通过相互并联的第三电容和第三电阻与所述反相输入端电连接,所述同相输出端通过相互串联的第四电阻和第四电容与所述同相输入端电连接。

10、根据本发明的一些实施例,所述二阶连续时间噪声整形sar量化器包括:

11、输入跟踪及复位模块,输入端与所述单运算放大器双二阶环路滤波器的输出端电连接;

12、电容式dac,输入端与所述输入跟踪及复位模块的输出端电连接;

13、依次式残差提取模块,输入端与所述电容式dac的输出端电连接;

14、无源集成与比较模块,输入端与所述依次式残差提取模块的输出端电连接,所述无源集成与比较模块的输出端用于输出所述数字码,并与所述分段电流控制数模转换器的输入端电连接,并与所述电容式dac的输入端电连接。

15、根据本发明的一些实施例,所述依次式残差提取模块包括:

16、第一开关,所述第一开关的第一端与所述电容式dac的输出端电连接;

17、第二开关,所述第二开关的第一端与所述第一开关的第二端电连接,所述第二开关的第二端与所述无源集成与比较模块的输入端电连接;

18、第一残差提取电容,所述第一残差提取电容的第一端与所述第一开关的第二端及所述第二开关的第一端电连接,所述第一残差提取电容的第二端接地;

19、第三开关,所述第三开关的第一端与所述电容式dac的输出端电连接;

20、第四开关,所述第四开关的第一端与所述第三开关的第二端电连接,所述第四开关的第二端与所述无源集成与比较模块的输入端电连接;

21、第二残差提取电容,所述第二残差提取电容的第一端与所述第三开关的第二端及所述第四开关的第一端电连接,所述第二残差提取电容的第二端接地。

22、根据本发明的一些实施例,所述无源集成与比较模块包括:

23、多输入比较器,所述多输入比较器的第一同相输入端与所述依次式残差提取模块的输出端电连接,所述多输入比较器的第二同相输入端通过第五开关与所述依次式残差提取模块的输出端电连接,所述多输入比较器的第三同相输入端通过第六开关与所述依次式残差提取模块的输出端电连接,所述多输入比较器的反相输入端接地,所述多输入比较器的输出端用于输出所述数字码,并与所述分段电流控制数模转换器的输入端电连接,并与所述电容式dac的输入端电连接;

24、第一集成电容,所述第一集成电容的第一端与所述多输入比较器的第二同相输入端电连接,所述第一集成电容的第二端接地;

25、第二集成电容,所述第二集成电容的第一端与所述多输入比较器的第三同相输入端电连接,所述第二集成电容的第二端接地。

26、根据本发明的一些实施例,所述分段电流控制数模转换器将m+n位的数模转换器划分为m位的msb模块和n位的lsb模块,且所述msb模块与所述lsb模块之间设置有一位冗余位,所述msb模块的电流镜尺寸为所述lsb模块的电流镜尺寸的2n倍,所述msb模块用于获取所述二阶连续时间噪声整形sar量化器输出的数字码的最高位,所述lsb模块用于获取所述二阶连续时间噪声整形sar量化器输出的数字码的最低位,m和n均为正整数。

27、根据本发明的一些实施例,所述直流与交流耦合负电阻模块包括:

28、第一mos管,所述第一mos管的栅极连接第一差分输入信号;

29、第二mos管,所述第二mos管的栅极连接所述第一差分输入信号,所述第二mos管的漏极与所述第一mos管的源极电连接,且所述第二mos管的漏极及所述第一mos管的源极均通过第五电容连接第一输出端口;

30、第三mos管,所述第三mos管的栅极连接第二差分输入信号,所述第三mos管的漏极与所述第一mos管的漏极电连接,且所述第三mos管的漏极及所述第一mos管的漏极均连接电源;

31、第四mos管,所述第四mos管的栅极连接所述第二差分输入信号,所述第四mos管的漏极与所述第三mos管的源极电连接,且所述第四mos管的漏极及所述第三mos管的源极均通过第六电容连接第二输出端口,所述第四mos管的源极与所述第二mos管的源极电连接,且所述第四mos管的源极及所述第二mos管的源极均接地;

32、所述直流与交流耦合负电阻模块通过所述第一输出端口和所述第二输出端口与所述分段电流控制数模转换器的输出端及所述单运算放大器双二阶环路滤波器的输入端电连接。

33、另一方面,根据本发明实施例的模数转换方法,基于上述方面实施例所述的无过量环路时延补偿的连续时间σ-δ调制器,所述方法包括:

34、模拟输入信号与所述分段电流控制数模转换器的输出相减后,输入到所述单运算放大器双二阶环路滤波器进行积分;

35、所述单运算放大器双二阶环路滤波器输出积分后的信号到所述二阶连续时间噪声整形sar量化器;

36、所述二阶连续时间噪声整形sar量化器对积分后的信号进行模数转换,输出数字码,并将所述数字码反馈到所述分段电流控制数模转换器;

37、所述分段电流控制数模转换器按最高位和最低位分别获取所述数字码,并对所述数字码进行数模转换,并输出转换后的模拟信号;

38、所述直流与交流耦合负电阻模块提供额外电流对所述单运算放大器双二阶环路滤波器的运算放大器的带宽进行补偿,所述额外电流与所述模拟信号一同输入到所述单运算放大器双二阶环路滤波器。

39、另一方面,根据本发明实施例的电子设备,包括:

40、存储器,用于存储程序指令;

41、处理器,用于调用所述存储器中存储的程序指令,按照获得的程序指令执行上述方面实施例的模数转换方法。

42、另一方面,根据本发明实施例的存储介质,所述存储介质存储有计算机可执行指令,所述计算机可执行指令用于使计算机执行上述方面实施例所述的模数转换方法。

43、根据本发明实施例的无过量环路时延补偿的连续时间σ-δ调制器、模数转换方法、电子设备和存储介质,至少具有如下有益效果:传统的σ-δ调制器,一般采用离散时间的sar adc作为量化器,因此,量化器输出延时需要加上数字码位数个sar周期的环路延迟,而本发明实施例采用的二阶连续时间噪声整形sar量化器200,能够将其输出延时缩短至1个sar周期,因此不需要对额外环路延迟进行补偿,也就无需引入eldc。本发明提出了一种没有eldc的ct sdm,使用一种连续时间逐次逼近型模数转换器(sar adc)作为量化器,将量化器的输出延时缩短至1个sar周期,因此不需要对额外环路延迟进行补偿;同时,使用了直流与交流耦合负电阻模块的负电阻技术,在低能耗的基础上降低了对环路滤波器的运算放大器的性能要求,以缓解对环路滤波器的运算放大器的带宽要求。

44、本发明的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

- 还没有人留言评论。精彩留言会获得点赞!