一种全局曝光低噪声高速三维传感器锁相像素及读出方式的制作方法

[0001]

本发明涉及图像传感器领域,特别涉及一种能够实现全局曝光低噪声高速三维传感器锁相像素及读出方式。

背景技术:

[0002]

传感器作为人类感官的延伸,实现了对外界信息准确可靠的获取和转换。cmos图像传感器更是在各种领域发挥着重要作用。近年来,对三维图像传感器的需求有所增加,在工业领域可用于三维重建、自动加工、高度测量等;在军事领域可用于无人机侦查、潜艇水下领航、星际遥测成像等;在汽车领域可用于无人驾驶,辅助驾驶;在消费电子中,应用于体感游戏、手势识别等。基于飞行时间(tof)的三维图像传感器由于成像系统较为简单,具有更为广阔的应用前景。基于方波调制光信号的3d图像传感器原理如图1所示,光源发生器发射经调制的光信号,经过往返距离延迟后,到达探测器的相位发生改变,通过测量调制光飞行时间t

flight

的变化,根据式1计算得到目标距离信息l,即根据飞行时间的测量原理,需要在一个光波调制周期完成三或四次采样,以获得相位变化信息,三相位积分示意图如图2所示,调制光周期为tmod,三个相位分别为0,tmod/3,2tmod/3,在三个相位处的积分结果分别为q1,q2,q3,进而通过计算获得距离信息。根据积分结果可以得到所探测距离如式2所示:在获取相位变化信息时,为降低误差需要对反射光信号的每一相位均进行多次采样并累加。若每一帧读取一个相位的采样信号,连续的采样三或四帧,必然使帧频下降,在拍摄运动物体时造成成像质量的明显下降。同时由于传统的三维图像传感器受读出电路速度影响,常采用滚筒曝光模式。在该曝光模式下,传统的三维图像传感器的曝光过程与普通图像传感器中的3t像素相类似,因此无法抑制像素中的复位噪声,从而导致传感器精度下降。

技术实现要素:

[0003]

针对现有技术存在的问题,本发明提出一种全局曝光低噪声高速三维传感器锁相像素及读出方式。该像素可以采用全局曝光方式,可以有效抑制图像畸变。该像素的读出过程与普通图像传感器中的4t像素相类似,可以使用相关双采样技术抑制复位噪声。该像素中感光部分采用一种新型结构,可以有效促进电荷转移效率,提高成像帧频。

[0004]

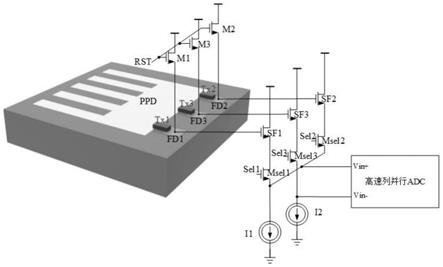

一种全局曝光低噪声高速三维传感器锁相像素结构,如图3所示,其主要由nmos管m1~m3,光电二极管photo-detector,nmos管sf1~sf3,nmos管msel1~msel3,尾电流源i1、i2,双输入高速列并行adc组成;各个组件的连接关系如下:nmos管m1~m3的源极均接电源vdd,栅极均接在rst信号,漏极分别接光电二极管photo-detector的fd1~fd3;nmos管sf1~sf3的

源极均接电源vdd,栅极分别光电二极管photo-detector的fd1~fd3相连接,源极分别与nmos管msel1~msel3的漏极相连;nmos管msel1~msel3的栅极分别与控制信号sel1~sel3相连,msel1的源极与msel2的源极相连,并同时尾电流源i1的正端、高速列并行adc的vin+端相连,msel3的源极与尾电流源i2的正端、高速列并行adc的vin-端相连。电流源i1、i2的负端均与地相连。

[0005]

一种全局曝光低噪声高速三维传感器锁相像素结构实现方法:为了提高像素中光生电荷的转移效率以及速度,通过构建内部电场的方法来加速电荷的转移。感光区采用梳状ppd结构,以加快ppd区光生电荷向fd区转移速度,避免积分时间内电荷转移不完全的问题。像素采用一种单侧三fd的结构,节点fd1、fd2和fd3可收集三个不同相位处的光生电荷,进而在一帧时间内直接输出所需的全部相位差信息,进而获取深度信息,从而有效提高传感器的成像速度。

[0006]

低误差锁相像素的实现方法:根据误差传递函数,可得到:其中a为调制光反射后的最大光强,b为背景光强度,n为积分次数,c为光速。根据探测距离误差传递函数式3推导,分别计算三相位与四相位获得深度信息的方法的探测误差,如式4与式5所示,三相位获取深度信息的方法,相较于四相位,具有更小的探测误差。式4与式5所示,三相位获取深度信息的方法,相较于四相位,具有更小的探测误差。

[0007]

通过如图4的时序控制下,两套源级跟随器电路实现空间上的双采样读出。通过优化后的复位时序可以有效降低复位电路引入的ktc噪声。采用全差分cds电路在时间上进行双采样操作,有效降低源极跟随器的非一致性,因此采用该结构可以有效降低像素的复位噪声和非一致性。

[0008]

一种全局曝光低噪声高速三维传感器锁相像素及读出方式,具有更快速的成像性能,更高的成像精度,更低的ktc噪声,进而扩大3d图像传感器的使用场合。

附图说明

[0009]

图1是基于方波调制光信号的3d图像传感器原理图;图2是基于飞行时间三维图像传感器的三相位积分示意图;图3是本发明提出一种采用全局曝光模式的低噪声高速三维图像传感器锁相像素结构及读出电路;图4是所提出像素结构的读出电路控制时序;图5是实例中所使用的两级cyclic adc原理图;

图6是实例中所使用的两级cyclic adc工作时序。

具体实施方式

[0010]

为使本发明的目的、技术方案和优点更加清晰,下面将结合实例给出本发明实施方式的具体描述。

[0011]

在该实例中,本发明设计像素尺寸为10um

×

10um,其中填充因子为40%,fd1~fd3尺寸为1.5um2,调制光源为占空比1:3,周期t

mod

=250ns,平均功率为1w的方波。读出电路采用双输入两级14bit cyclic adc原理图如图5所示,总体数据转换率为100ksps。本发明所采用的两级cyclic adc控制时序如图6所示,对于第一级cyclic adc,完成对cds输出信号的采集并同时完成最高位的量化,经过5次循环后第一级cyclic adc将完成高5位的数据转换。在第一级cyclic adc进行第5次循环时,第二级cyclic adc开始对第一级cyclic adc的输出信号进行采样,经过9个循环周期后完成低9位的数据转换。第一级cyclic adc和第二级cyclic adc的数据转换是以流水线形式开展的,因此第一级的转换时间等于第二级的转换时间也即整体adc的转换时间。本发明所采用的cyclic adc通过增加一个采样电容实现了半周期数据转换,也即每半个时钟周期即可完成1bit的数据转换,所以整体adc完成一次完整的数据转换仅需2.5个时钟周期。第一级cyclic adc的每个循环用时设为25ns;第二级cyclic adc的信号采样用时35s,之后每个循环用时均为10ns。本发明可实现60fps的输出帧频,有效降低噪声500uv。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1