一种具有四簇保守混沌流的广义Sprott-A系统及其电路实现的制作方法

一种具有四簇保守混沌流的广义sprott-a系统及其电路实现

技术领域

[0001]

本发明涉及一种三维广义sprott-a系统及电路实现,特别涉及一种具有四簇保守混沌流的广义sprott-a系统及其电路实现。

背景技术:

[0002]

随着网络技术的发展和信息交换的日益频繁,信息安全技术的研究变得越来越重要。密码学发展几千年来,在社会上应用非常广泛,20世纪80年代,非线性混沌理论开始发展并且日益壮大。混沌作为一种特有非线性现象,有许多值得利用的性质,如具有良好的伪随机性、轨道的不可预测性、对初始状态及结构参数的极端敏感性等一系列优良特性,这些特性与密码学的许多要求是相吻合的,这使得混沌密码学研究得到了广泛关注。当前的混沌密码技术都运用耗散系统,而耗散混沌系统的运动可能局限在吸引子结构内,使得其在实际应用中存在很多隐患。对于保守混沌系统而言,不存在吸引子,使得攻击者无法通过截获的密文对系统进行重构预测,因而具有较高的安全性,更适合在密码学中的应用。本发明提出一种具有四簇保守混沌流的广义sprott-a系统,该系统在混沌密码学领域具有潜在的应用价值。

技术实现要素:

[0003]

本发明要解决的技术问题是提供一种具有四簇保守混沌流的广义sprott-a系统及其电路实现,本发明采用如下技术手段实现发明目的:

[0004]

1.一种具有四簇保守混沌流的广义sprott-a系统的构建方法,其特征是在于,包括以下步骤:

[0005]

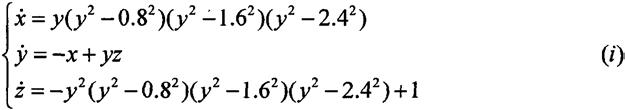

(1)具有四簇保守混沌流的广义sprott-a系统(i)为:

[0006][0007]

(2)基于系统(i)构造的电路,其特征是在于:该电路由三个主通道电路与一个辅助通道电路组成:第一主通道电路由直流电压源vcc、直流电压源vdd、运算放大器u1a、运算放大器u1b以及电阻r1、电阻r2、电阻r3、电阻r4、电阻r5、电阻r6和电容c1组成,第二主通道电路由直流电压源vcc、直流电压源vdd、运算放大器u2a、运算放大器u2b以及电阻r7、电阻r8、电阻r9、电阻r10和电容c2组成,第三主通道电路由直流电压源vcc、直流电压源vdd、电池组v1、运算放大器u3a、运算放大器u3b以及电阻r11、电阻r12、电阻r13、电阻r14、电阻r15、电阻r16、电阻r17和电容c3组成,辅助通道电路由乘法器a1、乘法器a2、乘法器a3、乘法器a4、乘法器a5、乘法器a6、乘法器a7、乘法器a8组成。

[0008]

2.所述辅助通道电路中乘法器a3的输出通过电阻r2与第一主通道电路中的运算放大器u1a的负输入端相连;辅助通道电路中乘法器a5的输出通过电阻r3与第一主通道电路中的运算放大器u1a的负输入端相连;辅助通道电路中乘法器a7的输出通过电阻r4与第

一主通道电路中的运算放大器u1a的负输入端相连;运算放大器u1a的输出通过电容c1与运算放大器u1a的负输入端相连;运算放大器u1a的输出通过电阻r7与第二主通道电路中的运算放大器u2a的负输入端相连;运算放大器u1a的输出通过电阻r5与第一主通道电路中的运算放大器u1b的负输入端相连;运算放大器u1a的正输入端接地;运算放大器u1b的输出通过电阻r6与运算放大器u1b的负输入端相连;运算放大器u1b的正输入端接地;运算放大器u1b的负电源端接直流电压源vdd;运算放大器u1b的正电源端接直流电压源vcc。

[0009]

3.所述辅助通道电路中乘法器a1的输出通过电阻r8与第二主通道电路中的运算放大器u2a的负输入端相连;运算放大器u2a的输出通过电容c2与运算放大器u2a的负输入端相连;运算放大器u2a的输出通过电阻r1与第一主通道电路中运算放大器u1a的负输入端相连;运算放大器u2a的输出与辅助通道电路中乘法器a2的一个输入端相连;运算放大器u2a的输出与辅助通道电路中乘法器a3的一个输入端相连;运算放大器u2a的输出与辅助通道电路中乘法器a5的一个输入端相连;运算放大器u2a的输出通过电阻r9与第二主通道电路中运算放大器u2b的负输入端相连;运算放大器u2a的正输入端接地;运算放大器u2b的输出通过电阻r10与运算放大器u2b的负输入端相连;运算放大器u2b的输出与辅助通道电路中乘法器a1的一个输入端相连;运算放大器u2b的输出与辅助通道电路中乘法器a2的一个输入端相连;运算放大器u2b的输出与辅助通道电路中乘法器a4的一个输入端相连;运算放大器u2b的正输入端接地;运算放大器u2b的负电源端接直流电压源vdd;运算放大器u2b的正电源端接直流电压源vcc。

[0010]

4.所述辅助通道电路中乘法器a2的输出通过电阻r11与第三主通道电路中的运算放大器u3a的负输入端相连;辅助通道电路中乘法器a4的输出通过电阻r12与第三主通道电路中的运算放大器u3a的负输入端相连;辅助通道电路中乘法器a6的输出通过电阻r13与第三主通道电路中的运算放大器u3a的负输入端相连;辅助通道电路中乘法器a8的输出通过电阻r14与第三主通道电路中的运算放大器u3a的负输入端相连;电池组v1的负极通过电阻r17与第三主通道电路中的运算放大器u3a的负输入端相连;电池组v1正极接地;运算放大器u3a的输出通过电容c3与运算放大器u3a的负输入端相连;运算放大器u3a的输出与辅助通道电路中乘法器a1的一个输入端相连;运算放大器u3a的输出通过电阻r16与第三主通道电路中的运算放大器u3b的负输入端相连;运算放大器u3a的正输入端接地;运算放大器u3b的输出通过电阻r15与运算放大器u3b的负输入端相连;运算放大器u3b的正输入端接地;运算放大器u3b的正电源端接直流电压源vcc;运算放大器u3b的负电源端接直流电压源vdd。

[0011]

5.所述辅助通道电路中乘法器a2的输出与辅助通道电路中乘法器a3的一个输入端相连;辅助通道电路中乘法器a2的输出与辅助通道电路中乘法器a6的一个输入端相连;辅助通道电路中乘法器a2的输出与辅助通道电路中乘法器a7的一个输入端相连;辅助通道电路中乘法器a3的输出与辅助通道电路中乘法器a4的一个输入端相连;辅助通道电路中乘法器a4的输出与辅助通道电路中乘法器a5的一个输入端相连;辅助通道电路中乘法器a4的输出与辅助通道电路中乘法器a6的一个输入端相连;辅助通道电路中乘法器a4的输出与辅助通道电路中乘法器a8的两个输入端均相连;辅助通道电路中乘法器a5的输出与辅助通道电路中乘法器a7的一个输入端相连。

附图说明

[0012]

图1为本发明优选实施例的电路连接结构示意图。

[0013]

图2为本发明的x-y相图。

具体实施方式

[0014]

下面结合附图和优选实施例对本发明作更进一步的详细描述,参见图1-图2。

[0015]

1.一种具有四簇保守混沌流的广义sprott-a系统的构建方法,其特征是在于,包括以下步骤:

[0016]

(1)具有四簇保守混沌流的广义sprott-a系统(i)为:

[0017][0018]

(2)基于系统(i)构造的电路,其特征是在于:该电路由三个主通道电路与一个辅助通道电路组成:第一主通道电路由直流电压源vcc、直流电压源vdd、运算放大器u1a、运算放大器u1b以及电阻r1、电阻r2、电阻r3、电阻r4、电阻r5、电阻r6和电容c1组成,第二主通道电路由直流电压源vcc、直流电压源vdd、运算放大器u2a、运算放大器u2b以及电阻r7、电阻r8、电阻r9、电阻r10和电容c2组成,第三主通道电路由直流电压源vcc、直流电压源vdd、电池组v1、运算放大器u3a、运算放大器u3b以及电阻r11、电阻r12、电阻r13、电阻r14、电阻r15、电阻r16、电阻r17和电容c3组成,辅助通道电路由乘法器a1、乘法器a2、乘法器a3、乘法器a4、乘法器a5、乘法器a6、乘法器a7、乘法器a8组成。

[0019]

2.所述辅助通道电路中乘法器a3的输出通过电阻r2与第一主通道电路中的运算放大器u1a的负输入端相连;辅助通道电路中乘法器a5的输出通过电阻r3与第一主通道电路中的运算放大器u1a的负输入端相连;辅助通道电路中乘法器a7的输出通过电阻r4与第一主通道电路中的运算放大器u1a的负输入端相连;运算放大器u1a的输出通过电容c1与运算放大器u1a的负输入端相连;运算放大器u1a的输出通过电阻r7与第二主通道电路中的运算放大器u2a的负输入端相连;运算放大器u1a的输出通过电阻r5与第一主通道电路中的运算放大器u1b的负输入端相连;运算放大器u1a的正输入端接地;运算放大器u1b的输出通过电阻r6与运算放大器u1b的负输入端相连;运算放大器u1b的正输入端接地;运算放大器u1b的负电源端接直流电压源vdd;运算放大器u1b的正电源端接直流电压源vcc。

[0020]

3.所述辅助通道电路中乘法器a1的输出通过电阻r8与第二主通道电路中的运算放大器u2a的负输入端相连;运算放大器u2a的输出通过电容c2与运算放大器u2a的负输入端相连;运算放大器u2a的输出通过电阻r1与第一主通道电路中运算放大器u1a的负输入端相连;运算放大器u2a的输出与辅助通道电路中乘法器a2的一个输入端相连;运算放大器u2a的输出与辅助通道电路中乘法器a3的一个输入端相连;运算放大器u2a的输出与辅助通道电路中乘法器a5的一个输入端相连;运算放大器u2a的输出通过电阻r9与第二主通道电路中运算放大器u2b的负输入端相连;运算放大器u2a的正输入端接地;运算放大器u2b的输出通过电阻r10与运算放大器u2b的负输入端相连;运算放大器u2b的输出与辅助通道电路中乘法器a1的一个输入端相连;运算放大器u2b的输出与辅助通道电路中乘法器a2的一个输入端相连;运算放大器u2b的输出与辅助通道电路中乘法器a4的一个输入端相连;运算放

大器u2b的正输入端接地;运算放大器u2b的负电源端接直流电压源vdd;运算放大器u2b的正电源端接直流电压源vcc。

[0021]

4.所述辅助通道电路中乘法器a2的输出通过电阻r11与第三主通道电路中的运算放大器u3a的负输入端相连;辅助通道电路中乘法器a4的输出通过电阻r12与第三主通道电路中的运算放大器u3a的负输入端相连;辅助通道电路中乘法器a6的输出通过电阻r13与第三主通道电路中的运算放大器u3a的负输入端相连;辅助通道电路中乘法器a8的输出通过电阻r14与第三主通道电路中的运算放大器u3a的负输入端相连;电池组v1的负极通过电阻r17与第三主通道电路中的运算放大器u3a的负输入端相连;电池组v1正极接地;运算放大器u3a的输出通过电容c3与运算放大器u3a的负输入端相连;运算放大器u3a的输出与辅助通道电路中乘法器a1的一个输入端相连;运算放大器u3a的输出通过电阻r16与第三主通道电路中的运算放大器u3b的负输入端相连;运算放大器u3a的正输入端接地;运算放大器u3b的输出通过电阻r15与运算放大器u3b的负输入端相连;运算放大器u3b的正输入端接地;运算放大器u3b的正电源端接直流电压源vcc;运算放大器u3b的负电源端接直流电压源vdd。

[0022]

5.所述辅助通道电路中乘法器a2的输出与辅助通道电路中乘法器a3的一个输入端相连;辅助通道电路中乘法器a2的输出与辅助通道电路中乘法器a6的一个输入端相连;辅助通道电路中乘法器a2的输出与辅助通道电路中乘法器a7的一个输入端相连;辅助通道电路中乘法器a3的输出与辅助通道电路中乘法器a4的一个输入端相连;辅助通道电路中乘法器a4的输出与辅助通道电路中乘法器a5的一个输入端相连;辅助通道电路中乘法器a4的输出与辅助通道电路中乘法器a6的一个输入端相连;辅助通道电路中乘法器a4的输出与辅助通道电路中乘法器a8的两个输入端均相连;辅助通道电路中乘法器a5的输出与辅助通道电路中乘法器a7的一个输入端相连。

[0023]

当然,上述说明并非对发明的限制,本发明也不仅限于上述举例,本技术领域的普通技术人员在本发明的实质范围内所做出的变化、改型、添加或替换,也属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1