一种多数据传输通道的融合装置和电子设备的制作方法

1.本技术涉及图像数据处理领域,尤其涉及到一种数据传输通道的融合装置和电子设备。

背景技术:

2.随着手机等电子设备对拍摄性能的进一步提高,摄像模组的数量以及感光芯片的像素也随之提高。目前,摄像模组的数据传输多采用移动产业处理器接口(mobile industry processor interface,mipi)。mipi中用于传输数据的物理层接口主要包括d-phy接口和c-phy接口,处理芯片和摄像模组内的感光芯片之间通过d-phy接口或c-phy接口进行图像数据的接收和发送,处理芯片对接收的图像数据进行处理得到图像。

3.实际使用时,感光芯片的接口和处理芯片的接口通过多条数据传输线连接,当电子设备需要设置多个摄像模组来满足拍摄性能的需求时,摄像模组通过多个连接器和多个数据传输线与处理芯片直接连接,以实现数据传输,但是采用上述方式传输数据会出现两个问题,一个是数量众多的数据传输线和连接器严重影响了智能终端中的印刷电路板(printed circuit board,pcb)的布局和布线,另一个是处理芯片用于接收数据的管脚有限,当数据传输线过多时,需要增加更换处理芯片,以实现增加处理芯片接收数据的管脚数量,增大了处理芯片的面积,从而增加处理芯片在pcb上的占用面积。这两个问题都会增加pcb设计难度,限制智能电子设备的系统优化空间。

4.因此,现有的图像传输架构有待进一步改进。

技术实现要素:

5.本技术提供了一种多数据传输通道的融合装置和电子设备,用于优化电子设备中的pcb的布局以及提高电子设备的优化空间。

6.第一方面,本技术实施例提供了电子设备,该电子设备可以包括:多个第一感光芯片、一个处理芯片以及一个第一融合芯片。

7.其中,每一个第一感光芯片通过一个数据传输通道与第一融合芯片连接,每一个第一感光芯片用于产生基于移动产业处理器接口mipi协议的数据流,并通过连接的数据传输通道传输给第一融合芯片;第一融合芯片通过一个数据传输通道与处理芯片连接,第一融合芯片用于将与多个第一感光芯片连接的多个数据传输通道中的数据流进行融合,得到第一高速融合数据流,并通过与处理芯片连接的一个数据传输通道将第一高速融合数据流发送给处理芯片;处理芯片用于通过连接的数据传输通道接收数据流,并利用接收的数据流得到图像。

8.采用上述电子设备结构,可以通过一个第一融合芯片将多个感光芯片产生的数据流进行融合,并通过一个数据传输通道传输给处理芯片,得到图像,在数据流的传输过程中,第一融合芯片可以通过一个数据传输通道中包含的极少的数据传输线即可将多个第一感光芯片产生的数据流传输给处理芯片,从而简化pcb的设计难度,以及优化电子设备的系

统架构。

9.在一种可能的设计中,第一融合芯片包括:融合模块、高速信号发送模块和与每一个第一感光芯片一一对应连接的接收模块。

10.其中,每一个接收模块,用于接收对应的第一感光芯片产生的数据流,并将接收的数据流输出给融合模块;融合模块分别与高速信号发送模块和各接收模块连接,融合模块用于接收各接收模块输出的数据流,并将接收的多个数据流融合为融合数据,并将融合数据输出给高速信号发送模块;高速信号发送模块与处理芯片连接,用于将接收到的融合数据转换为第一高速融合数据流后通过与处理芯片连接的一个数据传输通道发送给处理芯片。

11.采用上述电子设备结构,可以通过接收模块接收多个数据传输通道中数据流,并利用第一融合芯片将多个数据传输通道中的数据流融合后通过一个数据传输通道发送给处理芯片,从而无需在第一感光芯片与处理芯片之间连接多个数据传输通道,即可实现将多个第一感光芯片产生的数据流发送给处理芯片,从而减少用于传输多个第一感光芯片产生的数据流的数据传输线的数量。

12.在一种可能的设计中,融合模块包括:第一控制模块、多路选择器和与第一缓存模块。其中,第一缓存模块包括与每一个接收模块对应的输入端和与每一个输入端对应的输出端;

13.其中,第一缓存模块的每一个输入端与对应的接收模块连接,用于缓存连接的接收模块输出的数据流,并通过对应的输出端输出;多路选择器的多个输入端分别与第一缓存模块不同的输出端连接,多路选择器的输出端与高速信号发送模块连接,多路选择器用于将第一缓存模块缓存的多个数据流融合为融合数据后输出给高速信号发送模块;第一控制模块与多路选择器的控制端连接,第一控制模块用于控制多路选择器对第一缓存模块中缓存的多个数据流进行编号,并将编号后的多个数据流融合。

14.采用上述电子设备结构,多路选择器可以在第一控制模块的控制下,将从多个数据传输通道中接收的多个数据流进行进行融合。

15.在一种可能的设计中,融合模块还可以包括:第一数据处理模块和存储模块。

16.其中,第一数据处理模块与多路选择器的输出端连接,第一数据处理模块用于将多路选择器输出的融合数据进行处理,以及将处理后的融合数据分别输出给高速信号发送模块和存储模块;存储模块用于存储处理后的融合数据。

17.采用上述电子设备结构,可以在融合芯片将融合数据传输给高速信号发送模块之前,对融合数据进行预处理,从而增加数据处理的灵活性。

18.在一种可能的设计中,处理芯片包括:图像信号处理器、第一信号接收模块、第一分配模块和第一mipi协议处理模块。其中,

19.第一信号接收模块通过一个数据传输通道与第一融合芯片连接,用于接收第一融合芯片输出的第一高速融合数据流;第一分配模块分别与第一信号接收模块和第一mipi协议处理模块连接,第一分配模块用于接收第一信号接收模块输出的数据流,并将接收的数据流进行分配,得到多个数据流并输出给第一mipi协议处理模块;第一mipi协议处理模块与图像信号处理器连接,第一mipi协议处理模块用于接收第一分配模块输出的多个数据流,对接收的多个数据流进行处理,并将处理后的数据流输出给图像信号处理器;图像信号

处理器用于接收第一mipi协议处理模块输出的处理后的数据流,并利用接收的数据流得到图像。

20.采用上述电子设备结构,可以通过第一信号接收模块接收第一融合芯片输出的第一高速融合数据流,并利用第一分配模块对第一高速融合数据流进行分配,得到每一个第一感光芯片产生的数据流,并利用该数据流,得到最终的图像。

21.在一种可能的设计中,每一个分配模块包括:数据分配器、第二控制模块和与第二缓存模块。

22.其中,数据分配器的输入端与第一信号接收模块连接,数据分配器的多个输出端与第二缓存器连接,数据分配器用于接收第一信号接收模块输出的数据,并将接收的数据分配为多个数据流;第二缓存模块用于接收并缓存数据分配器输出的多个数据流,并将缓存的多个数据流输出给第一mipi协议处理模块;第二控制模块与数据分配器的控制端连接,第二控制模块用于控制数据分配器对数据分配器接收的数据进行分配,得到多个数据流。

23.采用上述电子设备结构,数据分配器可以在第二控制模块的控制下,将接收的第一高速融合数据流分配为多个数据流。

24.在一种可能的设计中,处理芯片和第一融合芯片之间连接有第一控制通道,处理芯片用于通过第一控制通道指示第一融合芯片控制多个第一感光芯片的工作参数,或者处理芯片和多个第一感光芯片之间连接有第二控制通道,处理芯片用于通过第二控制通道直接控制多个第一感光芯片的工作参数。

25.采用上述电子设备结构,处理芯片可以直接调整多个第一感光芯片的工作参数,也可以通过第一融合芯片控制多个第一感光芯片的工作参数。

26.采用上述电子设备结构,处理芯片可以调整多个第一感光芯片的工作参数,从而控制多个第一感光芯片产生特定参数的数据流。

27.在一种可能的设计中,本技术实施例提供的电子设备还可以包括:多个第二感光芯片和至少一个第二融合芯片。其中,每一个第二感光芯片通过一个数据传输通道与至少一个第二融合芯片中的一个第二融合芯片连接,每一个第二感光芯片用于产生基于mipi协议的数据流,并通过传输通道传输给连接的第二融合芯片;每一个第二融合芯片通过一个数据传输通道与处理芯片连接,每一个第二融合芯片用于将与连接在第二感光芯片之间的多个数据传输通道中的数据流进行融合,得到第二高速融合数据流,并通过与处理芯片连接的一个数据传输通道将第二高速融合数据流发送给处理芯片。

28.其中,处理芯片还包括:与每一个第二融合芯片一一对应的第二信号接收模块、与每一个第二信号接收模块一一对应的第二分配模块和与每一个第二分配模块一一对应的第二mipi协议处理模块。其中,每一个第二信号接收模块用于通过一个数据传输通道与对应的第二融合芯片连接,用于接收连接的第二融合芯片输出的第二高速融合数据流;每一个第二分配模块与对应的第二信号接收模块和对应的第二mipi协议处理模块连接,每一个第二分配模块用于接收连接的第二信号接收模块输出的数据,并将接收的数据进行分配,得到多个数据流并输出给连接的第二mipi协议处理模块;每一个第二mipi协议处理模块与图像信号处理器连接,每一个第二mipi协议处理模块用于接收连接的第二分配模块输出的多个数据流,对接收的多个数据流进行处理,并将处理后的数据流输出给图像信号处理器。

29.采用上述电子设备结构,在第一融合芯片的接口数量有限,或者感光芯片的空间分布限制,可以根据感光芯片的安装位置,设置多个融合芯片,来满足电子设备的数据传输需求。

30.第二方面,本技术实施例提供了一种多数据传输通道的融合装置,该装置包括:本技术实施例第一方面以及任一可能的设计中提供的第一融合芯片。其中,第一融合芯片用于将与多个第一感光芯片连接的多个数据传输通道中的数据流进行融合,得到第一高速融合数据流,并通过与处理芯片连接的一个数据传输通道发送给处理芯片。

31.采用上述装置结构,可以通过一个数据传输通道将多个数据传输通道中的数据流传输给处理芯片,减少了数据传输通道的数量,从而减少了数据传输线的数量。

32.在一种可能的设计中,该装置该包括:至少一个第二融合芯片。其中,每一个第二融合芯片用于通过多个数据传输通道与多个第二感光芯片连接,以及通过一个数据传输通道与处理芯片连接;每一个第二融合芯片用于将与多个第二感光芯片连接的多个数据传输通道中的数据流进行融合,得到第二高速融合数据流,并通过与处理芯片连接的数据传输通道发送给处理芯片。

33.采用上述装置结构,在第一融合芯片的接口数量有限,以及感光芯片的空间分布限制,可以根据感光芯片的安装位置,设置融合芯片的数量和位置,来满足数据传输需求。

34.第三方面,本技术实施例提供了一种数据传输方法,该方法的执行主体可以是本技术实施例第二方面提供以及任一可能的设计中提供的多数据传输通道的融合装置。具体地,包括以下步骤:获取与多个感光芯片连接的数据传输通道中的数据流;将获取的多个数据流融合为至少一个高速融合数据流,并将至少一个高速融合数据流发送给处理芯片。

35.采用上述方法,可以将多个感光芯片产生的多个数据流融合后传输,减小用于传输多个感光芯片产生的数据流的数据传输线的数量,且对数据流进一步融合,并提高数据的传输速度。

36.在一种可能的设计中,将获取的多个数据流融合为至少一个高速融合数据流,包括:将获取的多个数据流进行编号,并将编号后的多个数据流进行融合,得到至少一个高速融合数据流。

37.采用上述方法,可以对多个数据流进一步融合,得到高速融合数据流,从而减少用于传输多个数据流的数据传输通道的数量。

38.在一种可能的设计中,获取与每一个感光芯片连接的数据传输通道中的数据流之前,本技术实施例提供的多数据传输通道的融合方法还包括:

39.接收处理芯片发送的控制信号,并响应与该控制信号调整连接的多个感光芯片的工作参数。

40.采用上述方法,可以根据处理芯片发送的控制信号,输出符合要求的数据流。

41.第四方面,本技术实施例提供了一种数据处理方法,该方法的执行主体可以是本技术实施例第一方面及其任一可能的设计中提出的电子设备中的处理芯片。具体可以包括以下步骤:接收至少一个高速融合数据流,每一个高速融合数据流中包括多个感光芯片产生的多个数据流;将接收的至少一个高速融合数据分配为多个数据流;对多个数据流进行处理,得到图像。

42.采用上述方法,可以通过极少的数据传输线接收包含多个感光芯片产生的数据流

的至少一个高速融合数据流,并对接收的高速融合数据流进行处理,得到图像。

43.在一种可能的设计中,将接收的至少一个高速融合数据流分配为多个数据流,包括;对至少一个高速融合数据流进行时钟恢复;利用至少一个高速融合数据流中的编号标识,对时钟恢复后的至少一个高速融合数据流进行分配,得到每一个感光芯片对应的数据流。

44.采用上述方法,可以基于高速融合数据流中的编号标识,对高速融合数据流进行分配,从而得到每一个感光芯片对应的数据流,以便于处理芯片对数据流进行处理,得到图像。

45.在一种可能的设计中,在接收至少一个高速融合数据流之前,本技术实施例提供的数据处理方法还包括:

46.向多个感光芯片发送控制信号。其中,该控制信号用于控制多个感光芯片的工作参数,以使多个感光芯片产生数据流。

47.采用上述方法,可以通过调整多个感光芯片的工作参数,实现得到满足要求的数据流。

附图说明

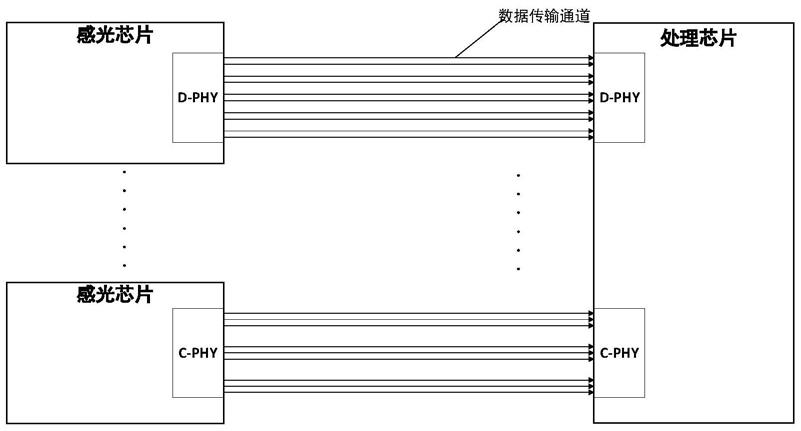

48.图1为一种应用场景的结构示意图;

49.图2为本技术实施例一种电子设备的结构示意图;

50.图3为本技术实施例一种第一融合芯片的结构示意图;

51.图4为本技术实施例一种融合模块的结构示意图;

52.图5为本技术实施例一种处理芯片的结构示意图;

53.图6为本技术实施例一种第一分配模块的结构示意图;

54.图7为本技术实施例一种多数据传输通道的融合装置的结构示意图;

55.图8为本技术实施例一种数据传输方法的流程示意图;

56.图9为本技术实施例一种数据处理方法的流程示意图;

57.图10为本技术实施例一种电子设备的数据处理的具体流程示意图。

具体实施方式

58.本技术实施例提供的多数据传输通道的融合装置和电子设备可以应用于手机和平板等智能终端中,还可以应用于无人机、自动驾驶系统、安防系统等技术领域。

59.目前,电子设备的结构框图如图1所示,在图1中,电子设备中包括多个感光芯片、多个数据传输通道以及处理芯片。其中,每一个感光芯片和处理芯片分别通过一个数据传输通道连接,以实现将感光芯片产生的数据流通过连接的数据传输通道传输给处理芯片,处理芯片通过多个数据传输通道接收到多个感光芯片产生的数据流,并对接收的多个数据流进行处理,得到图像,并通过电子设备的显示屏幕(未示出)显示该图像。其中,每一个数据传输通道中均存在多条数据传输线。其中,在一些应用场景中,处理芯片和感光芯片之间连接有连接器。

60.在实际应用中,感光芯片主要通过设置的d-phy接口和c-phy接口与数据传输通道连接,与每一个d-phy接口连接的数据传输通道通常具有10条数据传输线,与每一个c-phy

接口连接的数据传输通道通常具有9条数据传输线。随着电子设备对拍摄性能要求的逐渐提高,电子设备中感光芯片的数量也在逐渐增多,感光芯片的增加会导致数据传输通道数量的增多,同时,处理芯片也需要增加对应的数据接收接口以及增加连接在处理芯片和感光芯片的连接器的数量,才能实现接收到新增加的感光芯片产生的数据流。而增加的器件会造成数据传输线、连接器以及处理芯片在电子设备中的pcb上的占用面积增加,从而影响pcb的布局和布线,当电子设备增加新的功能时,pcb也无法为新增加的功能提供相应的位置,从而限制了电子设备的优化空间。

61.因此,现有技术中的电子设备在传输感光芯片产生的数据流时,增加了pcb的设计难度以及限制了电子设备的优化空间。因此,本技术实施例提供了一种多数据传输通道的融合装置和电子设备,用于简化pcb的设计难度以及优化电子设备的系统架构。

62.本技术实施例中“或”,描述关联对象的关联关系,表示可以存在两种关系,例如,a或b,可以表示:单独存在a,单独存在b的情况,其中a、b可以是单数或者复数。

63.本技术中所涉及术语“连接”,描述两个对象的连接关系,可以表示两种连接关系,例如,a和b连接,可以表示:a与b直接连接,a通过c和b连接这两种情况。

64.在本技术实施例中,“示例的”“在一些实施例中”“在另一实施例中”等用于表示作例子、例证或说明。本技术中被描述为“示例”的任何实施例或设计方案不应被解释为比其它实施例或设计方案更优选或更具优势。确切而言,使用示例的一词旨在以具体方式呈现概念。

65.需要指出的是,本技术实施例中涉及的“第一”、“第二”等词汇,仅用于区分描述的目的,而不能理解为指示或暗示相对重要性,也不能理解为指示或暗示顺序。本技术实施例中涉及的等于可以与大于连用,适用于大于时所采用的技术方案,也可以与小于连用,适用于与小于时所采用的技术方案,需要说明的是,当等于与大于连用时,不与小于连用;当等于与小于连用时,不与大于连用。

66.参见图2为本技术实施例提供的一种电子设备的结构示意图。该电子设备200包括多个第一感光芯片201、一个第一融合芯片202以及一个处理芯片203。

67.其中。每一个第一感光芯片201通过一个数据传输通道与第一融合芯片202连接,第一融合芯片202通过一个数据传输通道与处理芯片203连接。

68.其中,每一个第一感光芯片201可以用于产生基于移动产业处理器接口mipi协议的数据流,并通过连接的数据传输通道传输给第一融合芯片;第一融合芯片202用于将与多个第一感光芯片201连接的多个数据传输通道中的数据流进行融合,得到第一高速融合数据流,并通过与处理芯片203连接的一个数据传输通道将第一高速融合数据流发送给处理芯片203;处理芯片203用于通过连接的数据传输通道接收数据流,并利用接收的数据流得到图像。

69.实际使用时,电子设备200中的多个感光芯片201和处理芯片203可以设置在电子设备200中的同一pcb上,也可以设置在电子设备200中不同的pcb上,若多个感光芯片201和处理芯片203设置在不同的pcb上,则本技术实施例中与多个感光芯片201连接的第一融合芯片202优先设置在多个感光芯片对应的pcb上,以减少第一融合芯片202与多个感光芯片201之间的数据传输通道中的多条数据传输线的长度,实现减少数据传输线在pcb上的占用面积,从而简化pcb的设计难度,优化电子设备的系统架构。

70.在一示例中,当电子设备200中包含的多个感光芯片之间的距离较近时,可以使用一个第一融合芯片202与电子设备200中所有的第一感光芯片连接,以实现通过一个第一融合芯片201接收电子设备中所有感光芯片产生的数据流,从而减少电子设备中器件的数量以及减少融合芯片在pcb上的占用面积。

71.在另一示例中,当电子设备中包含的多个感光芯片之间的距离较远时,可以根据电子设备中感光芯片的安装位置选择电子设备200融合芯片的数量以及融合芯片在电子设备pcb上设置的位置,从而避免处理芯片203所在pcb上的数据传输线过多,占用处理芯片203所在pcb上较多的面积,增加pcb的设计难度。

72.第一融合芯片202用于融合多个第一感光芯片201产生的数据流时,多个第一感光芯片201与第一融合芯片202连接,第一融合芯片202与处理芯片203连接,第一融合芯片202将与多个数据传输通道中的数据流融合为高速融合数据,并通过与处理芯片203连接的一个数据传输通道传输给处理芯片。

73.下面,对第一融合芯片202和处理芯片203的具体结构进行介绍。

74.一、第一融合芯片202

75.第一融合芯片202通过多个数据传输通道分别与不同的第一感光芯片201连接,第一融合芯片202还通过一个数据传输通道与处理芯片203连接,第一融合芯片202用于将与多个第一感光芯片201连接的多个数据传输通道中的数据流进行融合,得到第一高速融合数据流,并通过与处理芯片203连接的一个数据传输通道将第一高速融合数据流发送给处理芯片。

76.具体地,如图3所示,第一融合芯片202可以包括:融合模块2021、高速信号发送模块2022和与每一个第一感光芯片201一一对应连接的接收模块2023。其中,每一个接收模块2023可以用于接收对应连接的第一感光芯片201产生的数据流,并将接收的数据流输出给融合模块2021;融合模块2021分别与高速信号发送模块2022和各接收模块2023连接,融合模块2022可以用于接收各接收模块2023输出的数据流,并将接收的多个数据流融合为融合数据,并将融合数据输出给高速信号发送模块2022;高速信号发送模块2022可以与处理芯片203连接,用于将接收到的融合数据转换为第一高速融合数据流后通过与处理芯片203连接的一个数据传输通道发送给处理芯片203。

77.具体地,若第一感光芯片201通过d-phy接口传输数据,则对应连接的接收模块2023为d-phy接收模块,若第一感光芯片201通过c-phy接口传输数据,则对应连接的接收模块为c-phy接收模块。

78.实际应用时,第一融合芯片202的各接收模块2023通过一个数据传输通道与对应的第一感光芯片201连接。具体实现时,第一融合芯片202的各接收模块2023上可以设置有多个固定管脚,第一感光芯片201可以通过一个数据传输通道以及第一融合芯片202的接收模块2023上的多个固定管脚与第一融合芯片202连接。

79.需要说明的是,第一融合芯片202的各接收模块2023设置的管脚数量可以根据与该接收模块2023连接的第一感光芯片201上用于传输数据的接口类型来设置。例如,若与该接收模块2023连接的第一感光芯片201通过d-phy接口传输数据,则该接收模块2023上的管脚数量为可以为10;若与该接收模块2023连接的第一感光芯片通过c-phy接口传输数据,则该接收模块2023上的管脚数量为9。其中,连接在接收模块2023和第一感光芯片201之间的

数据传输通道中的数据传输线的数量与该接收模块2023上管脚的数量相同。

80.具体使用时,第一感光芯片201产生的数据流通过mipi协议处理模块进行传输,第一融合芯片202通过数据传输通道接收到第一感光芯片201输出的数据流之前,第一感光芯片201中的mipi协议处理模块先将第一感光芯片采集的数据转换为csi-2数据流后,通过数据传输通道传输给第一融合芯片202,第一融合芯片202中的每一个接收模块2023通过多个管脚接收连接数据传输通道中的第一感光芯片201产生的数据流。其中,接收模块2023可以为d-phy接收模块和c-phy接收模块。其中,该数据流包括包头和包尾。

81.具体地,如图4所示,融合模块2021可以包括:第一控制模块20211、多路选择器20212和与第一缓存模块20213。其中,第一缓存模块20213包括与每一个接收模块2023对应的输入端和与每一个输入端对应的输出端。

82.具体地,第一缓存模块20213的每一个输入端与对应的接收模块2023连接,用于缓存连接的接收模块2023输出的数据流,并通过对应的输出端输出。多路选择器20212的输入端分别与第一缓存模块20213不同的输出端连接,多路选择器20212的输出端与高速信号发送模块2022连接,多路选择器20212可以用于将第一缓存模块20213中缓存的多个数据流融合为融合数据后输出给高速信号发送模块2022。第一控制模块20211与多路选择器20212的控制端连接,第一控制模块20211可以用于控制多路选择器20212对第一缓存模块20213中缓存的多个数据流进行编号,并将编号后的多个数据流融合。

83.应理解,为了增加数据处理的灵活性,本技术实施例提供的融合模块2021还包括:第一数据处理模块20214和存储模块20215,用于对融合数据进行数据预处理。其中,第一数据处理模块20214可以是但不限于图像处理单元。

84.具体地,第一数据处理模块20214与多路选择器20212的输出端连接,第一数据处理模块20214可以用于将多路选择器20212输出的融合数据进行处理,以及将处理后的融合数据分别输出给高速信号发送模块2022和存储模块20215;存储模块20215可以用于存储处理后的融合数据。

85.应理解,若由于第一融合芯片的设置的接收模块的数量有限,以及电子设备200中包括多个设置在不同位置的感光芯片时,为了保证处理芯片203可以获取到所有的感光芯片产生的数据流,在电子设备200中包括多个第二感光芯片时,电子设备200中还包括至少一个第二融合芯片。

86.其中,每一个第二感光芯片通过一个数据传输通道与至少一个第二融合芯片中的一个第二融合芯片连接,每一个第二感光芯片用于产生基于mipi协议的数据流,并通过传输通道传输给连接的第二融合芯片;每一个第二融合芯片通过一个数据传输通道与处理芯片连接,每一个第二融合芯片用于将与连接在第二感光芯片之间的多个数据传输通道中的数据流进行融合,得到第二高速融合数据流,并通过与处理芯片连接的一个数据传输通道将第二高速融合数据流发送给处理芯片。

87.应理解,第二融合芯片的结构与本技术实施例提供的第一融合芯片201的结构相同,本技术实施例不做重复介绍。

88.二、处理芯片203

89.处理芯片203通过一个数据传输通道与第一融合芯片201连接,并用于通过连接的数据传输通道接收数据流,并利用接收的数据流得到图像。

90.具体地,如图5所示,处理芯片203具体包括:图像信号处理器2031、第一信号接收模块2032、第一分配模块2033和第一mipi协议处理模块2034。

91.具体地,第一信号接收模块2032通过一个数据传输通道与第一融合芯片202连接,可以用于接收第一融合芯片202输出的第一高速融合数据流;第一分配模块2033分别与第一信号接收模块2032和第一mipi协议处理模块2034连接,第一分配模块2033可以用于接收第一信号接收模块2032输出的数据流,并将接收的数据流进行分配,得到多个数据流并输出给连接的第一mipi协议处理模块2034;第一mipi协议处理模块2034可以与图像信号处理器2031连接,第一mipi协议处理模块2034可以用于接收第一分配模块2033输出的多个数据流,并对接收的多个数据流进行处理,并将处理后的数据流输出给图像信号处理器2031;图像信号处理器2031可以用于接收第一mipi协议处理模块2034输出的处理后的数据流,并利用接收的处理后的数据流得到图像。

92.具体地,本技术实施例提供处理芯片还可以包括时钟恢复模块,时钟恢复模块分别与第一信号接收模块2032和第一分配模块2033连接,时钟恢复模块可以用恢复第一信号接收模块2032接收的高速融合数据流的时钟信号。

93.在一示例中,电子设备200中的处理芯片203可以通过高速串行接口与第一融合芯片202的输出连接。

94.具体使用时,第一感光芯片201输出的数据流为经过mipi协议处理模块处理后的数据,处理芯片203接收的第一融合芯片输出的高速融合数据流为mipi数据包,图像信号处理器2031无法对该数据流直接进行处理,因此,在第一分配模块2033在将高速融合数据流分配为多个数据流之后,将数据流传输至图像信号处理器2031之前,需要先通过第一mipi协议处理模块2034去掉数据流的包头和包尾,以便于图像信号处理器2031对处理后的数据流处理,得到图像。

95.其中,如图6所示,第一分配模块2033可以包括:数据分配器20331、第二控制模块和20332与第二缓存模块20333。

96.具体地,数据分配器20331的输入端与第一信号接收模块2032连接,数据分配器20331的多个输出端与第二缓存模块20333连接,数据分配器20331可以用于接收对一信号接收模块2032输出的数据流,并将接收的数据分配为多个数据流;第二缓存模块20333用于接收并缓存数据分配器20331的输出端输出的多个数据流,并将缓存的多个数据流输出给第一mipi协议处理模块2034;第二控制模块20332与数据分配器20331的控制端连接,第二控制模块20332可以用于控制数据分配器520331对数据分配器20331接收的数据的进行分配,得到多个数据流。

97.可选地,处理芯片203与第一融合芯片202之间连接有第一控制通道,处理芯片203用于通过第一控制通道以指示第一融合芯片202控制与该融合芯片连接的第一感光芯片201的工作参数。其中,该工作参数可以包括但不限于:像素、曝光时间、帧率和色深。

98.可选地,本技术实施例提供的处理芯片203与多个第一感光芯片201之间连接有第二控制通道,处理芯片203用于通过第二控制通道直接控制多个第一感光芯片201的工作参数。

99.应理解,当电子设备200中包括多个第二感光芯片和至少一个第二融合芯片时,处理芯片203还包括:与每一个第二融合芯片一一对应的第二信号接收模块、与每一个第二信

号接收模块一一对应的第二分配模块和与每一个第二分配模块一一对应的第二mipi协议处理模块。

100.具体地,每一个第二信号接收模块用于通过一个数据传输通道与对应的第二融合芯片连接,用于接收连接的第二融合芯片输出的第二高速融合数据流;每一个第二分配模块与对应的第二信号接收模块和对应的第二mipi协议处理模块连接,每一个第二分配模块用于接收连接的第二信号接收模块输出的数据,并将接收的数据进行分配,得到多个数据流并输出给连接的第二mipi协议处理模块;每一个第二mipi协议处理模块与图像信号处理器2031连接,每一个第二mipi协议处理模块用于接收连接的第二分配模块输出的多个数据流,对接收的多个数据流进行处理,并将处理后的数据流输出给图像信号处理器2031。

101.其中,第二信号接收模块与本技术前述实施例提供的第一信号接收模块的结构相同,第二分配模块的结构与本技术实施例提供的第一分配模块的结构相同,mipi协议处理模块与本技术前述实施例提供的mipi协议处理模块的结构相同,本技术这里不做重复介绍。

102.下面,以电子设备中设置有两个融合芯片以及电子设备中设置有一个融合芯片的两种情况为例,对电子设备的工作过程进行说明。

103.情况一、电子设备中包括5个感光芯片a、b、c、d和e、一个融合芯片f以及一个处理芯片g。其中,感光芯片a为超高清摄像模组的4000万像素感光芯片,感光芯片b为高清摄像模组的3200万像素感光芯片,感光芯片c为广角摄像模组的2000万像素感光芯片,感光芯片d为长焦摄像模组的800万像素感光芯片,感光芯片e为光学变焦摄像模组的800万像素感光芯片。

104.其中,感光芯片a和b通过c-phy接口将输出的图像数据传输给融合芯片f,感光芯片c、d和e通过d-phy接口将输出的图像数据传输给融合芯片f。其中,感光芯片a通过9条数据传输线与融合芯片f的第一输入端连接,感光芯片b也通过9条数据传输线与融合芯片f的第二输入端连接,感光芯片c通过10条数据传输线与融合芯片f的第三输入端连接,感光芯片d通过10条数据传输线与融合芯片f的第四输入端连接,感光芯片e通过10条数据传输线与融合芯片f的第五输入端连接,融合芯片f通过一个高速传输接口与处理芯片g连接。即,5个感光芯片与融合芯片之间连接有48条数据传输线。其中,一个高速传输接口包括两对数据传输线,每一对数据传输线包括两条数据传输线。

105.具体实现时,处理芯片g与融合芯片f连接,并通过向融合芯片f发送控制信号调整感光芯片a、b、c、d和e的工作参数,实现感光芯片a、b、c、d和e采集到特定参数的数据流,该数据流通过连接的48条数据传输线传输给融合芯片f,融合芯片f接收到感光芯片a、b、c、d和e输出的数据流之后,对接收的数据流进行编号,并对编号后的多个数据流进行融合得到第一高速融合数据流后,通过融合芯片f的输出端连接的高速传输接口将第一高速融合数据流发送给处理芯片g。其中,感光芯片a数据传输线的传输速率为2.1gsps,总带宽为14.4gbps,感光芯片b的数据传输线的传输速率1.69gsps,总带宽11.52gbps,感光芯片c的数据传输线的传输速率为1.05gsps,总带宽7.42gbps,感光芯片d的数据传输线的传输速率720mbps,总带宽2.88gbps,感光芯片e的数据传输线的传输速率720mbps,总带宽2.88gbps。其中,处理芯片g和融合芯片f之间的数据传输线的总带宽至少为19.04gbps。

106.处理芯片g可以通过一个高速传输接口接收到第一高速融合数据流,并根据第一

高速融合数据流中的包头和包尾数据进行还原成5个数据流,然后经mipi协议处理模块去掉包头和包尾,将去掉包头和包尾的数据输出给处理芯片g的图像信号处理器,图像信号处理器利用图像算法对接收的数据进行处理,输出图像。处理芯片g中的图像信号处理器可以调用一个感光芯片输出的数据流,也可以同时调用多个感光芯片输出的数据流,可以灵活设置内部的算法。例如,既可以把同一感光芯片的多帧图像进行融合提升动态范围和做降噪处理,也可以对多个不同感光芯片的数据流进行融合和加工提升景深和背景虚化,或实现更好的变焦效果等。

107.可以看出,5个感光芯片与融合芯片f之间连接有48条数据传输线,而融合芯片f与处理芯片g之间只需要4条数据传输线,因此,当融合芯片f跨接在5个感光芯片和处理芯片g之间时,可以在处理芯片g所在pcb上节省44条数据传输线的布线,从而简化pcb的设计难度,也可以在pcb上预留增加其它器件的位置,优化电子设备的系统架构。

108.情况二、电子设备中包括5个感光芯片a、b、c、d和e、两个融合芯片f和g以及一个处理芯片h。其中,感光芯片a为800万像素的感光芯片、感光芯片b为500万像素的感光芯片,感光芯片c为200万像素的感光芯片,感光芯片d为800万像素的感光芯片,感光芯片e为200万像素的感光芯片。

109.其中,感光芯片a、b和c通过d-phy接口将输出的图像数据传输给融合芯片f,感光芯片d和e通过d-phy接口将输出的图像数据传输给融合芯片g。其中,感光芯片a通过10条数据传输线与融合芯片f的第一输入端连接,感光芯片b通过10条数据传输线与融合芯片f的第二输入端连接,感光芯片c通过10条数据传输线与融合芯片f的第三输入端连接,感光芯片d通过10条数据传输线与融合芯片g的第一输入端连接,感光芯片f通过10条数据传输线与融合芯片g的第二输入端连接,融合芯片f和g分别通过一个高速传输接口与处理芯片h连接。即,5个感光芯片与融合芯片之间连接有50条数据传输线,融合芯片f和g与处理芯片h之间分别通过2条数据传输线。

110.具体实现时,处理芯片h通过分别向融合芯片f和融合芯片g发送控制信号,控制感光芯片a、b、c、d和e的工作参数,实现感光芯片a、b、c、d和e采集到特定参数的数据流,感光芯片a、b和c输出的数据流通过的30根数据传输线传输给融合芯片f,融合芯片f接收到感光芯片a、b和c输出的数据流之后,对接收的数据流进行编号,并对编号后的数据流融合为高速融合数据流后,通过融合芯片f的输出端连接的一个高速传输接口发送给处理芯片h。感光芯片d和e输出的图像数据通过连接的20根数据传输线传输给融合芯片g,融合芯片f接收到感光芯片c和d输出的数据流之后,对接收的数据流进行编号,并对编号后的数据流融合为高速融合数据流后,通过融合芯片g的输出端连接的一个高速传输接口发送给处理芯片h。

111.其中,感光芯片a数据传输线的传输速率1.152gbps,总带宽4.608gbps,感光芯片b数据传输线的传输速率720mbps,总带宽2.88gbps,感光芯片c数据传输线的传输速率288mbps,总带宽1.152gbps,感光芯片d数据传输线的传输速率1.152gbps,总带宽4.608gbps,感光芯片e数据传输线的传输速率288mbps,总带宽1.152gbps。其中,融合芯片f的高速传输接口的传输速率为8.64gbps,融合芯片g的高速传输接口的传输速率为5.76gbps。

112.处理芯片h可以通过融合芯片f和融合芯片g的高速传输接口接收到高速融合数据

流,并根据高速融合数据流包头中的编号将接收的高速融合数据流进行还原成5个数据流,然后经mipi协议处理模块去掉包头和包尾后,将去掉包头和包尾的数据输出给处理芯片h的图像信号处理器,图像信号处理器利用图像算法对接收的数据进行处理,输出图像。处理芯片h中的图像信号处理器可以调用一个感光芯片输出的数据流,也可以同时调用多个感光芯片输出的数据流,可以灵活设置内部的算法。例如,既可以把同一感光芯片的多帧图像进行融合提升动态范围和做降噪处理,也可以对多个不同感光芯片的数据流进行融合和加工提升景深和背景虚化。

113.可以看出,5个感光芯片与融合芯片f和融合芯片g之间连接有50条数据传输线,而融合芯片f以及融合芯片g与处理芯片h之间只需要4条输出传输线,因此,当融合芯片f以及融合芯片g跨接在5个感光芯片和处理芯片h之间时,可以在处理芯片h所在pcb上节省46条数据传输线的布线,从而简化pcb的设计难度,也可以在pcb上预留增加其它器件的位置,优化电子设备的系统架构。

114.基于同一发明构思,本技术实施例该提供了一种多数据通道数据融合装置,如图7所示,该装置700包括:本技术前述实施例提供的第一融合芯片202。

115.第一融合芯片201用于将与多个第一感光芯片连接的多个数据传输通道中的数据流进行融合,得到第一高速融合数据流,并通过与处理芯片连接的一个数据传输通道发送给处理芯片。

116.可选地,多数据通道数据融合装置700还可以包括:至少一个第二融合芯片。

117.其中,每一个第二融合芯片用于通过多个数据传输通道与多个第二感光芯片连接,以及通过一个数据传输通道与处理芯片连接;每一个第二融合芯片用于将与多个第二感光芯片连接的多个数据传输通道中的数据流进行融合,得到第二高速融合数据流,并通过与处理芯片连接的数据传输通道发送给处理芯片。

118.基于同一发明构思,本技术实施例还提供了一种多数据传输通道的融合方法,该方法的执行主体可以是本技术前述实施例提供的多数据传输通道的融合装置700,如图8所示,该方法具体包括以下步骤:

119.s801:多数据传输通道的融合装置获取与多个感光芯片连接的数据传输通道中的数据流。

120.具体地,多数据传输通道的融合装置可以通过一个数据传输通道与一个感光芯片连接,以获取每一个感光芯片产生的数据流。

121.在一示例中,在获取多个感光芯片产生的数据流之前,接收处理芯片发送的控制信号,并响应与该控制信号调整连接的多个感光芯片工作参数,以实现获取特定参数的数据流。

122.s802:多数据传输通道的融合装置将获取的多个数据流融合为至少一个高速融合数据流,并将至少一个高速融合数据流发送给处理芯片。

123.在一示例中,将多个数据流进行编号,并将编号后的多个数据流进行融合,得到至少一个高速融合数据流。

124.具体地,该编号可以设置在多个数据流中的包头和包尾中。

125.基于同一发明构思,本技术实施例还提供一种数据处理方法,该方法的执行主体可以是本技术前述实施例提供的电子设备中的处理芯片,如图9所示,该方法具体包括以下

步骤:

126.s901:处理芯片接收至少一个高速融合数据流。其中,每一个高速融合数据流中包括多个感光芯片产生的多个数据流。

127.具体地,处理芯片可以与前述多数据传输传输通道数据融合装置中的每一融合芯片连接,以获取每一融合芯片连接的多个感光芯片产生的多个数据流。

128.在一示例中,处理芯片在接收至少一个高速融合数据流之前,向多个感光芯片发送控制信号,以控制多个感光芯片的工作参数,以实现感光芯片输出特定参数的数据流。

129.可选地,处理芯片可以将该控制信号发送给各融合芯片,通过融合芯片控制与该融合芯片连接的感光芯片的工作参数。

130.具体地,融合芯片接收到控制信号之后,可以将控制信号发送给多个感光芯片,并直接控制多个感光芯片的工作参数。

131.s902:处理芯片将接收的至少一个高速融合数据流分配为多个数据流。

132.具体地,对至少一个高速融合数据流进行时钟恢复,利用至少一个高速融合数据流中的编号标识,对时钟恢复后的至少一个高速融合数据进行分配,得到每一个感光芯片对应的数据流。

133.在一示例中,根据至少一个高速融合数据中设置的多个数据包头以及数据包头中包含的编号,确定每一个感光芯片对应的数据流。其中,编号用于指明产生该原始数据流的感光芯片。

134.在另一示例中,根据至少一个高速融合数据中设置的多个数据包头和数据包尾,确定每一个感光芯片对应的数据流,其中,该数据包头和数据包尾中包括该数据包头对应的编号。

135.s903:处理芯片对多个数据流进行处理,得到图像。

136.具体地,利用图像信号处理器对多个数据流进行处理,得到图像。

137.可选地,利用mipi协议去掉多个数据流中的包头和包尾,得到目标数据流,并利用图像信号处理器对目标数据流进行处理,得到图像。

138.下面,结合图8和图9的描述,以电子设备包括一个融合芯片为例,对电子设备数据的工作过程进行详细说明,参见图10,具体包括以下步骤:

139.s1001:处理芯片向多个感光芯片发送控制信号。控制信号用于控制多个感光芯片的工作参数,使多个感光芯片输出特定参数的数据流。

140.可选地,若处理芯片和融合芯片连接有第一控制通道,处理芯片向处理芯片发送控制信号。其中,该控制信号用于控制融合芯片调整连接的多个感光芯片的工作参数。

141.可选地,若处理芯片和多个感光芯片之间连接有第二控制通道,处理芯片通过第二控制通道直接控制多个感光芯片的工作参数。

142.s1002:融合芯片将通过与多个感光芯片连接的多个数据传输通道中获取多个感光芯片输出的特定参数的数据流进行融合,得到高速融合数据流。

143.s1003:融合芯片将高速融合数据流发送给处理芯片。

144.s1004:处理芯片将获取的高速融合数据进行分配,得到多个数据流。

145.s1005:处理芯片利用多个数据流,得到图像。

146.本技术是参照根据本技术实施例的方法、设备(系统)、和计算机程序产品的流程

图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

147.这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

148.这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

149.显然,本领域的技术人员可以对本技术实施例进行各种改动和变型而不脱离本技术实施例的精神和范围。这样,倘若本技术实施例的这些修改和变型属于本技术权利要求及其等同技术的范围之内,则本技术也意图包含这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1