一种实现高性能大容量路由设备的设计方法与流程

1.本发明涉及网络通信技术,具体涉及一种实现高性能大容量路由设备的设计方法。

背景技术:

2.随着互联网的急速发展与普及、网络流量的激增、5g时代的即将到来以及不断应运而生的多种复杂网络应用,对路由器等组网设备也提出了更高的要求。我国网民数量已超8亿,互联网骨干网带宽已超200tbps,骨干网带宽每年以40%以上的速度增长,随着5g网络的规模建设,必然推动骨干网的带宽以更高速度增长,为了满足带宽增长速度,除不断增加光缆数量外,单端口带宽能力也从kbps提升至100gbps,目前通用路由器每u高度的处理能力一般不超过100gbps,单块硬件板卡所支持的掩码acl规则容量一般不超过10万条,数据特征码不超过5000条。

3.为了应对海量的hash规则、掩码acl规则及数据特征码规则的管理要求和庞大的流量线速处理,假使采用通用路由器设备进行组网建设,势必造成机房空间的浪费以及更高的使用成本。

4.高性能大容量的路由设备设计是一项高技术含量的课题,是高科技研发团队智慧结晶,在此提出一种实现高性能大容量路由设备的设计方法。

技术实现要素:

5.本发明目的在于提供一种实现高性能大容量路由设备的设计方法,首先通用路由器单块板卡一般采用单颗网络处理器芯片(网络处理器芯片为一种可编程器件,可应用于通信领域的各种任务,比如流量管理、协议分析、路由查找、数据溯源等)以及单颗tcam芯片(tcam芯片是一种态内容寻址存储器,主要用于快速查找掩码acl、数据特征码、路由等表项)来结合实现流量的解析和多种规则类型的存储和查找。本方法中单块板卡采用多颗网络处理器和多颗tcam芯片,具体实现高性能处理及大容量多种规则类型存储和查找的方法如下:步骤一:将单块板卡内的多颗网络处理器多颗tcam芯片分为多组协同处理单元,每组协同处理单元内包含两颗网络处理器芯片和两颗tcam芯片,每组协同处理单元可完成100gbps以上流量模型会话内的所有的流量管理、协议分析以及多种规则类型存储和查找等需求。之所以没有在一个协同处理单元组内只分配单颗网络处理器是考虑协议分析和规则查表对性能要求比较高,单颗网络处理器芯片无法做到100gbps的短包线速处理,故上述设计可使单块板卡的短包线速处理性能超过200gbps,掩码acl规则容量超过20万条,数据特征码容量超过1万条。

6.步骤二:流量通过一组协同处理单元的网络处理器-a进入设备后,在网络处理器-a内判断流量类型,如果是非ip流量,则直接进行源口进源口出的透传动作处理动作;如果是ip流量,则提取该流的五元组(源ip、目的ip、源端口、目的端口以及协议号)信息以及输

入端口的物理端口号信息,将上述提取的五元组信息在网络处理器-a内作为hash值计算,输入端口的物理端口号主要便于后续流量执行透传的动作。

7.步骤三:步骤二中的hash值计算方法:首先将源ip权重值置1,目的ip权重值置2,源端口权重值置3,目的端口权重值置4,协议号权重值置5,然后将五个信息进行累加得到一个32比特的值hresult1,将hresult1的最高16个比特值和hresult1的低16个比特值异或运算得到一个16比特的值hresult2,将hresult2的15~12比特值和hresult2的11~8比特值进行异或运算得到4比特的值hresult3,hresult2的7~4比特值和hresult2的3~0比特值进行异或运算得到4比特的值hresult4,hresult3与hresult4再次异或运算后取最后一个比特的值。

8.步骤四:约定如果步骤三中得到的hash值为0,则该流量的hash规则查找匹配需要在网络处理器-a进行,如果步骤三种得到的hash值为1,则该流量的hash规则查找匹配需要网络处理器-b中进行。

9.步骤五:每组协同处理单元的两个网络处理器各外挂配置一个tcam芯片,在网络处理器-a中外挂的tcam内分配进行数据特征码的匹配查找任务,在网络处理器-b中外挂的tcam内分配进行掩码acl规则的匹配查找任务。

10.步骤六:将通过网络处理器-a或者网络处理器-b查询得到的hash规则匹配结果、通过网络处理器-a查询得到的数据特征码规则匹配结果与通过网络处理器-b查询得到的掩码acl匹配的结果在处网络处理器-b内做优先级比较,其中在网络处理器-a查询匹配的结果通过信息携带通告至网络处理器-b,得到最终最高的规则优先级匹配结果,然后根据匹配结果执行处理动作。

11.步骤七:对于上述多种规则类型的增删改查操作,其中hash规则需要根据步骤三的算法决定添加到网络处理器-a还是网络处理器-b,数据特征码规则添加到网络处理器-a外挂的tcam芯片,掩码acl规则添加到网络处理器-b外挂的tcam芯片。上述设计方法使单个协同处理单元内hash规则容量、掩码acl规则容量和数据特征码规则容量至少扩大了一倍。

12.以上本发明的技术方案,与现有相比,其显著的有益效果在于:该设计方法使单块板卡内hash规则容量、掩码acl规则容量和数据特征码规则容量成倍扩大,能够在有限空间下提高设备的可靠性和拓展性,应对海量的hash规则、掩码acl规则及数据特征码规则的管理要求和庞大的流量线速处理,使用成本低廉。

附图说明

13.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

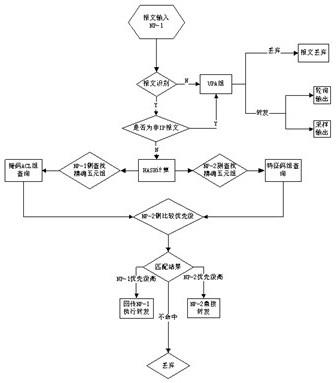

14.图1是本发明的一种实现高性能大容量路由设备的设计方法的流程图。

15.图2是本发明的一种实现高性能大容量路由设备的设计方法一种例子的结构组成图。

具体实施方式

16.为了更了解本发明的技术内容,特举具体实施例并配合所附图式说明如下:结合图1,本发明提出一种实现高性能大容量路由设备的设计方法,图2是其中一种实现高性能大容量路由设备的设计方法的例子,下面结合例子对本发明所提及的方法做详细阐述。所述方法包括:首先通用路由器单块板卡一般采用单颗网络处理器芯片(网络处理器芯片为一种可编程器件,可应用于通信领域的各种任务,比如流量管理、协议分析、路由查找、数据溯源等)以及单颗tcam芯片(tcam芯片是一种态内容寻址存储器,主要用于快速查找掩码acl、数据特征码、路由等表项)来结合实现流量的解析和多种规则类型的存储和查找。

17.所述例子中实现高性能大容量路由设备的设计方法为单块板卡采用四颗网络处理器和四颗tcam芯片,具体实现高性能处理及大容量多种规则类型存储和查找的方法如下:步骤一:将单块板卡内的四颗网络处理器和四颗tcam芯片分为两组协同处理单元,即每组协同处理单元内包含两颗网络处理器芯片和两颗tcam芯片,每组协同处理单元可完成100gbps以上流量模型会话内的所有的流量管理、协议分析以及多种规则类型存储和查找等需求,因为如果在一个协同处理单元组内只分配单颗网络处理器,协议分析和规则查表对性能要求比较高,单颗网络处理器芯片无法做到100gbps的短包线速处理,故上述设计可使单块板卡的短包线速处理性能超过200gbps,掩码acl规则容量超过20万条,数据特征码容量超过1万条。

18.步骤二:流量通过一组协同处理单元的网络处理器-a进入设备后,在网络处理器-a内判断流量类型,如果是非ip流量,则直接进行源口进源口出的透传动作处理动作;如果是ip流量,则提取该流的五元组(源ip、目的ip、源端口、目的端口以及协议号)信息以及输入端口的物理端口号信息,将上述提取的五元组信息在网络处理器-a内作为hash值计算,输入端口的物理端口号主要便于后续流量执行透传的动作。

19.步骤三:步骤二中的hash值计算方法:首先将源ip权重值置1,目的ip权重值置2,源端口权重值置3,目的端口权重值置4,协议号权重值置5,然后将五个信息进行累加得到一个32比特的值hresult1,将hresult1的最高16个比特值和hresult1的低16个比特值异或运算得到一个16比特的值hresult2,将hresult2的15~12比特值和hresult2的11~8比特值进行异或运算得到4比特的值hresult3,hresult2的7~4比特值和hresult2的3~0比特值进行异或运算得到4比特的值hresult4,hresult3与hresult4再次异或运算后取最后一个比特的值。

20.步骤四:约定如果步骤三中得到的hash值为0,则该流量的hash规则查找匹配需要在网络处理器-a进行,如果步骤三种得到的hash值为1,则该流量的hash规则查找匹配需要网络处理器-b中进行。

21.步骤五:每组协同处理单元的两个网络处理器各外挂配置一个tcam芯片,在网络处理器-a中外挂的tcam内分配进行数据特征码的匹配查找任务,在网络处理器-b中外挂的tcam内分配进行掩码acl规则的匹配查找任务。

22.步骤六:将通过网络处理器-a或者网络处理器-b查询得到的hash规则匹配结果、通过网络处理器-a查询得到的数据特征码规则匹配结果与通过网络处理器-b查询得到的

掩码acl匹配的结果在处网络处理器-b内做优先级比较,其中在网络处理器-a查询匹配的结果通过信息携带通告至网络处理器-b,得到最终最高的规则优先级匹配结果,然后根据匹配结果执行处理动作。

23.步骤七:对于上述多种规则类型的增删改查操作,其中hash规则需要根据步骤三的算法决定添加到网络处理器-a还是网络处理器-b,数据特征码规则添加到网络处理器-a外挂的tcam芯片,掩码acl规则添加到网络处理器-b外挂的tcam芯片。上述设计方法使单个协同处理单元内hash规则容量、掩码acl规则容量和数据特征码规则容量至少扩大了一倍。

24.该设计方法使单块板卡内hash规则容量、掩码acl规则容量和数据特征码规则容量成倍扩大,能够在有限空间下提高设备的可靠性和拓展性,应对海量的hash规则、掩码acl规则及数据特征码规则的管理要求和庞大的流量线速处理,使用成本低廉。

25.在本公开中参照附图来描述本发明的各方面,附图中示出了许多说明的实施例。本公开的实施例不必定义在包括本发明的所有方面。应当理解,上面介绍的多种构思和实施例,以及下面更加详细地描述的那些构思和实施方式可以以很多方式中任意一种来实施,这是因为本发明所公开的构思和实施例并不限于任何实施方式。另外,本发明公开的一些方面可以单独使用,或者与本发明公开的其他方面的任何适当组合来使用。

26.虽然本发明已以较佳实施例揭露如上,然其并非用以限定本发明。本发明所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,当可作各种的更动与润饰。因此,本发明的保护范围当视权利要求书所界定者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1