一种2lane的LVDS视频编码方法及系统与流程

一种2lane的lvds视频编码方法及系统

技术领域

1.本公开涉及视频编解码技术领域,尤其涉及一种2lane的lvds视频编码方法及系统。

背景技术:

2.lvds,low

‑

voltage differential signaling,低电压差分信号标准,常用来传输串行信号标准。传统的lvds编码都采用lvds编码芯片的形式,其中一种是将已有的视频信号格式转化编码成lvds电平信号,这种lvds信号是遵循液晶屏的lvds显示驱动标准,比如龙讯公司的lt8619c芯片将hdmi信号编码成lvds信号来实现驱动屏幕显示。另外一种是图像探测器,将图像视频信号直接编码成lvds信号输出,这种lvds信号在信号中嵌入了同步码,一些特定的soc通过判断这些同步码来同步接收视频数据,比如索尼公司的图像传感器imx226。以上两种方式的lvds编码方式都采用芯片实现编码,这样若市面上没有该芯片方案那会造成没有方法可用的地步。对于海思系列的soc芯片比如hi3559都带有lvds电平标准的视频接口,这些接口原本是应用于特定的图像传感器芯片比如imx226,但对于一些特殊应用的场景比如要将pal视频信号或者sdi视频信号传递给hi3559,而市面上没有现成的视频转化方案,这就需要fpga实现视频转化。fpga在对接hi3559的时候就需要根据hi3559的视频时序完成视频的lvds编码。因此需要提出了一种视频编码方法,可以在hi3559硬件带宽要求下,将分辨率小于1080p的任意分辨率视频信号编码成2lane的lvds信号传递给hi3559。

技术实现要素:

3.有鉴于此,本公开实施例提供一种2lane的lvds视频编码方法及系统,可以在hi3559硬件带宽要求下,为hi3559提供小于1080p的任意分辨率的2lane lvds编码视频信号。

4.为了实现上述目的,本发明提供如下技术方案:

5.一种2lane的lvds视频编码方法,包括如下步骤:

6.(1)视频数据通过同步码嵌入模块,完成同步码的嵌入;

7.(2)通过fifo_16to32模块将相邻两个16bit的像素点组合为32bit的视频数据;

8.(3)输出的图像数据分别对高16位和低16位进行同步打拍处理,再输入给fifo_16to8模块,fifo_16to8模块将16位的数据分成前后两个8位数据;

9.(4)输出的视频流信号通过触发器进行同步处理;

10.(5)将视频数据给到8bit_to_1bit模块,对8bit的数据进行串行化处理得到串行数据;

11.(6)将串行化的视频数据通过单端转差分模块输出fpga。

12.进一步地,fifo_16to32模块输入的时钟是clk1,输出时钟是二分频的clk2。

13.进一步地,fifo_16to8模块输入时钟是二分频的clk2,输出时钟是像素时钟clk1。

14.本发明还提供一种2lane的lvds视频编码系统,包括:同步码嵌入模块、lvds编码模块、锁相环模块和复位模块;

15.所述同步码嵌入模块用于将hi3559接收数据所需要的同步码信息嵌入到视频流中;

16.所述的lvds编码模块包括1个fifo_16to32模块、两个fifo_16to8模块、两个8bit_to_1bit模块(fifo_8to1),用于通将视频数据重组在2条lane上并实现并串转化;

17.所述锁相环模块用于提供lvds编码模块的编码时钟;

18.所述复位模块用于确保fifo正常工作,在每次初始化lvds编码模块的时候复位fifo,再通过延时模块依次开启fifo。

19.进一步地,所述同步码嵌入模块的输入视频数据为16bit的yuv420格式的视频数据。

20.进一步地,所述的hi3559接收数据所需要的同步码信息包括帧起始同步码、帧结束同步码、行起始同步码、行结束同步码。

21.进一步地,还包括触发器模块,所述触发器模块用于在数据从一个模块传递到下一个模块的过程中对数据进行同步触发处理,以对时序进行优化。

22.本发明的一种2lane的lvds视频编码方法及系统,其有益效果在于:本发明由于采用了ff模块作为同步时序优化,采用fifo作为数据转化介质,所以该设计具有良好的时序特点,同时可以在硬件带宽要求下将分辨率小于1080p的任意分辨率的视频信号编码成2lane的lvds信号传递给hi3559。该编码方法具有编码时序稳定、通用性较强等优点。

附图说明

23.为了更清楚地说明本公开实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

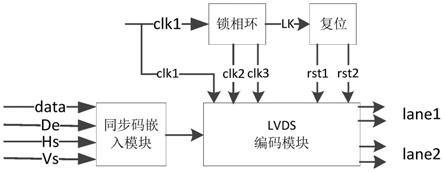

24.图1为本发明实施例中2lane的lvds视频编码实现框图;

25.图2为本发明实施例中同步码嵌入时序;

26.图3为本发明实施例中时钟生成原理图;

27.图4为本发明实施例中复位信号生成原理图;

28.图5为本发明实施例中lvds编码模块图。

具体实施方式

29.下面结合附图对本公开实施例进行详细描述。

30.以下通过特定的具体实例说明本公开的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本公开的其他优点与功效。显然,所描述的实施例仅仅是本公开一部分实施例,而不是全部的实施例。本公开还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本公开的精神下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。基于本公开中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本公开保护的范围。

31.要说明的是,下文描述在所附权利要求书的范围内的实施例的各种方面。应显而易见,本文中所描述的方面可体现于广泛多种形式中,且本文中所描述的任何特定结构及/或功能仅为说明性的。基于本公开,所属领域的技术人员应了解,本文中所描述的一个方面可与任何其它方面独立地实施,且可以各种方式组合这些方面中的两者或两者以上。举例来说,可使用本文中所阐述的任何数目个方面来实施设备及/或实践方法。另外,可使用除了本文中所阐述的方面中的一或多者之外的其它结构及/或功能性实施此设备及/或实践此方法。

32.还需要说明的是,以下实施例中所提供的图示仅以示意方式说明本公开的基本构想,图式中仅显示与本公开中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

33.另外,在以下描述中,提供具体细节是为了便于透彻理解实例。然而,所属领域的技术人员将理解,可在没有这些特定细节的情况下实践所述方面。

34.本发明所述的2lane的lvds视频编码方法框图如图1所示,为一种2lane的lvds编码方法实现框图,主要包括同步码嵌入模块、lvds编码模块、锁相环模块和复位模块。

35.1、同步码嵌入模块

36.本发明所述的同步码嵌入模块将hi3559接收数据所需要的同步码信息嵌入到视频流中;所述的同步码嵌入模块的输入视频数据为16bit的yuv420格式的视频数据;所述的hi3559所需要的同步码格式如表1所示,其描述为16进制,包括帧起始同步码,帧结束同步码,行起始同步码,行结束同步码;同步码数据是由4个16bit的数据表示,在嵌入到视频流中是要代替相应的图像信号。

37.表1:同步码格式

38.帧起始同步码ffff00000000sav帧结束同步码ffff00000000eav行起始同步码ffff00000000sol行结束同步码ffff00000000eol

39.如图2所示,设视频信号的分辨率为m.n,帧起始同步码作为一场视频有效信号的第1行的视频有效信号起始标志,帧结束同步码作为一场视频有效信号的第m行的视频有效结束标志;行起始同步码作为第2行至第m行的视频有效起始标志,行结束同步码作为第1行至第m

‑

1行视频有效的结束标志。

40.本发明所述的同步码嵌入模块的原理如图2所示,由于视频流数据只有一条通道,而最后lvds编码出来的视频数据是2条通道的,而且每一个lvds通道都要嵌入同步码数据。本发明提供了一个思路,在同步码嵌入模块中先把后续分开相邻像素所需要同步码结对嵌入到视频流中,如图2所示,同步码数据是ffff,ffff,0000,0000,0000,0000,sav,sav(或eav,eav或sol,sol或eol,eol)。根据上一断描述的,在视频de信号的两边分别嵌入同步码数据。而在视频有效信号期间即de高电平期间,保留原视频流数据。

41.1、锁相环模块

42.锁相环模块提供lvds编码时钟,如图3所示,有输入视频的像素时钟clk1,分频出时钟clk2,倍频出clk3,locked信号是时钟稳定标志,代表着锁相环稳定工作。锁相环生成

时钟和像素时钟的关系是clk2=0.5clk1,clk3=8clk1。

43.3、复位模块

44.复位信号是为了确保fifo正常工作,在每次初始化lvds编码模块的时候复位fifo,再通过延时模块依次开启fifo,这样使得fifo的工作更加稳定。如果没有该复位信号,在每次输入图像消失的时候会造成图像u分量和v分量相反的现象而造成画面颜色失真。复位信号rst1和rst2的生成是由延时模块delay1和delay2产生的,对应的延时拍数是图5中fifo深度的一半。

45.4、lvds编码模块

46.本发明所述的lvds编码模块的原理框图如图5所示,包括1个16bit转32bit的fifo(fifo_16to32)、两个16bit转8bit的fifo(fifo_16to8)、两个8bit转1bit模块(串行化模块)。另外clk1,clk2,clk3信号来自于锁相环模块,rst1,rst2来自于复位模块。在数据从一个模块传递到下一个模块的过程中需要通过触发器模块(ff)对数据进行同步触发处理,对时序进行优化。

47.所述的lvds编码模块的原理及工作顺序如下所示:

48.(1)视频数据来自于同步码嵌入模块,其同步码的格式如图2所示;

49.(2)通过fifo_16to32模块将相领两个16bit的像素点组合为32bit的视频数据,这样就实现把相邻图像数据分布在不同的两个lane上,且这两个像素点数据变成同步数据了。fifo_16to32输入的时钟是clk1,输出时钟是二分频的clk2。

50.(3)输出的图像数据分别对高16位和低16位进行同步打拍处理,再输入给fifo_16to8模块,fifo_16to8模块把16位的数据分成前后两个8位数据,其输入时钟是二分频的clk2,输出时钟是像素时钟clk1。

51.(4)输出的视频流信号要通过触发器同步处理,这样可以优化视频时序。

52.(5)将视频数据给到8bit_to_1bit模块,对8bit的数据进行串行化处理得到串行数据。

53.(6)将串行化的视频数据通过单端转差分模块输出fpga。

54.下面通过具体实施例,并结合附图,对本方案进行详细的阐述。

55.设输入的分辨率为1080p 30hz(1920*1080,时钟频率74.25hz),则本例子中所用到的clk1为74.25mhz,clk2为clk1的二分频,则为37.125mhz,clk3为594mhz,采用xilinx k7325t作为逻辑运行平台。

56.所述的同步码格式为表1所示的数据,其中sav的16进制表示为8080,eav的16进制表示为9d9d,sol的16进制表示为abab,eol的16进制表示为b6b6;

57.所述的fifo_16to32模块为深度512,16位转32位的fifo模块;

58.所述的fifo_16to8模块为深度512,16位转8位的fifo模块;所述的ff模块为2个节拍的触发器时序同步;

59.所述的8bit_to_1bit模块为xilinx fpga的oserdes模块,设置为8bit输入,1bit串行输出;

60.所述的单端转差分模块为xilinx fpga的obuf_diff。

61.则lvds编码的流程如下所示:

62.1)视频数据通过同步码嵌入模块,完成同步码的嵌入。

63.2)通过fifo_16to32模块将相领两个16bit的像素点组合为32bit的视频数据,这样就实现把相邻图像数据分布在不同的两个lane上,且这两个像素点数据变成同步数据了.fifo_16to32输入的时钟是clk1,输出时钟是二分频的clk2。

64.3)输出的图像数据分别对高16位和低16位进行同步打拍处理,再输入给fifo_16to8模块,fifo_16to8模块把16位的数据分成前后两个8位数据,其输入时钟是二分频的clk2,输出时钟是像素时钟clk1。

65.4)输出的视频流信号要通过触发器同步处理,这样可以优化视频时序。

66.5)将视频数据给到8bit_to_1bit模块,对8bit的数据进行串行化处理得到串行数据。

67.6)将串行化的视频数据通过单端转差分模块输出fpga。

68.以上就是具体实施方式,若要改变分辨率直接调整输入的分辨率和时钟信号即可完成2lane的lvds编码。

69.对于hi3559平台,其2lane的lvds编码的带宽受到fpga和hi3559 mipi rx串行接收模块的限制,理论上,2lane的lvds编码传输的视频格式最多不要超过1080p 30hz。

70.以上所述,仅为本公开的具体实施方式,但本公开的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本公开揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本公开的保护范围之内。因此,本公开的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1