图像传感器、指纹检测装置和电子设备的制作方法

图像传感器、指纹检测装置和电子设备

1.本申请是申请日为2020年8月21日、申请号为202010851264.3、名称为“图像传感器、指纹检测装置和电子设备”的发明申请的分案申请。

技术领域

2.本申请实施例涉及图像传感器领域,并且更具体地,涉及图像传感器、指纹检测装置和电子设备。

背景技术:

3.图像传感器是一种将光信号转换成电信号的装置。图像传感器通常包括像素电路、输出电路等,其中,像素电路可以将接收到的光信号转换成电信号并输入到输出电路,输出电路可以将像素电路输出的电信号读出。图像传感器的面积和功耗成为影响其发展的因素之一,因此,如何减小图像传感器的面积和功耗,成为一项亟待解决的问题。

技术实现要素:

4.本申请实施例提供一种图像传感器、指纹检测装置和电子设备,具有较小的面积和功耗。

5.第一方面,提供了一种图像传感器,包括:像素电路阵列,其中每个像素电路用于根据接收到的光信号产生输出信号;输出电路,用于同时接收所述像素电路阵列中的多个像素电路的输出信号,并输出所述多个像素电路的输出信号的信号均值。

6.在该方案中,图像传感器中的输出电路可以同时接收像素电路阵列中的多个像素电路的输出信号,并输出该多个像素电路的输出信号的信号均值,从而实现了在输出电路中实现对多个像素电路的输出信号的合并和平均。对于在需要进行信号合并和平均的场景中,极大地减少了输出电路的数量,减小了图像传感器的面积和功耗。

7.在一种可能的实现方式中,所述图像传感器还包括:采样电路,用于采集所述输出电路输出的所述信号均值。

8.由于每个输出电路仅需要一个采样电路对其输出的信号均值进行采集,因此,图像传感器中采样电路的数量也减少了,进一步减小了图像传感器的面积和功耗。

9.在一种可能的实现方式中,所述像素电路阵列由多个子阵列组成,所述多个像素电路包括所述多个子阵列中编号相同的像素电路,所述各个子阵列中编号相同的像素电路位于各自对应的子阵列内相同的行和列。

10.为了便于对像素电路结构中需要进行信号合并和平均的多个像素电路进行选择,该多个像素电路的分布可以是,该多个像素电路在其所在的像素电路子阵列中位于相同行和列,从而可以通过行扫描和列扫描的方式选通当前需要进行信号合并和平均的该多个像素电路。

11.在一种可能的实现方式中,所述输出电路包括运算放大器,所述运算放大器包括第一输入端和第二输入端,所述多个像素电路的第一输出端与所述运算放大器的第一输入

端相连,所述多个像素电路的第二输出端与所述运算放大器的第二输入端相连。

12.在一种可能的实现方式中,所述运算放大器还包括与其输出端相连的多组晶体管,其中每组晶体管包括串联的第一晶体管和第二晶体管。其中,所述多组晶体管的数量与所述多个像素电路的数量相同,所述第一晶体管和所述像素电路的源跟随输入管的跨导相同,所述第二晶体管是与所述像素电路的选通开关管相同的选通开关管,所述源跟随输入管和所述选通开关管串联在所述像素电路的第一输出端和第二输出端之间。

13.在一种可能的实现方式中,所述运算放大器还包括电流镜,所述电流镜的一端与每个像素电路的源跟随输入管相连,所述电流镜的另一端与每组晶体管中的第一晶体管相连。

14.在一种可能的实现方式中,所述运算放大器还包括电流源,所述电流源的一端与每个像素电路的选通开关管相连,并与每组晶体管中的第二晶体管相连,所述电流源的另一端接地。

15.在一种可能的实现方式中,所述运算放大器还包括电流镜,所述电流镜的一端与每个像素电路的选通开关管相连,所述电流镜的另一端与每组晶体管中的第二晶体管相连。

16.在一种可能的实现方式中,所述运算放大器还包括电流源,所述电流源的一端与每个像素电路的源跟随输入管相连,并与每组晶体管中的第一晶体管相连,所述电流源的另一端接地。

17.在一种可能的实现方式中,所述像素电路还包括光电二极管、寄生电容器、复位开关管和传输管。其中,所述光电二极管的正极接地,所述光电二极管的负极与所述传输管的源极相连,所述传输管的栅极由传输信号控制,所述传输管的漏极与所述寄生电容器的一端、所述源跟随输入管的栅极、以及所述复位开关管的源极相连,所述传输管的栅极由传输信号控制,所述寄生电容器的另一端接地,所述复位开关管的漏极接复位电压,所述复位开关管的栅极由复位信号控制,所述选通开关管的栅极由选通信号控制,所述源跟随输入管的源极与所述选通开关管的漏极相连,所述源跟随输入管的漏极一端和所述选通开关管的源极一端分别作为所述像素电路的第一输出端和第二输出端。

18.在一种可能的实现方式中,所述采样电路包括第一采样电容和第二采样电容,所述第一采样电容和所述第二采样电容用于在所述像素电路曝光前后分别采集两次所述信号均值,以实现相关双采样。

19.采用相关双采样可以消除像素电路中的复位噪声的干扰,提高图像传感器的性能。

20.在一种可能的实现方式中,所述图像传感器应用于指纹检测装置中,其中,所述多个像素电路接收到的所述光信号为手指返回的同一方向的光信号。

21.第二方面,提供了一种指纹检测装置,包括:前述第一方面以及第一方面的任一种可能的实现方式中的图像传感器。

22.在一种可能的实现方式中,其中,所述指纹检测装置还包括设置在所述每个子阵列上方的光路引导结构,所述光路引导结构包括微透镜和设置在所述微透镜下方的多个挡光层,所述多个挡光层中的最上方的挡光层设置有至少一个通光小孔且其余挡光层中的每个挡光层上设置多个通光小孔,以形成所述多个方向的导光通道,所述微透镜用于对所述

显示屏上方的手指返回的光信号进行会聚,所述多个方向的导光通道用于将对应方向的所述光信号引导至对应的像素电路。

23.第三方面,提供了一种电子设备,包括:前述第二方面以及第二方面的任一种可能的实现方式中的指纹检测装置。

附图说明

24.图1是传统的图像传感器的结构示意图。

25.图2是基于图1的图像传感器的工作原理的示意图。

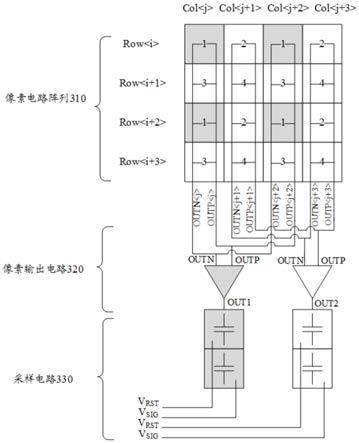

26.图3是本申请实施例的图像传感器的示意图。

27.图4是基于图3的图像传感器的工作原理的示意图。

28.图5是本申请实施例的一种可能的像素电路的结构示意图。

29.图6是本申请实施例的一种可能的输出电路的结构示意图。

30.图7是基于图5和图6的图像传感器的一种可能的结构示意图。

31.图8是本申请实施例的实现多接收方向的光路的示意图。

32.图9是本申请实施例的实现多接收方向的光路的示意图。

具体实施方式

33.下面将结合附图,对本申请中的技术方案进行描述。

34.本申请实施例中的图像传感器可以应用于任何需要进行信号合并和平均的场景中,例如,该图像传感器可以应用在指纹检测装置中,用来对手指返回的信号进行采集从而获取该手指的指纹图像。

35.图1是传统的图像传感器的结构示意图。图1所示的图像传感器包括像素电路阵列110、输出电路120、采样电路130、行扫描控制器140、列扫描控制器150、多路选择开关160、可编程增益放大器(programmable gain amplifier,pga)170和模数转换电路(analog

‑

to

‑

digital converter,adc)180等。像素电路阵列110中被选通的像素电路将各自接收到的光信号转换成电信号,并输入至输出电路120,并由输出电路120将该电信号读出。输出电路120可以具有多种形式,包括但不限于传统的4t像素电路结构的源跟随器。采样电路130可以对输出电路120输出的信号进行采样和保持,并进行相关双采样(correlated double sampling,cds),然后在多路选择开关的控制下依次输出到pga电路170和adc电路180分别进行放大和模数转换等操作,得到最终的数据。

36.图2是基于图1所示的图像传感器的工作原理的示意图。其中,图2中的row表示行,col表示列。如图2所示的像素电路阵列110,编号为1的像素电路的输出信号需要进行信号合并和平均,编号为2的像素电路的输出信号需要进行信号合并和平均,编号为3的像素电路的输出信号需要进行信号合并和平均,编号为4的像素电路的输出信号需要进行信号合并和平均。

37.图2中示出了4个子阵列,分别为:由左上角的四个像素电路组成的子阵列、由右上角的四个像素电路组成的子阵列、由左下角的四个像素电路组成的子阵列、以及由右下角的四个像素电路组成的子阵列。应理解,每4个子阵列中的编号相同的像素电路的输出信号对应的信号均值在进行后续处理后,可以作为图像传感300所采集的一幅图像中的一个像

素点的像素数据,例如,4个像素电路1的输出信号对应的信号均值在进行后续处理后可以作为像素电路1的像素数据,4个像素电路2的输出信号对应的信号均值在进行后续处理后可以作为像素电路2的像素数据。

38.以4个像素电路1为例,在第i行和第i+2行选通时,第i行第j列的像素电路1的输出信号为out1<j>,该输出信号out1<j>被对应的输出电路120读出,并得到信号b1<j>,信号b1<j>会被采样电路中与其对应的采样电容进行采样和保持;第i+2行第j列的像素电路1的输出信号为out2<j>,该输出信号out2<j>通过对应的输出电路120读出,并得到信号b2<j>,信号b2<j>会被采样电路中与其对应的采样电容进行采样和保持;第i行第j+2列的像素电路1的输出信号为out1<j+2>,该输出信号out1<j+2>通过对应的输出电路120读出,并得到信号b1<j+2>,信号b1<j+2>会被采样电路中与其对应的采样电容进行采样和保持;第i+2行第j列的像素电路1的输出信号为out2<j+2>,该输出信号out2<j+2>通过对应的输出电路120读出,并得到信号b2<j+2>,信号b2<j+2>会被采样电路中与其对应的采样电容进行采样和保持。像素电路阵列110中的4个像素电路1经过各自对应的输出电路120,最终分别得到的信号b1<j>、b2<j>、b1<j+2>和b2<j+2>,然后经过各自对应的采样电路130后,得到合并平均后的数据,分别记为v

rst

和v

sig

。其中,v

rst

和v

sig

分别是曝光前后两次采集的信号,对这两个信号进行相关双采样后,可以消除噪声信号,接着将相关双采样后的信号输入至pga电路170和adc电路180进行放大和模数转换,得到像素电路1的像素数据。

39.在第i行和第i+2行选通时,4个像素电路2经过类似的过程,最终也可以得到像素电路2对应v

rst

和v

sig

,对这两个信号进行相关双采样后,输入至pga电路170和adc电路180进行放大和模数转换,得到像素电路2的像素数据。

40.接着,在第i+1行和第i+3行选通时,对4个像素电路3和4个像素电路4进行相似的操作,最终得到各自的像素数据。

41.可以看出,在图2中,需要进行信号合并和平均的多个像素电路分别通过多个输出电路120读出,再分别通过多个采样电容进行采样和保持,最后再进行信号合并和平均。具体地,如果需要进行信号合并和平均的多个子像素分布在n行,且像素阵列110包括y列,那么需要n

×

y个输出电路120和n

×

y个采样电路130。因此,图像传感器中需要设置大量的输出电路120和采样电路130,导致图像传感器的面积和功耗都较高。

42.为此,本申请实施例提供了一种图像传感器,具有较小的面积和功耗。

43.图3是本申请实施例的图像传感器的示意图。如图3所示,图像传感器300包括像素电路阵列310和输出电路320。该输出电路320也可以称为读出电路320或者读取电路320。

44.其中,像素电路阵列310中的每个像素电路用于根据接收到的光信号产生输出信号。

45.输出电路320用于同时接收像素电路阵列310中的多个像素电路的输出信号,并输出多个像素电路的输出信号的信号均值。

46.在该实施例中,图像传感器300中的输出电路320可以同时接收像素电路阵列310中的多个像素电路的输出信号,并输出该多个像素电路的输出信号的信号均值,从而实现了在输出电路320中实现对多个像素电路的输出信号的合并和平均。对于在需要进行信号合并和平均的场景中,极大地减少了输出电路的数量,减小了图像传感器的面积和功耗,并降低了成本。

47.进一步地,可选地,如图3所示,图像传感器300还可以包括采样电路330,用于采集输出电路320输出的该信号均值。

48.由于每个输出电路仅需要一个采样电路对其输出的信号均值进行采集,因此,图像传感器中采样电路的数量也减少了,进一步减小了图像传感器的面积和功耗。

49.进一步地,可选地,如图3所示,图像传感器300还可以包括多路选择开关360,用于选通多路中某一路输出的该信号均值,以使多路输出的该信号均值依次通过后续的公共的处理电路进行处理。

50.进一步地,可选地,如图3所示,图像传感器300还可以包括行扫描控制器340和列扫描控制器350,分别用于控制像素电路阵列310中的行和列的选通。

51.进一步地,可选地,如图3所示,图像传感器300还可以包括pga电路370,用于对接收到的信号进行放大。

52.进一步地,可选地,如图3所示,图像传感器300还可以包括adc电路370,用于对放大后的信号进行模数转换。

53.本申请实施例中,图像传感器300可以同时对像素电路阵列310中的任意位置的多个像素电路进行信号合并和平均。为了便于对像素电路阵列310中需要进行信号合并和平均的该多个像素电路进行选择,优选地,在一种实现方式中,像素电路阵列310由多个子阵列组成,该多个像素电路包括该多个子阵列中编号相同的像素电路,各个子阵列中编号相同的像素电路位于各自对应的子阵列内相同的行和列。例如,各个子阵列中编号为1的像素电路均位于对应子阵列中的第一行第一列,各个子阵列中编号为2的像素电路均位于对应子阵列中的第一行第二列,等等。这样,可以很方便地通过行扫描和列扫描的方式选通当前需要进行信号合并和平均的该多个像素电路,例如图2和图4所示。

54.可选地,在一种实现方式中,输出电路320包括运算放大器,该运算放大器包括第一输入端和第二输入端。其中,该多个像素电路的第一输出端与运算放大器的第一输入端相连,该多个像素电路的第二输出端与运算放大器的第二输入端相连。

55.在图2所示的方式中,是先将该多个像素电路的输出信号分别通过多个输出电路320读出,并通过多个采样电路330分别进行采样和保持,然后再进行信号合并和平均。而在该实施例中,是将需要进行信号合并和平均的该多个像素电路的两个输出分别作为输出电路320的两个输入,从而使该多个像素电路的输出信号在输出电路320内完成合并和平均,大幅度地减少了输出电路320的数量和采样电路330的数量,极大地降低了图像传感器的面积和功耗,并降低了成本。

56.为了对该实施例中的图像传感器300有更清楚地说明,下面以图4为例,详细描述图像传感器300的工作原理。其中,图4中的row表示行,col表示列。图4仅示出了像素电路阵列310中的4个子阵列,每个子阵列包括2

×

2个像素电路,编号分别为1、2、3和4。每个子阵列也可以包括其他数量的像素电路,例如每个子阵列包括r

×

r个像素电路,其中r>1。图4所示仅为示例,不应对本申请的保护范围造成限制。另外,该像素电路阵列310中包括的子阵列也可以具有其他数量。例如,像素电路阵列310可以包括p

×

q

×

m个子阵列,p和q为正整数,其中,m表示需要对多少个像素电路的输出信号进行信号合并和平均,例如m=4。

57.如图4所示的像素电路阵列110,4个子阵列中编号为1的像素电路的输出信号需要进行信号合并和平均,编号为2的像素电路的输出信号需要进行信号合并和平均,编号为3

的像素电路的输出信号需要进行信号合并和平均,编号为4的像素电路的输出信号需要进行信号合并和平均。

58.应理解,每4个子阵列中的编号相同的像素电路的输出信号对应的该信号均值,可以作为图像传感器300所采集的一幅图像中的一个像素点的像素数据。其中,当像素电路阵列310包括p

×

q

×

m个子阵列时,图像传感器300所采集的一幅图像包括p

×

q个像素点,其中需要对m个像素电路的输出信号进行信号合并和平均。例如,m=4时,4个像素电路1的输出信号对应的信号均值作为像素电路1的像素数据,4个像素电路2的输出信号对应的信号均值作为像素电路2的像素数据,4个像素电路2的输出信号对应的信号均值作为像素电路2的像素数据,4个像素电路4的输出信号对应的信号均值作为像素电路4的像素数据,等等。

59.以4个像素电路1为例,在第i行和第i+2行被选通时,第i行第j列的像素电路1、第i+2行第j列的像素电路1、第i行第j+2列的像素电路1、以及第i+2行第j+2列的像素电路1均被选通。

60.4个像素电路1的输出信号outn被输入至对应的输出电路320的同一输入端,4个像素电路1的输出信号outp被输入至对应的输出电路320的另一输入端。也就是说,第i行第j列的像素电路1和第i+2行第j列的像素电路1输出的outn<j>,以及第i行第j+2列和第i+2行第j+2列的像素电路1输出outn<j+2>被输入至对应的输出电路320的相同输入端。并且第i行第j列的像素电路1和第i+2行第j列的像素电路1输出的outp<j>,以及第i行第j+2列和第i+2行第j+2列的像素电路1输出outp<j+2>输入至该输出电路320的另一输入端。

61.该输出电路320接收4个像素电路1的输出信号outn和outp,并输出out1,其中out1即为合并和平均后的4个像素电路1的输出信号。信号out1被对应的采样电路330采样和保持,最终输出合并和平均后的数据,分别记为v

rst

和v

sig

。其中,v

rst

和v

sig

分别是曝光前后两次采集的信号,对这两个信号进行相关双采样后,可以消除一定的噪声信号,接着将相关双采样后的信号输入至pga电路370和adc电路380进行放大和模数转换,得到像素电路1的像素数据。

62.在第i行和第i+2行选通时,第i行第j+1列的像素电路2、第i+2行第j+1列的像素电路1、第i行第j+3列的像素电路1、以及第i+2行第j+3列的像素电路2均被选通。这4个像素电路2经过类似的过程,最终也可以得到像素电路2对应v

rst

和v

sig

,对这两个信号进行相关双采样后,输入至pga电路170和adc电路180进行放大和模数转换,得到像素电路2的像素数据。

63.接着,在第i+1行和第i+3行选通时,对4个像素电路3和4个像素电路4进行相似的操作,最终得到各自的像素数据。

64.可以看出,在图3中,编号相同的多个像素电路的输出信号在对应的输出电路320内部电路中完成合并和平均,大幅度地减少了输出电路320的数量和采样电路330的数量,极大地降低了图像传感器的面积和功耗。

65.本申请实施例对像素电路阵列310中的各个像素电路的结构不做限定。

66.可选地,在一种实现方式中,该像素电路还包括光电二极管、寄生电容器、复位开关管和传输管。

67.其中,该光电二极管的正极接地,该光电二极管的负极与该传输管的源极相连,该传输管的栅极由传输信号控制,该传输管的漏极与该寄生电容器的一端、该源跟随输入管

的栅极、以及该复位开关管的源极相连,该寄生电容器的另一端接地,该复位开关管的漏极接复位电压,该复位开关管的栅极由复位信号控制,该选通开关管的栅极由选通信号控制,该源跟随输入管的源极和该选通开关管的漏极相连,该源跟随输入管的漏极一端和该选通开关管的源极一端分别作为该像素电路的第一输出端和第二输出端。

68.例如图5所示,一个像素电路包括光电二极管(photodiode,pd)、寄生电容器c

fd

、传输管m1、复位开关管m2、源跟随输入管m3和选通开关管m4。该复位开关管m2用于对光电二极管pd进行复位。该选通开关管m4开启时,表明该像素电路当前被选通,以进行信号合并和平均。

69.其中,光电二极管pd的正极接地,光电二极管pd的负极接传输管m1的源极,传输管m1的栅极由传输信号tx控制,传输管m1的漏极分别与寄生电容器c

fd

的一端、源跟随输入管m3的栅极以及复位开关管m2的源极相连,寄生电容器c

fd

的另一端接地,复位开关管的漏极接复位电压v

rst

,复位开关管的栅极由复位信号rst控制,源跟随输入管m3的源极与选通开关管m4的漏极相连,跟随输入管m3的漏极接电源电压vccp,选通开关管m4的栅极由选通信号rsel控制。

70.当光线照射在光电二极管pd上产生电荷,该电荷在传输管m1打开时可以被寄生电容器c

fd

收集,从而在fd点上产生相应的电压,实现将光信号转换为电信号的过程。受fd点的电压的影响,源跟随输入管m3的漏极和选通开关管m4的源极分别产生电压信号outn和outp,即该像素电路的两个输出信号。

71.每一行像素电路的复位信号rst<i>相连,每一行像素电路的选通信号rsel<i>相连,i为行数。其中,rsel<i>=1时,该行像素被选通。

72.应理解,图5所示的像素电路仅仅为示例,本申请实施例也可以采用其他结构的像素电路,包括但不限于4t像素结构。

73.本申请实施例对输出电路320的结构也不做限定。

74.可选地,在一种实现方式中,输出电路320中的运算放大器还包括与其输出端相连的多组晶体管。其中,每组晶体管包括串联的第一晶体管和第二晶体管。该多组晶体管的数量(即组数)与需要进行信号合并和平均的该多个像素电路的数量相同。

75.进一步地,该第一晶体管和该像素电路的源跟随输入管的跨导相同,或者说,该第一晶体管和该像素电路的源跟随输入管的为相同的晶体管。

76.并且,该第二晶体管是与该像素电路的选通开关管相同的选通开关管。

77.优选地,该第一晶体管、该源跟随输入管、该第二晶体管、该选通开关管可以均为相同的晶体管。

78.例如,在一种实现方式中,该运算放大器还包括电流镜,该电流镜的一端与每个像素电路的源跟随输入管相连,该电流镜的另一端与每组晶体管中的第一晶体管相连。

79.进一步地,可选地,该运算放大器还包括电流源,该电流源的一端与每个像素电路的选通开关管相连,并与每组晶体管中的第二晶体管相连,该电流源的另一端接地。

80.又例如,在另一种实现方式中,该运算放大器还包括电流镜,该电流镜的一端与每个像素电路的选通开关管相连,该电流镜的另一端与每组晶体管中的第二晶体管相连。

81.进一步地,可选地,该运算放大器还包括电流源,该电流源的一端与每个像素电路的源跟随输入管相连,并与每组晶体管中的第一晶体管相连,该电流源的另一端接地。

82.例如图6所示的输出电路320,其包括运算放大器321。假设采用图5所示的像素电路,fd<1>至fd<n>分别为需要进行信号合并和平均的像素电路的源跟随输入管m3的栅极电压。pout,例如图4中的out1,是输出电路320的输出端的输出信号。该输出端与n组晶体管3212相连,n组晶体管3212之间并联,其中每组晶体管3212包括串联的晶体管m5和晶体管m6。具体地,该输出端可以与每组晶体管3212中的晶体管m5的栅极相连。

83.输出电路320的两个输入端中,其中一个输入端与各个像素电路的输出outp相连,另一个输入端与各个像素电路的输出outn相连。并且,输出电路320中的晶体管m5的跨导和晶体管m3的跨导相同,或者说,输出电路320中的晶体管m5和像素电路中的晶体管m3是相同的晶体管。并且,晶体管m6和晶体管m4为相同的选通开关管。由于输出电路320在进行信号合并和平均时,晶体管m6和晶体管m4作为开关均为导通状态,以下,为了便于理解,可以将晶体管m6和晶体管m4看作导线。

84.从图6中可以看出,运算放大器321中包括电流镜3211,电流镜3211的输入端电流和输出端电流分别为i1和i2,且i1=i2。

85.像素电路阵列310中各个像素电路的fd点的电压通常相差不大,即小信号假设成立。因此,fd<1>至fd<n>中的任意一个可以表示为fd<k>=vcm+

△

v<k>,其中,vcm为共模信号,

△

v<k>为小信号即fd<k>相对于vcm的微小变化。那么,输入端电流i1为:

86.i1=i(cm)+gm(1)

×△

v(1)+gm(2)

×△

v(2)+

……

gm(k)

×△

v(k)+

……

+gm(n)

×△

v(n)。

87.其中,gm(1)=gm(2)=

……

=gm(k)=

……

=gm(n)=gm。

88.因此,i1=i(cm)+gm

×△

v(1)+gm

×△

v(2)+

……

gm

×△

v(k)+

……

+gm

×△

v(n)。

89.由于电流镜3211的作用,输出端的电流i2=i1,且多组晶体管3212中的晶体管m5的跨导等于n

×

gm。因此,输出电路320的输出pout为:

90.pout=vcm+[gm

×△

v(1)+gm

×△

v(2)+

……

+gm

×△

v(k)+

……

+gm

×△

v(n)]/(n

×

gm)=vcm+[

△

v(1)+

△

v(2)+

……

+

△

v(k)+

……

+

△

v(n)]/n=(fd<1>+fd<2>+

……

+fd<k>+

……

+fd<n>)/n

[0091]

可见,输出电路320采用基于多输入跨导电流求和的该运算放大器321,实现了对fd<1>、fd<2>、

……

、fd<k>、

……

、fd<n>对应的输出信号的合并和平均。

[0092]

总体来看,图6中的输出电路320的运算放大器321采用了五管运算放大器的基本结构,并且,由于运算放大器321的输入端连接了需要进行信号合并和平均的n个像素电路,运算放大器的输出端连接了与n个像素电路中的源跟随输入m3管和选通开关管m4分别相同的n个晶体管m5和n个晶体管m6,从而实现了对n个像素电路的输出信号的合并和平均。

[0093]

图6中所示的源跟随输入m3管和选通开关管m4的位置是可以调换的,并同时调换晶体管m5和晶体管m6的位置。

[0094]

应理解,图6所示的输出电路仅仅为示例,本申请实施例也可以采用其他结构的输出电路,包括但不限于五管运算放大器。

[0095]

图7是基于图5的像素电路和图6的输出电路320的图像传感器的示意图。其中,图7仅示出了当前选通的4个像素电路1,即n=4。4个像素电路1的输出信号outp和outn分别输入输出电路320的两个输入端,输出电路320接收多个像素电路的输出信号outp和outn后,输出合并和平均后的信号pout。

[0096]

可选地,在一种实现方式中,采样电路330包括第一采样电容和第二采样电容,该第一采样电容和该第二采样电容用于在该像素电路曝光前后分别采集两次该信号均值,以实现相关双采样。

[0097]

例如图7所示,采样电路330与输出电路320相连,其中,第一采样电容c1通过开关k1与输出电路320的输出端相连,第二采样电容c2通过开关k2与输出电路320的输出端相连。可以控制开关k1和开关k2,使得在像素电路的曝光前后分别通过第一采样电容c1和第二采样电容c2采集两次信号均值,前一次是对复位电平v

rst

的采样,后一次是对曝光信号电平v

sig

的采样,两次采集的信号作差后可以消除复位噪声,因此提高了图像传感器的性能。

[0098]

本申请实施例还提供了一种指纹检测装置,该指纹检测装置包括上述本申请各种实施例中的图像传感器。该指纹检测装置可以设置于显示屏下方,以实现屏下指纹检测。

[0099]

当该图像传感器应用于指纹检测装置中,需要进行信号合并和平均的该多个像素电路接收到的光信号例如可以是手指返回的同一方向的光信号。或者说,该多个像素电路阵列的每个子阵列中的多个像素电路分别用于接收多个方向的光信号。

[0100]

该指纹检测装置的结构例如可以采用微透镜和一个或多个挡光层来实现对不同方向的光信号的接收。

[0101]

可选地,在一种实现方式中,该指纹检测装置还包括设置在所述每个子阵列上方的光路引导结构,该光路引导结构包括微透镜和设置在所述微透镜下方的多个挡光层,其中该多个挡光层中的最上方的挡光层设置有至少一个通光小孔且其余挡光层中的每个挡光层上设置多个通光小孔,以形成该多个方向的导光通道,该微透镜用于对显示屏上方的手指返回的光信号进行会聚,该多个方向的导光通道用于将对应方向的光信号引导至对应的像素电路。

[0102]

以图8和图9为例,上述编号相同的像素电路可以用于接收同一方向的光线,前述的像素电路1、像素电路2、像素电路3和像素电路4可以分别用于接收四个不同方向的光线。其中,图8是像素电路阵列310中的三个子阵列上方的光路导引结构的剖视图,图9是像素电路阵列310中的四个子阵列上方的光路引导结构的俯视图。

[0103]

图像传感器300的像素电路阵列310的上方设置有三个挡光层和一个微透镜层,最上方的挡光层上设置有一个通光小孔,其余挡光层中的每个挡光层上设置4个通光小孔以形成不同方向的四个导光通道,经微透镜会聚后的光信号分别经过这4个导光通道并分别到达4个像素电路。如图8所示,微透镜阵列210包括多个微透镜211,每个微透镜对应一个像素单元,每个像素单元包括4个像素。挡光层211上的开孔2211、挡光层222上的开孔2221、以及挡光层223上的开孔2231形成一个光接收方向,该方向的光信号可以被像素电路331接收;挡光层211上的开孔2211、挡光层222上的开孔2222和挡光层223上的开孔2232形成另一个光接收方向,该方向的光信号可以被像素电路332接收;类似地,图9的俯视图中示出了4个光接收方向。

[0104]

应理解,图8和图9仅仅为示例,其他能够实现多个接收方向的光路结构也可以应用于该指纹检测装置中。例如,也可以针对每个像素电路设置一个微透镜,即一个微透镜对应一个像素电路。

[0105]

另外,以上仅以四个方向的光线为例,这时像素电路阵列中的一个子阵列包括的像素电路为2

×

2个编号不同的像素电路。实际应用中也可以采用其他数量的光线方向,例

如一个子阵列中包括编号不同的两个像素电路,分别用于接收两个不同方向的光线。

[0106]

本申请实施例还提供了一种电子设备,该电子设备包括屏幕以及上述本申请各种实施例中的指纹检测装置。可选地,该指纹检测装置设置在该屏幕下方,以实现屏下光学指纹检测。

[0107]

作为示例而非限定,本申请实施例中的电子设备可以为终端设备、手机、平板电脑、笔记本电脑、台式机电脑、游戏设备、车载电子设备或穿戴式智能设备等便携式或移动计算设备,以及电子数据库、汽车、银行自动柜员机(automated teller machine,atm)等其他电子设备。该穿戴式智能设备包括功能全、尺寸大、可不依赖智能手机实现完整或部分功能的设备,例如智能手表或智能眼镜等;以及,只专注于某一类应用功能,且需要和其它设备如智能手机配合使用的设备,例如各类进行体征监测的智能手环、智能首饰等。

[0108]

需要说明的是,在不冲突的前提下,本申请描述的各个实施例和/或各个实施例中的技术特征可以任意的相互组合,组合之后得到的技术方案也应落入本申请的保护范围。

[0109]

应理解,本申请实施例中的具体的例子只是为了帮助本领域技术人员更好地理解本申请实施例,而非限制本申请实施例的范围,本领域技术人员可以在上述实施例的基础上进行各种改进和变形,而这些改进或者变形均落在本申请的保护范围内。

[0110]

以上所述,仅为本申请的具体实施方式,但本申请的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本申请揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本申请的保护范围之内。因此,本申请的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1