多接口控制设备的制作方法

1.本公开涉及控制技术领域,尤其涉及一种多接口控制设备。

背景技术:

2.随着科技的高速发展,控制技术也在不断的更新换代,对系统的精确测试工作也进入到了一个新的阶段。传统的测控系统通常采用单片机或dsp作为核心控制器,控制adc、dac、通信和其它外围电路的工作,以及对数据进行处理可控制。对于二维平台来说,单片机的时钟频率较低,难以适应复杂系统的要求,而dsp虽然可以实现较高的数据采集和计算处理,但其速度提高的同时,也提高了系统的成本。单一的使用cpu只能串行地执行一系列指令,处理速度太慢。应用fpga作为中心控制器,可以提高电路的设计的灵活性和小型化水平。fpga的设计输入方便,集成度高,工作速度快,逻辑单元功能强大。通过内部连线编程构成各种逻辑单元,完成组合逻辑和时序逻辑的功能,可以实现大规模电路,但现有设备接口单一。

技术实现要素:

3.有鉴于此,本公开提出了一种多接口控制设备,包括cpu、网络交换芯片、mcu、电源管理模块、网络芯片和vpx背板;

4.所述cpu与所述网络交换芯片通信连接;

5.所述cpu与所述mcu通信连接;

6.所述cpu与所述电源管理模块通信连接;

7.所述cpu与所述网络芯片通信连接;

8.所述cpu配置有iic接口,用于连接rtc器件;

9.所述cpu、所述网络芯片、所述网络交换芯片、所述mcu和所述电源管理模块均与所述vpx背板电连接。

10.在一种可能的实现方式中,所述cpu通过第一接口与所述网络芯片通信连接;

11.所述cpu通过第二接口与所述网络芯片通信连接;

12.所述cpu通过第三接口与所述网络芯片通信连接。

13.在一种可能的实现方式中,所述第一接口为rgmii接口;

14.所述第二接口为rgmii接口;

15.所述第三接口为sgmii接口。

16.在一种可能的实现方式中,所述cpu配置有缓存模块;

17.所述缓存模块的类型为ddr3;

18.所述缓存模块的容量为2gb。

19.在一种可能的实现方式中,所述cpu通过pcie接口与所述vpx背板电连接;

20.所述pcie接口为pcie

×

4。

21.在一种可能的实现方式中,所述cpu通过srio接口与所述vpx背板电连接;

22.所述srio接口为srio

×

4。

23.在一种可能的实现方式中,所述网络交换芯片与所述网络芯片通信连接。

24.在一种可能的实现方式中,所述mcu与所述电源管理模块通过gpio接口连接。

25.在一种可能的实现方式中,还包括网口;

26.所述网络芯片与所述网口电连接。

27.在一种可能的实现方式中,所述网口为rj45网口。

28.通过cpu、网络交换芯片、mcu、电源管理模块、网络芯片和vpx背板,cpu与网络交换芯片通信连接,cpu与mcu通信连接,cpu与电源管理模块通信连接,cpu与网络芯片通信连接,cpu配置有iic接口,用于连接rtc器件,cpu、网络芯片、网络交换芯片、mcu和电源管理模块均与vpx背板电连接。以使控制设备实现多个接口,从而可以分布式获取数据。

29.根据下面参考附图对示例性实施例的详细说明,本公开的其它特征及方面将变得清楚。

附图说明

30.包含在说明书中并且构成说明书的一部分的附图与说明书一起示出了本公开的示例性实施例、特征和方面,并且用于解释本公开的原理。

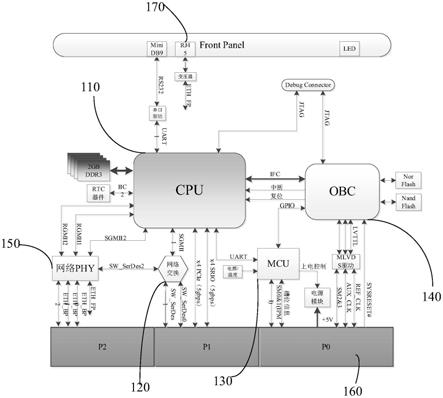

31.图1示出本公开实施例的多接口控制设备的示意图;

32.图2示出本公开实施例的多接口控制设备的电源模块示意图;

33.图3示出本公开实施例的多接口控制设备的时钟示意图。

具体实施方式

34.以下将参考附图详细说明本公开的各种示例性实施例、特征和方面。附图中相同的附图标记表示功能相同或相似的元件。尽管在附图中示出了实施例的各种方面,但是除非特别指出,不必按比例绘制附图。

35.其中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”、“轴向”、“径向”、“周向”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型或简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制。

36.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本实用新型的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

37.在这里专用的词“示例性”意为“用作例子、实施例或说明性”。这里作为“示例性”所说明的任何实施例不必解释为优于或好于其它实施例。

38.另外,为了更好的说明本公开,在下文的具体实施方式中给出了众多的具体细节。本领域技术人员应当理解,没有某些具体细节,本公开同样可以实施。在一些实例中,对于本领域技术人员熟知的方法、手段、元件和电路未作详细描述,以便于凸显本公开的主旨。

39.图1示出根据本公开一实施例的多接口控制设备的示意图。如图1所示,该多接口

控制设备包括:

40.cpu110、网络交换芯片120、mcu130、电源管理模块140、网络芯片150和vpx背板160,cpu110与网络交换芯片120通信连接,cpu110与mcu130通信连接,cpu110与电源管理模块140通信连接,cpu110与网络芯片150通信连接,cpu110配置有iic接口,用于连接rtc器件,cpu110、网络芯片150、网络交换芯片120、mcu130和电源管理模块140均与vpx背板160电连接。

41.通过cpu110、网络交换芯片120、mcu130、电源管理模块140、网络芯片150和vpx背板160,cpu110与网络交换芯片120通信连接,cpu110与mcu130通信连接,cpu110与电源管理模块140通信连接,cpu110与网络芯片150通信连接,cpu110配置有iic接口,用于连接rtc器件,cpu110、网络芯片150、网络交换芯片120、mcu130和电源管理模块140均与vpx背板160电连接。以使控制设备实现多个接口,从而可以分布式获取数据。

42.具体的,参见图1,在一种可能的实现方式中,cpu110通过第一接口与网络芯片150通信连接,cpu110通过第二接口与网络芯片150通信连接,cpu110通过第三接口与网络芯片150通信连接。举例来说,第一接口为rgmii接口,第二接口为rgmii接口,第三接口为sgmii接口。

43.进一步的,参见图1,在一种可能的实现方式中,cpu110配置有缓存模块,cpu110配置了缓存模块可以提高处理速度,举例来说,缓存模块的类型为ddr3,缓存模块的容量为2gb,缓存模块包括缓存单元,缓存单元的个数为两个,每个缓存单元的容量为1gb,速率≥1333mt/s,两个缓存单元组成双通道,这样就提高了cpu110的处理速度。

44.进一步的,参见图1,在一种可能的实现方式中,cpu110通过pcie接口与vpx背板160电连接,pcie接口为pcie

×

4,其传输速度可以达到5gbps。

45.进一步的,参见图1,在一种可能的实现方式中,cpu110通过srio接口与vpx背板160电连接,srio接口为srio

×

4,同样的,其传输速度可以达到5gbps,举例来说,cpu110引出一路srio

×

4到vpx背板160,同时,cpu110引出一路pcie

×

4到vpx背板160,可以通过srio

×

4接口和pcie

×

4直接将数据传输到cpu110中进行处理。

46.进一步的,参见图1,在一种可能的实现方式中,网络交换芯片120与网络芯片150通信连接。举例来说,cpu110通过sgmii接口与网络交换芯片120连接,网络交换芯片120引出两路serdes接口,两路serdes接口均与vpx背板160电连接,同时网络交换芯片120与网络芯片150电连接,同样的,也是通过serdes接口与网络芯片150电连接。

47.进一步的,参见图1,在一种可能的实现方式中,mcu130与电源管理模块140通过gpio接口连接。举例来说,cpu110通过一路uart与mcu130通信连接,mcu130通过sm接口与vpx背板160电连接。另外的,mcu130与温度控制器电连接,mcu130与温度传感器电连接,mcu130与电源控制芯片电连接,电源控制芯片与cpu110电连接,mcu130通过接收温度传感器的数据并向电源控制芯片发送指令用于实现健康管理功能。

48.在一种可能的实现方式中,还包括网口170,网络芯片150与网口170电连接。举例来说,网口170为rj45网口170,网口170的个数为一个,网口170用于连接外部主机,外部主机通过插入rj45网口170连接到网络芯片150,可以通过网络芯片150向cpu110发送调试信息进行调试设置。另外的,网络芯片150引出三路eth接口与vpx背板160电连接,可以同时接收数据,达到分布式接收。

49.另外的,电源管理模块140(obc)还配置有nor flash和nand flash。进一步的,参见图2,板卡的电源实现选用ltm4623、ltm4630和ltm4644模块电源,其中ltm4623为单路输出,输出电流为3a,ltm4630为2路输出,每路输出电流为18a,ltm4644为4路输出,每路输出电流为4a,电源轨如图3所示,此外,ltc4280为热插拔器件,可进行欠压、过压和过流保护。

50.进一步的,参见图3,各个部件的外接时钟需求如表一所示。

51.表一

52.序号时钟名称频率(mhz)属性数量1fpga工作时钟25lvcmos/lvttl12phy工作时钟25lvcmos/lvttl13cpu系统时钟100lvcmos/lvttl14cpu ddr时钟133.3lvcmos/lvttl15mcu工作时钟8lvcmos/lvttl16cpu serdes时钟125cml/lvpel/hcsl2

53.需要说明的是,尽管以上述各个实施例作为示例介绍了本公开多接口控制设备如上,但本领域技术人员能够理解,本公开应不限于此。事实上,用户完全可根据个人喜好和/或实际应用场景灵活设定多接口控制设备,只要达到所需功能即可。

54.这样,通过cpu110、网络交换芯片120、mcu130、电源管理模块140、网络芯片150和vpx背板160,cpu110与网络交换芯片120通信连接,cpu110与mcu130通信连接,cpu110与电源管理模块140通信连接,cpu110与网络芯片150通信连接,cpu110配置有iic接口,用于连接rtc器件,cpu110、网络芯片150、网络交换芯片120、mcu130和电源管理模块140均与vpx背板160电连接。以使控制设备实现多个接口,从而可以分布式获取数据。

55.以上已经描述了本公开的各实施例,上述说明是示例性的,并非穷尽性的,并且也不限于所披露的各实施例。在不偏离所说明的各实施例的范围和精神的情况下,对于本技术领域的普通技术人员来说许多修改和变更都是显而易见的。本文中所用术语的选择,旨在最好地解释各实施例的原理、实际应用或对市场中的技术改进,或者使本技术领域的其它普通技术人员能理解本文披露的各实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1