一种超宽带干扰源装置的制作方法

1.本实用新型涉及电信号干扰设备技术领域,特别涉及一种超宽带干扰源装置。

背景技术:

2.随着超宽带无线电干扰源装置在我国的商用,该超宽带无线电干扰源装置的延伸应用越来越多。超宽带无线电干扰源装置的体积和成本直接影响到超宽带无线电干扰源装置设备的商用性能。

3.现有技术中存在如下问题,传统的超宽带无线电干扰源装置主要方式,是多片dac合成超带宽方案。多片dac合成超带宽方案时,电路体积庞大,而且软件功能也复杂化,必须实现每一片dac的最大带宽,并且计算发射中心频点间隙,然后最终叠加各路dac发射出来的带宽信号。如果产品工作时,其中一片dac出故障,系统发射的干扰源也随之在响应的频点带宽失效。同时导致无法直接集成在一块板子上,具有体积大、功耗高的缺陷。

技术实现要素:

4.为此,需要提供一种超宽带干扰源装置,解决了传统的超宽带无线电干扰源装置体积大、功耗高的缺陷。

5.为实现上述目的,本实用新型提供了一种超宽带干扰源装置,包括收发模块、时钟模块、处理模块和管理模块,所述时钟模块与收发模块和处理模块电性连接,时钟模块给收发模块和处理模块提供参考时钟,所述处理模块与收发模块和管理模块电性连接,处理模块将干扰波型数据传输给收发模块,管理模块通过处理模块对收发模块进行配置。

6.进一步的,所述收发模块包括ad9371芯片、两个saw滤波器和两个gb接口,所述ad9371芯片设有发射端口,所述发射端口包括t1端口和t2端口,所述t1端口和t2端口分别与一个saw滤波器电性连接,所述两个saw滤波器分别与一个gb接口电性连接。

7.进一步的,所述时钟模块包括ad9528芯片,所述ad9528芯片的引脚37和引脚38分别与ad9371芯片的引脚e7和e8电性连接,所述ad9528芯片的引脚40和引脚41分别与ad9371芯片的引脚k3和k4电性连接,所述ad9371芯片的发射端t1引脚h14、j14电性连接宽带巴伦tcm1

‑

83+,进行差分转单端后与一个saw滤波器电性连接,再连接到gb接口,所述ad9371芯片的发射端t2引脚j1、h1电性连接宽带巴伦tcm1

‑

83+,进行差分转单端后与一个saw滤波器电性连接,再连接到gb接口,所述gb接口均连接有天线,信号经天线发射。

8.进一步的,所述时钟模块还包括osc2振荡器、j24连接器和电容c108、电容c109、电容c140、电容c141和电容673;所述电容c140和电容c141的一端与3.3v正电压和osc2振荡器的引脚4电性连接,所述电容c140和电容c141的另一端接地;所述osc2振荡器的引脚2接地,所述osc2振荡器的引脚3与电容c108的一端电性连接,所述电容c108的另一端与电容c673的一端和ad9528芯片的引脚2电性连接,所述电容c673的另一端与j24连接器的引脚1电性连接,所述j24连接器的引脚2

‑

5接地。

9.进一步的,所述时钟模块还包括osc1振荡器、电阻r52、电阻r496、电阻r497、电阻

r500

‑

505和电容c118、电容c130

‑

132;所述ad9528芯片的引脚8与电阻r52的一端电性连接,电阻r52的另一端与osc1振荡器的引脚1和电容c130的一端电性连接,所述电容c130的另一端接地,所述osc1振荡器的引脚3与地和电阻r497的一端电性连接,所述电阻r496和电阻r497串联并连接3.3v正电压;所述osc1振荡器的引脚6与电容c178的一端和3.3v正电压连接,所述电容c178和电容c131并联同时接地;所述osc1振荡器的引脚5与电容c132的一端和电阻r500的一端电性连接,所述电容c132的另一端与电阻r502、电阻r504的一端和芯片ad9528的引脚11电性连接,所述电阻r502的另一端接3.3v正电压和电阻r503的一端,所述电阻r503的另一端与电阻r505、电容c118的一端和芯片ad9528的引脚12电性连接,所述电容c118的另一端与电阻r501的一端和osc1振荡器的引脚4电性连接,所述电阻r500、电阻r501、电阻r504和电阻r505均接地。

10.进一步的,所述时钟模块还包括驱动芯片u65、电容c650、电阻r53、电阻r55和led灯1、led灯2;所述芯片ad9528的引脚55与驱动芯片u65的引脚1电性连接,所述芯片ad9528的引脚56与驱动芯片u65的引脚3电性连接,所述驱动芯片u65的引脚2接地,所述驱动芯片u65的引脚5与电容c650的一端电性连接,所述电容c650的另一端接地,所述驱动芯片u65的引脚4串联电阻r55和led灯2,所述led灯2接地,所述驱动芯片u65的引脚6串联电阻r53和led灯1,所述led灯1接地。

11.进一步的,所述时钟模块还包括j23连接器、j25连接器和电容c181、电容c707;所述芯片ad9528的引脚67与电容c181的一端电性连接,所述电容c181的另一端与j23连接器的引脚1电性连接,所述j23连接器的引脚2

‑

5接地,所述芯片ad9528的引脚70与电容c707的一端电性连接,所述电容c707的另一端与j25连接器的引脚1电性连接,所述j25连接器的引脚2

‑

5接地。

12.进一步的,所述处理模块包括fpga芯片、电容c245、电容c246和电阻r300、电阻r301、电阻r489,所述fpga芯片包括芯片u25

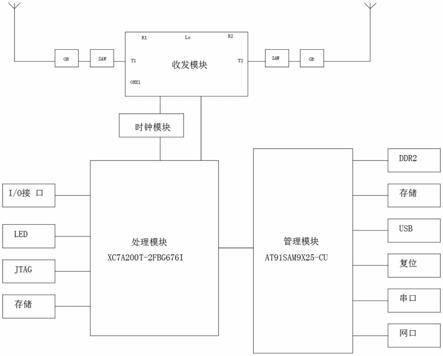

‑

9,所述芯片u25

‑

9的引脚g4与电阻r300的一端和ad9528芯片的引脚28电性连接,所述电阻r300的另一端与ad9528芯片的引脚29和芯片u25

‑

9的引脚f4电性连接,所述芯片u25

‑

9的引脚g5与电容c246的一端电性连接,所述电容c246的另一端与电阻r301的一端和ad9528芯片的引脚31电性连接,所述电阻r301的另一端与ad9528芯片的引脚32和电容c245的一端电性连接,所述电容c245的另一端与芯片u25

‑

9的引脚f5电性连接,所述芯片u25

‑

9的引脚h3与ad9371芯片的引脚j5电性连接。

13.进一步的,所述fpga芯片还包括芯片u25

‑

10,所述处理模块还包括电容c247

‑

c250,所述芯片u25

‑

10的引脚aa13与电容c247的一端电性连接,所述电容c247的另一端与ad9528芯片引脚25电性连接,所述芯片u25

‑

10的引脚ab13与电容c249的一端电性连接,所述电容c249的另一端与ad9528芯片引脚26电性连接,所述芯片u25

‑

10的引脚f11与电容c248的一端电性连接,所述电容c248的另一端与ad9528芯片引脚34电性连接,所述芯片u25

‑

10的引脚e11与电容c250的一端电性连接,所述电容c250的另一端与ad9528芯片引脚35电性连接。

14.进一步的,所述管理模块包括arm9芯片,所述arm9芯片包括芯片u12c,所述芯片u12c与fpga芯片电性连接,所述arm9芯片上设有ddr2接口、存储接口、usb接口、复位电路接口、串口接口和网口接口。

15.区别于现有技术,上述技术方案具有以下有益效果:

16.把所需发射信号数据经过处理模块处理后送到收发模块,设置收发模块的频率、带宽、通道参数,通过在发射端口就可以用频谱仪观察到到发射端所产生的宽带干扰频谱效果;管理模块把收发模块需要配置参数输送处理模块,再连接到收发模块,对收发模块进行相应的配置;用户可以通过管理模块进行人机交互。

附图说明

17.图1为具体实施方式所述干扰源装置系统框图;

18.图2为具体实施方式所述干扰源装置ad9371的部分电路原理图;

19.图3为具体实施方式所述干扰源装置ad9371的部分电路原理图;

20.图4为具体实施方式所述干扰源装置ad9371的部分电路原理图;

21.图5为具体实施方式所述干扰源装置ad9371的部分电路原理图;

22.图6为具体实施方式所述干扰源装置ad9528芯片的电路原理图;

23.图7为具体实施方式所述干扰源装置ad9528芯片的部分电路原理图;

24.图8为具体实施方式所述干扰源装置ad9528芯片的部分电路原理图;

25.图9为具体实施方式所述干扰源装置ad9528芯片的部分电路原理图;

26.图10为具体实施方式所述干扰源装置fpga芯片的部分电路原理图;

27.图11为具体实施方式所述干扰源装置fpga芯片的部分电路原理图;

28.图12为具体实施方式所述干扰源装置arm9的部分电路原理图。

具体实施方式

29.为详细说明技术方案的技术内容、构造特征、所实现目的及效果,以下结合具体实施例并配合附图详予说明。

30.请参阅图1,本实施例公开一种超宽带干扰源装置,包括,包括收发模块、时钟模块、处理模块和管理模块,时钟模块与收发模块和处理模块电性连接,时钟模块给收发模块和处理模块提供参考时钟,处理模块与收发模块和管理模块电性连接,处理模块将干扰波型数据传输给收发模块,控制模块通过管理模块对收发模块进行配置。

31.请参阅图2

‑

5,收发模块采用adi公司的ad9371 rf transceiver芯片,收发模块包括ad9371芯片、两个saw滤波器和两个gb接口,ad9371芯片设有发射端口,发射端口包括t1端口和t2端口,t1端口和t2端口的带宽是250m,t1端口和t2端口分别与一个saw滤波器电性连接,两个saw滤波器分别与一个gb接口电性连接。

32.请参阅图6

‑

9,时钟模块包括ad9528芯片,ad9528芯片的引脚37和引脚38分别与ad9371芯片的引脚e7和e8电性连接,ad9528芯片的引脚40和引脚41分别与ad9371芯片的引脚k3和k4电性连接,ad9371芯片的发射端t1引脚h14、j14电性连接宽带巴伦tcm1

‑

83+,进行差分转单端后与一个saw滤波器电性连接,再连接到gb接口,ad9371芯片的发射端t2引脚j1、h1电性连接宽带巴伦tcm1

‑

83+,进行差分转单端后与一个saw滤波器电性连接,再连接到gb接口,gb接口均连接有天线,信号经天线发射。

33.时钟模块还包括osc2振荡器、osc1振荡器、j23

‑

j25连接器、驱动芯片u65、电容c108、电容c109、电容c118、电容c130

‑

132、电容c140、电容c141、电容c181、电容673、电容c650、电容c707、电阻r52、电阻r53、电阻r55、电阻r496、电阻r497、电阻r500

‑

505和led灯1、

led灯2;

34.电容c140和电容c141的一端与3.3v正电压和osc2振荡器的引脚4电性连接,电容c140和电容c141的另一端接地;osc2振荡器的引脚2接地,osc2振荡器的引脚3与电容c108的一端电性连接,电容c108的另一端与电容c673的一端和ad9528芯片的引脚2电性连接,电容c673的另一端与j24连接器的引脚1电性连接,j24连接器的引脚2

‑

5接地。

35.ad9528芯片的引脚8与电阻r52的一端电性连接,电阻r52的另一端与osc1振荡器的引脚1和电容c130的一端电性连接,电容c130的另一端接地,osc1振荡器的引脚3与地和电阻r497的一端电性连接,电阻r496和电阻r497串联并连接3.3v正电压;osc1振荡器的引脚6与电容c178的一端和3.3v正电压连接,电容c178和电容c131并联同时接地;osc1振荡器的引脚5与电容c132的一端和电阻r500的一端电性连接,电容c132的另一端与电阻r502、电阻r504的一端和芯片ad9528的引脚11电性连接,电阻r502的另一端接3.3v正电压和电阻r503的一端,电阻r503的另一端与电阻r505、电容c118的一端和芯片ad9528的引脚12电性连接,电容c118的另一端与电阻r501的一端和osc1振荡器的引脚4电性连接,电阻r500、电阻r501、电阻r504和电阻r505均接地。

36.芯片ad9528的引脚55与驱动芯片u65的引脚1电性连接,芯片ad9528的引脚56与驱动芯片u65的引脚3电性连接,驱动芯片u65的引脚2接地,驱动芯片u65的引脚5与电容c650的一端电性连接,电容c650的另一端接地,驱动芯片u65的引脚4串联电阻r55和led灯2,led灯2接地,驱动芯片u65的引脚6串联电阻r53和led灯1,led灯1接地。

37.芯片ad9528的引脚67与电容c181的一端电性连接,电容c181的另一端与j23连接器的引脚1电性连接,j23连接器的引脚2

‑

5接地,芯片ad9528的引脚70与电容c707的一端电性连接,电容c707的另一端与j25连接器的引脚1电性连接,j25连接器的引脚2

‑

5接地。芯片ad9528给ad9371 rf transceiver芯片、fpga芯片提供系统所需高稳定度的参考时钟。

38.请参阅图10

‑

11,处理模块包括fpga芯片、电容c245

‑

c250和电阻r300、电阻r301、电阻r489,fpga芯片上设有i/o接口、led接口、jtag接口和存储接口,fpga芯片包括芯片u25

‑

9和芯片u25

‑

10,芯片u25

‑

9和u25

‑

10均为xilinx公司的xc7a200t

‑

2fbg676i芯片,芯片u25

‑

9的引脚g4与电阻r300的一端和ad9528芯片的引脚28电性连接,电阻r300的另一端与ad9528芯片的引脚29和芯片u25

‑

9的引脚f4电性连接,芯片u25

‑

9的引脚g5与电容c246的一端电性连接,电容c246的另一端与电阻r301的一端和ad9528芯片的引脚31电性连接,电阻r301的另一端与ad9528芯片的引脚32和电容c245的一端电性连接,电容c245的另一端与芯片u25

‑

9的引脚f5电性连接,芯片u25

‑

9的引脚h3与ad9371芯片的引脚j5电性连接。

39.芯片u25

‑

10的引脚aa13与电容c247的一端电性连接,电容c247的另一端与ad9528芯片引脚25电性连接,芯片u25

‑

10的引脚ab13与电容c249的一端电性连接,电容c249的另一端与ad9528芯片引脚26电性连接,芯片u25

‑

10的引脚f11与电容c248的一端电性连接,电容c248的另一端与ad9528芯片引脚34电性连接,芯片u25

‑

10的引脚e11与电容c250的一端电性连接,电容c250的另一端与ad9528芯片引脚35电性连接。

40.fpga芯片的外挂的存储芯片用于存储系统的固件,fpga芯片预留的i/o可用于用户扩展接口和测试端口,fpga芯片的led灯用于指示系统的工作状态。fpga芯片的jtag接口可以系统在线调试、下载程序接口。

41.请参阅图12,管理模块包括arm9芯片,arm9芯片包括芯片u12c,所述芯片u12c与

fpga芯片电性连接,arm9芯片上设有ddr2接口、存储接口、usb接口、复位电路接口、串口接口和网口接口。用户可以通过网口或串口监控系统的运行状态,arm9的外设存储器用于存储操作系统文件,usb接口可外接设备,或系统固件升级下载,复位按键,可进行在线复位重启。

42.在使用时,将需要发射信号数据经过fpga处理完送到ad9371 rf transceiver芯片,设置ad9371芯片的频率、带宽、通道参数,通过在发射端口就可以用频谱仪观察到到发射端所产生的宽带干扰频谱效果;arm9芯片把ad9371芯片需要配置参数输送fpga芯片,再连接到ad9371芯片,对ad9371芯片进行相应的配置;用户可以通过arm9芯片进行人机交互。

43.需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者终端设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者终端设备所固有的要素。在没有更多限制的情况下,由语句“包括

……”

或“包含

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者终端设备中还存在另外的要素。此外,在本文中,“大于”、“小于”、“超过”等理解为不包括本数;“以上”、“以下”、“以内”等理解为包括本数。

44.尽管已经对上述各实施例进行了描述,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例做出另外的变更和修改,所以以上所述仅为本实用新型的实施例,并非因此限制本实用新型的专利保护范围,凡是利用本实用新型说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本实用新型的专利保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1