实现针对北斗信号进行5G信号干扰滤除的装置的制作方法

实现针对北斗信号进行5g信号干扰滤除的装置

技术领域

1.本发明涉及北斗信号分析处理领域,尤其涉及5g干扰滤除领域,具体是指一种实现针对北斗信号进行5g信号干扰滤除的装置。

背景技术:

2.随着5g建设的快速增加,基站的大批量部署,由于5g nr(2.6ghz)系统对北斗系统rdss业务频段的邻频干扰以及重叠覆盖问题,导致在北斗接收机,尤其是地面接收站在特定频段受到严重干扰,不能正常接收北斗信号,因此在北斗接收机前端研发一款可以滤除5g干扰的设备已迫在眉睫。

3.本发明提供了一种北斗信号5g干扰滤除设备,通过信号接收单元经过下变频、宽带解调器及adc(模数转换器)获取北斗与5g信号共存的复合数字信号;在北斗信号干扰滤除单元中提取当前频点的5g信号,再通过lmmse(贝叶斯估计理论)进行信道估计,还原5g信号;使用在信号接收单元提取的复合数字信号去除还原的5g信号,得到较为纯净的北斗信号;通过信号发生单元,把还原后的北斗数字信号数据送入dac(数模转换器),经过宽带调制器和一级变频还原到接收信号的功率和频率,发送给北斗接收机完成北斗信号的5g干扰滤除。

技术实现要素:

4.本发明的目的是克服了上述现有技术的缺点,提供了一种满足还原性好、操作简便、适用范围较为广泛的实现针对北斗信号进行5g信号干扰滤除的装置。

5.为了实现上述目的,本发明的实现针对北斗信号进行5g信号干扰滤除的装置如下:

6.该实现针对北斗信号进行5g信号干扰滤除的装置,其主要特点是,所述的装置包括信号接收单元、北斗干扰信号滤除单元和信号发生单元,所述的信号接收单元的输出端与北斗干扰信号滤除单元的输入端相连接,所述的北斗干扰信号滤除单元的输出端相连与信号发生单元的输入端相连接,所述的信号接收单元用于获取北斗加5g复合数字基带信号,所述的北斗干扰信号滤除单元用于提取5g信号、信道估计、5g信号还原及5g干扰信号去除,并还原北斗信号,所述的信号发生单元,用于把去除干扰的北斗信号转换成模拟信号发送给北斗接收机。

7.较佳地,所述的信号接收单元包括第一低噪放、带通滤波器、第二低噪放、混频器、第一锁相环、中频放大器、中频带通滤波器、宽带解调器、第二锁相环、数模转换器和dds时钟;所述的第一低噪放接收信号,输出端与带通滤波器组的输入端相连,带通滤波器组的输出端通过第二低噪放与混频器相连,第一锁相环的输出端与混频器的输入端相连,混频器的输出端通过中频放大器和中频带通滤波器与宽带解调器的输入端相连,第二锁相环的输出端与宽带解调器的输入端相连,宽带解调器的输出端与数模转换器的输入端相连,数模转换器的输入端与dds时钟的输入端相连,所述的第一低噪放用于提高接收灵敏度,保证正

常接收的功率较小的北斗信号,所述的带通滤波器组用于接收信号不受通道杂散和镜像频率的干扰,所述的第二低噪放用于补偿滤波器组带来的信号衰减。

8.较佳地,所述的第一锁相环、第二锁相环和dds时钟的参考时钟均为19.2mhz。

9.较佳地,所述的北斗干扰信号滤除单元包括数字信号处理器、fpga、第一ddr3和第二ddr3,dsp的输入输出端通过pcie接口与fpga的输入输出端相连,数字信号处理器的输入输出端分别与第一ddr3和第二ddr3的输入输出端相连,fpga的输入输出端分别与第一ddr3和第二ddr3的输入端相连,

10.fpga将采样数据存储在第一ddr3,数字信号处理器从第一ddr3提取数字基带信号,利用数字信号处理器的多处理内核并行处理基带数据,进行5g信号提取以及gnss信号还原,存储到第二ddr3的指定地址,fpga进行5g信号消除后,传输至信号发生单元;fpga还将采样数据存储在第二ddr3的指定地址,数字信号处理器处理基带数据存储到第一ddr3的指定地址,经过fpga处理后传输至信号发生单元。

11.较佳地,所述的信号发生单元包括第二宽带调制器、第二模数转换器、第二dds时钟、中频带通滤波器、中频放大器、混频器、第三锁相环、第四锁相环、两级放大器和一级低通滤波器,第二宽带调制器的输入端与第二模数转换器的输出端相连,第二模数转换器的输入端与第二dds时钟的输入端相连,所述的第二宽带调制器的输出端通过中频带通滤波器和中频放大器与混频器的输入端相连,第三锁相环的输出端与第二宽带调制器的输入端相连,所述的混频器的输入端与第四锁相环的输出端相连,所述的混频器的输出端通过两级放大器和一级低通滤波器与输出端相连,所述的两级放大器用于补偿混频器带来的信号损失,所述的低通滤波器用于抑制混频的高频分量。

12.较佳地,所述的第二dds时钟的采样时钟为491.52mhz,第三锁相环的输出频率为1070mhz。

13.采用了本发明的实现针对北斗信号进行5g信号干扰滤除的装置,通过简化接收方案快速获取数字基带数据,通过dsp、fpga与两级ddr3的乒乓操着实现数据的实时处理,以实现基带数据处理实时性和避免数据丢失的可能性;通过优化处理的信道估计算法保证了在去除5g干扰信号的同时,确保北斗信号的无失真还原。

附图说明

14.图1为本发明的实现针对北斗信号进行5g信号干扰滤除的装置的原理框图。

15.图2为本发明的实现针对北斗信号进行5g信号干扰滤除的装置的信号接收单元的原理框图。

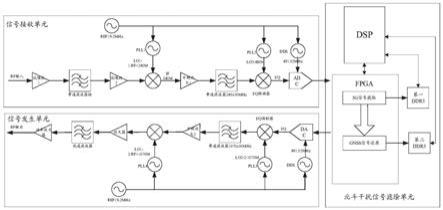

16.图3为本发明的实现针对北斗信号进行5g信号干扰滤除的装置的北斗信号干扰滤除单元的原理框图。

17.图4为本发明的实现针对北斗信号进行5g信号干扰滤除的装置的信号发生单元的原理框图。

具体实施方式

18.为了能够更清楚地描述本发明的技术内容,下面结合具体实施例来进行进一步的描述。

19.本发明的该实现针对北斗信号进行5g信号干扰滤除的装置,其中包括信号接收单元、北斗干扰信号滤除单元和信号发生单元,所述的信号接收单元的输出端与北斗干扰信号滤除单元的输入端相连接,所述的北斗干扰信号滤除单元的输出端相连与信号发生单元的输入端相连接,所述的信号接收单元用于获取北斗加5g复合数字基带信号,所述的北斗干扰信号滤除单元用于提取5g信号、信道估计、5g信号还原及5g干扰信号去除,并还原北斗信号,所述的信号发生单元,用于把去除干扰的北斗信号转换成模拟信号发送给北斗接收机。

20.作为本发明的优选实施方式,所述的信号接收单元包括第一低噪放、带通滤波器、第二低噪放、混频器、第一锁相环、中频放大器、中频带通滤波器、宽带解调器、第二锁相环、数模转换器和dds时钟;所述的第一低噪放接收信号,输出端与带通滤波器组的输入端相连,带通滤波器组的输出端通过第二低噪放与混频器相连,第一锁相环的输出端与混频器的输入端相连,混频器的输出端通过中频放大器和中频带通滤波器与宽带解调器的输入端相连,第二锁相环的输出端与宽带解调器的输入端相连,宽带解调器的输出端与数模转换器的输入端相连,数模转换器的输入端与dds时钟的输入端相连,所述的第一低噪放用于提高接收灵敏度,保证正常接收的功率较小的北斗信号,所述的带通滤波器组用于接收信号不受通道杂散和镜像频率的干扰,所述的第二低噪放用于补偿滤波器组带来的信号衰减。

21.作为本发明的优选实施方式,所述的第一锁相环、第二锁相环和dds时钟的参考时钟均为19.2mhz。

22.作为本发明的优选实施方式,所述的北斗干扰信号滤除单元包括数字信号处理器、fpga、第一ddr3和第二ddr3,dsp的输入输出端通过pcie接口与fpga的输入输出端相连,数字信号处理器的输入输出端分别与第一ddr3和第二ddr3的输入输出端相连,fpga的输入输出端分别与第一ddr3和第二ddr3的输入端相连,

23.fpga将采样数据存储在第一ddr3,数字信号处理器从第一ddr3提取数字基带信号,利用数字信号处理器的多处理内核并行处理基带数据,进行5g信号提取以及gnss信号还原,存储到第二ddr3的指定地址,fpga进行5g信号消除后,传输至信号发生单元;fpga还将采样数据存储在第二ddr3的指定地址,数字信号处理器处理基带数据存储到第一ddr3的指定地址,经过fpga处理后传输至信号发生单元。

24.作为本发明的优选实施方式,所述的信号发生单元包括第二宽带调制器、第二模数转换器、第二dds时钟、中频带通滤波器、中频放大器、混频器、第三锁相环、第四锁相环、两级放大器和一级低通滤波器,第二宽带调制器的输入端与第二模数转换器的输出端相连,第二模数转换器的输入端与第二dds时钟的输入端相连,所述的第二宽带调制器的输出端通过中频带通滤波器和中频放大器与混频器的输入端相连,第三锁相环的输出端与第二宽带调制器的输入端相连,所述的混频器的输入端与第四锁相环的输出端相连,所述的混频器的输出端通过两级放大器和一级低通滤波器与输出端相连,所述的两级放大器用于补偿混频器带来的信号损失,所述的低通滤波器用于抑制混频的高频分量。

25.作为本发明的优选实施方式,所述的第二dds时钟的采样时钟为491.52mhz,第三锁相环的输出频率为1070mhz。

26.本发明的具体实施方式中,涉及一种北斗信号5g干扰滤除设备,包括信号接收单元、信号发生单元及北斗干扰信号滤除单元,信号接收单元输出端与北斗干扰信号滤除单

元的输入端相连;北斗干扰信号滤除单元的输出端相连与信号发生单元的输入端相连。由于在特定频段,北斗与5g信号有重叠覆盖的情况,导致北斗信号无法正常接收,通过信号接收单元经过下变频、宽带解调器及adc(模数转换器)获取北斗与5g信号共存的复合数字信号;在北斗干扰信号滤除单元中提取当前频点的5g信号,再通过lmmse(贝叶斯估计理论)进行信道估计,还原5g信号;使用在信号接收单元提取的复合数字信号去除还原的5g信号,得到较为纯净的北斗信号;通过信号发生单元,把还原后的北斗数字信号数据送入dac(数模转换器),经过宽带调制器和一级变频还原到接收信号的功率和频率,发送给北斗接收机完成北斗信号的5g干扰滤除。

27.如图1所示,北斗信号5g干扰滤除设备包括信号接收单元、信号发生单元及北斗干扰信号滤除单元;信号接收单元输出端与北斗干扰信号滤除单元的输入端相连;北斗干扰信号滤除单元的输出端相连与信号发生单元的输入端相连。

28.如图2所示,所述的信号接收单元,用于获取北斗加5g复合数字基带信号,其处理过程如下:

29.1)信号通过增益为15db的低噪放1与带通滤波器组的输入端相连;低噪放1是为了提高接收灵敏度,保证正常接收的功率较小的北斗信号;带通滤波器组是为了接收信号不受通道杂散和镜像频率的干扰。

30.2)带通滤波器组的输出端相连,通过10db的低噪放2与混频器相连;pll1(锁相环)输出端与混频器的输入端相连,其中pll1的输出频率为信号接收频率rf+240mh在,保证输出240mhz的中频信号;低噪放2是为了补偿滤波器组带来的信号衰减。

31.3)混频器的输出端通过15db中频放大器及240mhz通带100mhz的中频带通滤波器与宽带解调器的输入端相连;pll2(锁相环)输出端与宽带解调器的输入端相连;pll2的输出频率为480mhz;

32.4)宽带解调器的输出端与adc(数模转换器)的输入端相连,adc(数模转换器)的输入端与dds时钟的输入端相连,dds提供采样时钟为491.52mhz。

33.如图3所示,所述的ppl1、pll2以及dds的参考时钟要保证同源,并且均为19.2mhz。

34.所述的北斗干扰信号滤除单元,用于提取5g信号、信道估计、5g信号还原及5g干扰信号去除,还原北斗信号,其处理过程如下:

35.1)dsp的输入输出端通过pcie接口与fpga的输入输出端相连;dsp的输入输出端分别与第一个ddr3、第二个ddr3的输入输出端相连;fpga的输入输出端分别与第一个ddr3、第二个ddr3的输入输出端相连;

36.2)fpga把adc采样的数据先存储在第一个ddr3,dsp从第一个ddr3提取数字基带信号,利用dsp多处理内核并行处理基带数据,保证低延时进行5g信号提取并还原,并存储到第二个ddr3指定地址,fpga进行5g信号消除后,送给信号发生单元的dac进行数模转换。

37.3)在数据处理过程中,fpga把adc采样的数据再存储在第二个ddr3的指定地址,dsp再处理基带数据存储到第一个ddr3的指定地址,fpga处理后再发给dac。

38.如图4所示,所述的信号发生单元,用于把去除干扰的北斗信号转换成模拟信号发送给北斗接收机,其处理过程如下:

39.1)宽带调制器的输入端与dac(模数转换器)的输出端相连,dac(模数转换器)的输入端与dds时钟的输入端相连,dds提供采样时钟为491.52mhz。

40.2)宽带调制器的输出端通过20db中频放大器及1070mhz通带100mhz的中频带通滤波器与混频器输入端相连;pll3(锁相环)输出端与宽带调制器的输入端相连;pll3的输出频率为1070mhz;

41.3)混频器输入端与pll4(锁相环)输出端相连;其中pll4的输出频率为信号最终输出频率rf1+1070mhz;

42.4)混频器输出端通过谅解放大器和一级低通滤波与输出端相连;两级放大为了补偿混频器带来的信号损失,低通滤波是为了抑制混频的高频分量。

43.所述的ppl3、pll4以及dds的参考时钟要保证同源,并且均为19.2mhz。

44.采用了本发明的实现针对北斗信号进行5g信号干扰滤除的装置,通过简化接收方案快速获取数字基带数据,通过dsp、fpga与两级ddr3的乒乓操着实现数据的实时处理,以实现基带数据处理实时性和避免数据丢失的可能性;通过优化处理的信道估计算法保证了在去除5g干扰信号的同时,确保北斗信号的无失真还原。

45.在此说明书中,本发明已参照其特定的实施例作了描述。但是,很显然仍可以作出各种修改和变换而不背离本发明的精神和范围。因此,说明书和附图应被认为是说明性的而非限制性的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1