一种服务器密码机的数据处理方法、装置及服务器密码机与流程

1.本发明涉及计算机技术领域,特别是指一种服务器密码机的数据处理方法、装置及服务器密码机。

背景技术:

2.现有技术中,服务器密码机大多采用通用型或定制型主板、cpu(中央处理器)模块、外接pci

‑

e密码卡形式组成。cpu模块收发数据包会消耗大量cpu和系统中断资源,尤其在使用万兆网卡的情况下,万兆网卡满速运行需要至少4核心以上cpu,并且消耗20%左右的cpu资源。cpu调用pci

‑

e密码卡进行密码算法运算,也需要消耗大量cpu资源,进一步加重cpu的运行负担。并且现有的pci

‑

e密码卡的密码算法运算能力普遍不是很高,能达到10gbps加解密速率的产品屈指可数,无法满足日益增大的密码运算需求。

技术实现要素:

3.本发明要解决的技术问题是如何提供一种服务器密码机的数据处理方法、装置及服务器密码机。释放了服务器密码机的中央处理器cpu的运算能力,缩减了软件开发的难度;提高了安全性和快速响应能力;增大了系统的算法处理性能;保证了服务器密码机的安全性。

4.为解决上述技术问题,本发明的技术方案如下:本发明提供了一种服务器密码机的数据处理方法,所述方法包括:上层软件模块向底层硬件模块发送控制指令;接收所述底层硬件模块根据所述控制指令对所述底层硬件模块进行解析传输的数据进行处理得到的处理结果;所述底层硬件包括:中央处理器cpu、与所述cpu通信连接的现场可编程门阵列fpga接口模块以及所述fpga接口模块通信连接的算法fpga模块;所述fpga接口模块根据上层软件模块的控制指令对其接收到的数据报文发送至所述算法fpga模块进行安全运算处理或者发送至所述cpu处理。

5.可选的,所述fpga接口模块根据上层软件模块的控制指令对其接收到的数据报文发送至所述算法fpga模块进行安全运算处理或者发送至所述cpu处理,包括:所述fpga接口模块根据上层软件模块的控制指令对其接收到的数据报文进行解析,得到解析结果;若所述解析结果表示所述数据报文是需要进行安全处理的业务数据,将所述数据报文发送至所述算法fpga模块进行安全运算处理,并接收所述算法fpga模块返回的运算结果;若所述解析结果表示所述数据报文是不需要进行安全处理的控制数据,将所述控制数据发送至所述cpu处理。

6.可选的,所述接口fpga模块通过中转fpga模块与所述cpu通信连接;所述接口fpga模块将所述控制数据通过所述中转fpga模块发送至所述cpu处理

和/或接收所述cpu发送的配置信息;所述配置信息由上层软件模块中的系统参数配置模块产生并配置给所述cpu。

7.可选的,所述接口fpga模块与数据安全模块通信连接;所述接口fpga模块接收所述cpu发送的密钥管理指令,将所述密钥管理指令发送给所述数据安全模块,由所述数据安全模块根据所述密钥管理指令进行以下至少一项操作:对称密钥或者非对称密钥的生成、删除、导入、导出、备份、恢复。

8.可选的,对所述数据进行解析,得到解析结果,包括:对所述数据进行解析,获得数据报文的字段信息;所述字段信息包括以下至少一项:前导码字段、mac字段、ip地址、报文类型头、净荷以及校验字段,所述mac字段包括源mac以及目的mac,所述ip地址包括源ip以及目的ip。

9.可选的,若所述解析结果表示所述数据报文是需要进行安全处理的业务数据,将所述数据报文发送至所述算法fpga模块进行安全运算处理,包括:若所述解析结果表示所述数据报文是需要进行安全处理的业务数据,且所述数据报文目的地址是本设备的地址,则将数据报文送入算法fpga模块进行处理。

10.可选的,接收所述算法fpga模块返回的运算结果,包括:接收所述算法fpga模块对所述数据报文采用预设安全算法进行加密和/或解密的运算结果。

11.本发明提供一种服务器密码机的数据处理装置,应用于服务器密码机,所述装置包括:收发模块,用于接收上层软件模块的控制指令;处理模块,用于根据所述控制指令对底层硬件模块进行解析传输的数据进行处理,得到处理结果;所述底层硬件包括:中央处理器cpu、与所述cpu通信连接的现场可编程门阵列fpga接口模块以及所述fpga接口模块通信连接的算法fpga模块;所述fpga接口模块根据上层软件模块的控制指令对其接收到的数据报文发送至所述算法fpga模块进行安全运算处理或者发送至所述cpu处理;所述收发模块在所述底层硬件模块和上层软件模块之间传输所述处理结果。

12.本发明提供一种服务器密码机,包括:上层软件模块以及底层硬件模块;所述上层软件模块向所述底层硬件模块发送控制指令;所述上层软件模块接收所述底层硬件模块根据所述控制指令对所述底层硬件模块传输的数据进行处理的处理结果;所述底层硬件模块包括:中央处理器cpu、接口现场可编程门阵列fpga模块以及算法fpga模块;所述cpu与所述接口fpga模块通信连接;所述接口fpga模块与所述算法fpga模块通信连接;所述fpga接口模块根据上层软件模块的控制指令对其接收到的数据报文发送至所述算法fpga模块进行安全运算处理或者发送至所述cpu处理。

13.本发明提供一种计算机可读存储介质,存储指令,当所述指令在计算机上运行时,使得计算机执行如上述的方法。

14.本发明的上述方案至少包括以下有益效果:通过上层软件模块向底层硬件模块发送控制指令;接收所述底层硬件模块根据所述控制指令对所述底层硬件模块进行解析传输的数据进行处理,得到的处理结果;所述底

层硬件包括:中央处理器cpu、与所述cpu通信连接的现场可编程门阵列fpga接口模块以及所述fpga接口模块通信连接的算法fpga模块;所述fpga接口模块根据上层软件模块的控制指令对其接收到的数据报文发送至所述算法fpga模块进行安全运算处理或者发送至所述cpu处理。释放了中央处理器cpu的运算能力,缩减了软件开发的难度;提高了安全性和快速响应能力;增大了系统的算法处理性能;保证了服务器密码机的安全性。

附图说明

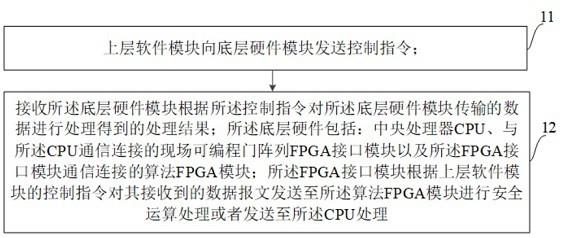

15.图1是本发明实施例的服务器密码机的数据处理方法的流程示意图;图2是本发明实施例的服务器密码机的上层软件模块的架构示意图;图3是本发明实施例的服务器密码机的cpu模块和接口fpga模块的分布式系统架构示意图;图4是本发明实施例的服务器密码机的算法fpga模块的结构示意图;图5是本发明实施例的服务器密码机的接口fpga模块的结构示意图;图6是本发明实施例的接口fpga模块对数据报文处理的流程示意图;图7是本发明实施例的服务器密码机的数据处理装置的模块示意图。

具体实施方式

16.下面将参照附图更详细地描述本公开的示例性实施例。虽然附图中显示了本公开的示例性实施例,然而应当理解,可以以各种形式实现本公开而不应被这里阐述的实施例所限制。相反,提供这些实施例是为了能够更透彻地理解本公开,并且能够将本公开的范围完整的传达给本领域的技术人员。

17.如图1所示,本发明的实施例提供一种服务器密码机的数据处理方法,所述方法包括:步骤11,上层软件模块向底层硬件模块发送控制指令;步骤12,接收所述底层硬件模块根据所述控制指令对所述底层硬件模块传输的数据进行处理,得到的处理结果;所述底层硬件包括:中央处理器cpu(central processing unit)、与所述cpu通信连接的现场可编程门阵列fpga(field programmable gate array)接口模块以及所述fpga接口模块通信连接的算法fpga模块;所述fpga接口模块根据上层软件模块的控制指令对其接收到的数据报文发送至所述算法fpga模块进行安全运算处理或者发送至所述cpu处理。

18.如图2所示,该实施例是基于硬件模块的运行,通过后台服务程序将上层软件模块向底层硬件模块发送控制指令,再接收底层硬件模块根据控制指令对底层硬件模块传输的数据进行处理,最终得到处理结果。提高了安全性和快速响应能力,保证了服务器密码机的安全性。这里的上层软件模块包括系统参数配置、密钥管理以及用户管理,后台服务程序通过数据通信与底层硬件模块之间传输数据。

19.如图2和图3所示,本发明一可选的实施例中,所述fpga接口模块根据上层软件模块的控制指令对其接收到的数据报文发送至所述算法fpga模块进行安全运算处理或者发送至所述cpu处理,包括:所述fpga接口模块根据上层软件模块的控制指令对其接收到的数据报文进行解

析,得到解析结果;若所述解析结果表示所述数据报文是需要进行安全处理的业务数据,将所述数据报文发送至所述算法fpga模块进行安全运算处理,并接收所述算法fpga模块返回的运算结果;若所述解析结果表示所述数据报文是不需要进行安全处理的控制数据,将所述控制数据发送至所述cpu处理。

20.本实施例是由cpu与fpga协同合作的数据处理;通过接口fpga模块根据上层软件模块的控制指令进行收发和/或解析数据报文,不再需要cpu模块去处理数据包的收发和解析工作,使cpu的运算能力得到了极大的释放,解决了对cpu过分依赖的问题,有效提高了cpu的运算效率。

21.如图3所示,本发明一可选的实施例中,所述接口fpga模块通过中转fpga模块与所述cpu通信连接;所述接口fpga模块将所述控制数据通过所述中转fpga模块发送至所述cpu处理和/或接收所述cpu发送的配置信息;所述配置信息由上层软件模块中的系统参数配置模块产生并配置给所述cpu;所述接口fpga模块与数据安全模块通信连接;所述接口fpga模块接收所述cpu发送的密钥管理指令,将所述密钥管理指令发送给所述数据安全模块,由所述数据安全模块根据所述密钥管理指令进行以下至少一项操作:对称密钥或者非对称密钥的生成、删除、导入、导出、备份、恢复。

22.该实施例中,接口fpga模块将控制数据通过中转fpga模块发送至cpu处理和/或接收cpu发送的由上层软件模块中的系统参数配置模块产生并配置的配置信息。接口fpga模块接收cpu模块发送的密钥管理指令,并发送给数据安全模块。

23.中转fpga模块,通过pci

‑

e总线与cpu模块相连,通过uart(universal asynchronous receiver/transmitter,通用异步收发传输器)总线与系统检测模块相连,通过rgmii(reduced gigabit media independent interface,精简吉比特介质独立接口)总线与接口fpga相连。中转fpga模块进行数据的转发,目的是将cpu模块、系统检测模块、接口fpga模块联系起来,数据可以相互传输。中转fpga模块实现了将cpu模块、系统检测模块、接口fpga模块相互联系起来,起到了数据的中转转发的作用,使得数据可以进行交互传输。

24.需要说明的是,cpu模块为软件运行提供了计算平台,cpu中的软件可以通过中转fpga模块将配置信息发送到接口fpga模块,还可以通过中转fpga模块获取系统检测模块的状态;系统监测模块在具体的实施例中可以用于检测服务器的电源状态、温度等状态,并根据相关状态控制风扇转速、电源通断等,同时外接rtc(real_time clock,实时时钟)时钟芯片以提供时钟相关信息。

25.接口fpga模块,通过rgmii总线与物理网口连接,可以同时提供千兆网络接口和万兆网络接口;通过rgmii总线与中转fpga模块连接,实现与cpu模块的通信;通过sram总线与数据安全模块连接,转发cpu模块用户管理、密钥管理的指令给数据安全模块;通过内部高速总线连接算法fpga模块,两片fpga之间的通信速率可达40gbps。接口fpga模块的主要作用是数据的收发、协议的解析和封装。

26.接口fpga模块的工作流程是从接口接收数据,进行网络协议解析,如数据需要算

法运算则将数据送到算法fpga模块,并将运算结果进行封装,将封装后的数据从接口发送出去;如数据是不需要算法运算的配置数据和管理数据,接口fpga模块会转发到cpu模块进行处理。

27.算法fpga模块内部设有sm3/sm4算法ip核集群,通过gpio(general

‑

purpose input/output,通用型的输入输出)分别连接sm1/sm2算法协处理器和随机数芯片;算法fpga模块提供的国密算法可供接口fpga模块调用,也可供cpu模块调用,具有很大的灵活性,提供了高速的sm3/sm4算法与高速的sm1和sm2算法和真随机数功能,起到了提供随机数和国密sm1/sm2/sm3/sm4算法服务,其中,sm1算法和sm2算法由外部的专用算法芯片提供,可同时挂载多片专用算法芯片以提高sm1和sm2算法的速率,sm1算法最高速率可达9gbps,sm2算法签名运算最高可达36万次/秒,sm3和sm4算法的速率可达10gbps以上;另外,需要说明的是,sm3/sm4算法ip核集群是由多个算法ip核组成的,所有的算法ip核相互独立,可以同时运行,提供了极高的sm3/sm4算法速率。

28.如图4所示,一个具体的实施例1中,算法fpga模块通过pci

‑

e总线进行dma(直接存储访问)的ip core(intellectual property core,中断优先寄存器核,即ip核)与主机交互,通过axi stream总线利用软件axi stream interconnect分别连接sm3算法池、sm4算法池以及arm(acorn risc machine,arm处理器)的访问接口,最终通过emc(external memory controller,外部存储器控制器)与板载arm交互,这里ip核集群包括多个ip核。

29.接口fpga模块通过rgmii总线物理网口,该物理网口优选的可以提供千兆网络接口和万兆网络接口,通过rgmii总线与中转fpga模块连接,通过sram(static random

‑

access memory,静态随机存取存储器)与数据安全模块连接,通过内部高速data bus(数据总线)与算法fpga模块连接,其通信速率可达40gbps;实现了接口fpga模块与cpu之间的通信,还可以转发cpu模块的指令给数据安全模块,数据安全模块由符合规范的安全芯片组成,提供了对敏感数据的安全存储,实现与cpu模块配合完成管理操作,该管理操作包括密钥体系的管理和系统用户的管理;同时还实现了对数据报文的收发和/或解析,对数据报文的解析可以解析到ip层(网络层)和/或tcp/udp层(transmission control protocol/user datagram protocol, 传输控制协议/用户数据报协议),其对数据报文的收发和/或解析的整个过程都不需要cpu参与,减小了cpu运算负担,提高了cpu的运算效率。

30.如图5所示,一个具体的实施例2中,接口fpga模块内部进行数据的收发,其核心部分是axis_stream_switch(axis总线流交换机)模块,用于接收数据报文,并对数据报文进行解析,并进一步对数据进行高速转发,其外部挂载come rgmii接口、wx1860 rgmii接口、hsmd 1接口、hsmd2

‑

h2接口、hsh3接口、mcu(microcontroller unit,微控制单元)接口、config data operate(配置数据操作)、rgmii接口以及若干eth data depart(以太网数据部),用于axis stream格式转换;其中安全密码芯片ach512通过mcu接口与axis_stream_switch模块连接,ddr control(double data rate control,双倍速率控制)通过config data operate与axis_stream_switch模块连接,alg fpga 10g base(万兆以太网的应用层可编程逻辑门器件)通过gmii(gigabit medium independent interface,千兆媒体独立接口)与rgmii接口连接,eth phy #0(以太网物理层#0)和eth phy#1(以太网物理层#1)通过eth data depart与axis_stream_switch模块连接,实现了对数据报文的转发。

31.本实施例的硬件组成部分由中转fpga模块、接口fpga模块、算法fpga模块以及cpu

模块以及其他功能性模块共同组成,其中主要由接口fpga和算法fpga完成,基本不需要cpu模块参与;接口fpga模块接收到数据报文后进行协议解析,如果是需要进行安全处理的业务数据,接口fpga模块会直接把数据报文发送到算法fpga模块进行安全运算处理,运算完毕后算法fpga模块会把结果发送到接口fpga模块进行协议封装,接口fpga模块将封装好的数据报文从外网发送出去,整个过程不需要cpu模块的参与,仅有少量管理数据或者协商数据需要由接口fpga模块传递给cpu模块进行处理。这种仅需cpu模块进行少量参与的业务处理方式,隔绝了业务数据和操作系统的联系,很大程度上也隔绝了系统被攻击的可能性,保障了安全性。

32.本发明一可选的实施例中,对所述数据进行解析,得到解析结果,包括:对所述数据进行解析,获得数据报文的字段信息;所述字段信息包括以下至少一项:前导码字段、mac字段、ip地址、报文类型头、净荷以及校验字段,所述mac字段包括源mac以及目的mac,所述ip地址包括源ip以及目的ip。

33.本实施例中数据报文的字段信息格式如表1所示:表1其中,preamble是前导码字段,mac是mac字段,ip header是ip地址包括ipv4或者ipv6,tcp/udp header是报文类型头,payload是净荷,crc是校验字段。

34.如图6所示,本发明一可选的实施例中,若所述解析结果表示所述数据报文是需要进行安全处理的业务数据,将所述数据报文发送至所述算法fpga模块进行安全运算处理,包括:若所述解析结果表示所述数据报文是需要进行安全处理的业务数据,且所述数据报文目的地址是本设备的地址,则将数据报文送入算法fpga模块进行处理。本发明一可选的实施例中,接收所述算法fpga模块返回的运算结果,包括:接收所述算法fpga模块对所述数据报文采用预设安全算法进行加密和/或解密的运算结果。

35.其中,安全算法包括以下至少一种算法:sm1算法;sm2算法;sm3算法;sm4算法;其中,所述sm3算法的ip核集群与所述sm4算法的ip核集群相互独立。

36.本实施例中,在接口fpga模块对数据报文进行处理,数据报文收发的接口有两种,一种是电口物理phy模块,在fpga转换成rgmii接口,另一种是sfp+光模块,其中电口物理phy模块优选的是1gbps的电口物理phy模块,sfp+光模块优选的是10gbps的sfp+光模块;本实施例中的服务器服务器密码机是一个终端设备,数据报文在服务器密码机中的传输过程包括:判断数据报文是否是传输控制协议tcp报文或用户数据报udp报文,如果是,解析出源端口地址和目的端口地址;若目的地址是本服务器密码机的端口的地址,若所述数据报文是不需要进行安全运算的控制数据,则将数据报文送入cpu data fifo(中央处理器数据先进先出)模块,再经由rgmii送入cpu模块进行处理,若将数据报文是需要进行安全运算的业务数据,则通过process data fifo(数据处理先进先出)模块送入算法fpga模块进行处理;通过上述数据报文经接口fpga模块进行传输,可以实现接口fpga模块把数据报文发送到算法fpga模块进行安全运算处理的过程,从而减轻了cpu的运算负担。

37.数据报文的收发、解析以及安全处理都由硬件模块提供,为了实现cpu模块专注于管理服务,进一步减轻cpu模块的运行压力。

38.本发明的实施例还需要运行在底层硬件模块上的上层软件模块,上层软件模块用于软件与硬件之间的数据通信、系统参数配置、用户管理以及密钥管理等工作。

39.如图2所示,所述底层硬件包括:中央处理器cpu、与所述cpu通信连接的现场可编程门阵列fpga接口模块以及所述fpga接口模块通信连接的算法fpga模块;上层软件模块包括:系统参数配置子模块、用户管理子模块、密钥管理子模块以及后台服务程序模块,其中,1)系统参数配置子模块用于配置密码服务平台相关的参数,其参数包括接口fpga模块的外网mac地址、接口fpga模块的外网ip地址、源mac地址、源ip地址、日志级别以及日志存储位置,参数配置完,由cpu模块下发到对应模块进行处理;2)用户管理子模块用于密码服务平台上各种不同权限用户的操作,其操作包括用户创建、用户删除、用户登录以及用户登出。可以设置不同权限的用户以执行不同的操作,权限的分割保证了数据和业务的安全性,用户信息等敏感数据信息将由cpu模块发送到数据安全模块进行安全的存储和保护,即使设备被破坏也不会丢失,以保证了安全性;3)密钥管理子模块用于对称密钥和非对称密钥操作,其操作包括密钥生成、密钥删除、密钥导入、密钥导出、密钥备份以及密钥恢复。密钥的使用和存储的安全性是至关重要的,密钥管理功能由cpu模块和数据安全模块两部分共同完成,cpu模块负责发送密钥管理指令,数据安全模块负责密钥的安全存储和使用,确保在密钥在整个生命周期内都是安全的,任何人都无法窃取或者破坏密钥数据;4)后台服务程序模块用于监听网络端口、缓存网络数据包、解析封装用户协议、转发配置信息等工作,为上层的系统参数配置子模块、用户管理子模块、密钥管理子模块提供支持。当数据从底层硬件模块发往上层软件模块时,数据经过后台服务程序模块后,会去掉所有的协议封装,包括网络协议和用户自定义协议,只保留有效数据;当数据从上层的3个模块发往底层硬件时,数据经过后台服务程序模块后,会添加相应的协议封装,包括网络协议和用户自定义协议,封装后的数据会转发到对应的底层硬件模块进行处理。

40.5)数据通信用于软件和硬件之间的数据通信,其通信线路有5条:a.cpu模块至中转fpga模块至系统监测模块;b.cpu模块至中转fpga模块至接口fpga模块;c.cpu模块至中转fpga模块至接口fpga模块至千兆/万兆网口;d.cpu模块至中转fpga模块至接口fpga模块至数据安全模块;e.cpu模块至中转fpga模块至接口fpga模块至算法fpga模块;其中,a线路是由cpu模块获取系统监测模块状态的数据通路;b线路是由cpu模块进行配置接口fpga参数的数据通路;c线路是由cpu模块获取不需要算法运算数据包的数据报文通路;d线路是由cpu模块传递用户管理和密钥管理指令到数据安全模块的数据通路;e线路是由cpu模块调用算法fpga模块所提供的算法的数据通路;需要说明的是,所有通信线路的数据通信都需要遵循内部定义的通信协议,每个数据包的前16字节为通信协议头,数据包通过源id和目的id来完成寻址和路由,其中,通信协议头的格式如表2所示:

表2本发明的实施例通过上层软件模块向底层硬件模块发送控制指令;接收所述底层硬件模块根据所述控制指令对所述底层硬件模块传输的数据进行处理,得到的处理结果;所述底层硬件包括:中央处理器cpu、与所述cpu通信连接的现场可编程门阵列fpga接口模块以及所述fpga接口模块通信连接的算法fpga模块;所述fpga接口模块根据上层软件模块的控制指令对其接收到的数据报文发送至所述算法fpga模块进行安全运算处理或者发送至所述cpu处理;释放了中央处理器cpu的运算能力,缩减了软件开发的难度;提高了安全性和快速响应能力;增大了系统的算法处理性能;保证了服务器密码机的安全性。

41.如图7所示,本发明的实施例还提供一种服务器密码机的数据处理装置70,应用于服务器密码机,所述装置包括:收发模块71,用于接收上层软件模块的控制指令;处理模块72,用于根据所述控制指令对底层硬件模块传输的数据进行处理,得到处理结果;所述底层硬件包括:中央处理器cpu、与所述cpu通信连接的现场可编程门阵列fpga接口模块以及所述fpga接口模块通信连接的算法fpga模块;所述fpga接口模块根据上层软件模块的控制指令对其接收到的数据报文发送至所述算法fpga模块进行安全运算处理或者发送至所述cpu处理;所述收发模块在所述底层硬件模块和上层软件模块之间传输所述处理结果。

42.可选的,所述fpga接口模块根据上层软件模块的控制指令对其接收到的数据报文发送至所述算法fpga模块进行安全运算处理或者发送至所述cpu处理,包括:所述fpga接口模块根据上层软件模块的控制指令对其接收到的数据报文进行解析,得到解析结果;若所述解析结果表示所述数据报文是需要进行安全处理的业务数据,将所述数据报文发送至所述算法fpga模块进行安全运算处理,并接收所述算法fpga模块返回的运算结果;若所述解析结果表示所述数据报文是不需要进行安全处理的控制数据,将所述控制数据发送至所述cpu处理。

43.可选的,所述接口fpga模块通过中转fpga模块与所述cpu通信连接;所述接口fpga模块将所述控制数据通过所述中转fpga模块发送至所述cpu处理和/或接收所述cpu发送的配置信息;所述配置信息由上层软件模块中的系统参数配置模块产生并配置给所述cpu。

44.可选的,所述接口fpga模块与数据安全模块通信连接;所述接口fpga模块接收所述cpu发送的密钥管理指令,将所述密钥管理指令发送

给所述数据安全模块,由所述数据安全模块根据所述密钥管理指令进行以下至少一项操作:对称密钥或者非对称密钥的生成、删除、导入、导出、备份、恢复。

45.可选的,对所述数据进行解析,得到解析结果,包括:对所述数据进行解析,获得数据报文的字段信息;所述字段信息包括以下至少一项:前导码字段、mac字段、ip地址、报文类型头、净荷以及校验字段,所述mac字段包括源mac以及目的mac,所述ip地址包括源ip以及目的ip。

46.可选的,若所述解析结果表示所述数据报文是需要进行安全处理的业务数据,将所述数据报文发送至所述算法fpga模块进行安全运算处理,包括:若所述解析结果表示所述数据报文是需要进行安全处理的业务数据,且所述数据报文目的地址是本设备的地址,则将数据报文送入算法fpga模块进行处理。

47.可选的,接收所述算法fpga模块返回的运算结果,包括:接收所述算法fpga模块对所述数据报文采用预设安全算法进行加密和/或解密的运算结果。

48.需要说明的是,该装置是与上述方法对应的装置,上述方法实施例中的所有实现方式均适用于该装置的实施例中,也能达到相同的技术效果。本发明的实施例还提供一种服务器密码机,包括如上所述的数据处理装置。

49.本发明的实施例还提供一种服务器密码机,包括:上层软件模块以及底层硬件模块;所述上层软件模块向所述底层硬件模块发送控制指令;所述上层软件模块接收所述底层硬件模块根据所述控制指令对所述底层硬件模块传输的数据进行处理的处理结果;所述底层硬件模块包括:中央处理器cpu、接口现场可编程门阵列fpga模块以及算法fpga模块;所述cpu与所述接口fpga模块通信连接;所述接口fpga模块与所述算法fpga模块通信连接;所述fpga接口模块根据上层软件模块的控制指令对其接收到的数据报文发送至所述算法fpga模块进行安全运算处理或者发送至所述cpu处理。

50.可选的,所述fpga接口模块根据上层软件模块的控制指令对其接收到的数据报文发送至所述算法fpga模块进行安全运算处理或者发送至所述cpu处理,包括:所述fpga接口模块根据上层软件模块的控制指令对其接收到的数据报文进行解析,得到解析结果;若所述解析结果表示所述数据报文是需要进行安全处理的业务数据,将所述数据报文发送至所述算法fpga模块进行安全运算处理,并接收所述算法fpga模块返回的运算结果;若所述解析结果表示所述数据报文是不需要进行安全处理的控制数据,将所述控制数据发送至所述cpu处理。

51.可选的,所述接口fpga模块通过中转fpga模块与所述cpu通信连接;所述接口fpga模块将所述控制数据通过所述中转fpga模块发送至所述cpu处理和/或接收所述cpu发送的配置信息;所述配置信息由上层软件模块中的系统参数配置模块产生并配置给所述cpu。

52.可选的,所述接口fpga模块与数据安全模块通信连接;

所述接口fpga模块接收所述cpu发送的密钥管理指令,将所述密钥管理指令发送给所述数据安全模块,由所述数据安全模块根据所述密钥管理指令进行以下至少一项操作:对称密钥或者非对称密钥的生成、删除、导入、导出、备份、恢复。

53.可选的,对所述数据进行解析,得到解析结果,包括:对所述数据进行解析,获得数据报文的字段信息;所述字段信息包括以下至少一项:前导码字段、mac字段、ip地址、报文类型头、净荷以及校验字段,所述mac字段包括源mac以及目的mac,所述ip地址包括源ip以及目的ip。

54.可选的,若所述解析结果表示所述数据报文是需要进行安全处理的业务数据,将所述数据报文发送至所述算法fpga模块进行安全运算处理,包括:若所述解析结果表示所述数据报文是需要进行安全处理的业务数据,且所述数据报文目的地址是本设备的地址,则将数据报文送入算法fpga模块进行处理。

55.可选的,接收所述算法fpga模块返回的运算结果,包括:接收所述算法fpga模块对所述数据报文采用预设安全算法进行加密和/或解密的运算结果。

56.需要说明的是,该服务器密码机是与方法对应的服务器密码机,上述方法实施例中的所有实现方式均适用于该服务器密码机的实施例中,也能达到相同的技术效果。

57.本发明的实施例还提供一种计算机可读存储介质,存储指令,当所述指令在计算机上运行时,使得计算机执行如上所述的方法。上述各方法实施例中的所有实现方式均适用于该实施例中,也能达到相同的技术效果。

58.本领域普通技术人员可以意识到,结合本文中所公开的实施例描述的各示例的单元及算法步骤,能够以电子硬件、或者计算机软件和电子硬件的结合来实现。这些功能究竟以硬件还是软件方式来执行,取决于技术方案的特定应用和设计约束条件。专业技术人员可以对每个特定的应用来使用不同方法来实现所描述的功能,但是这种实现不应认为超出本发明的范围。

59.所属领域的技术人员可以清楚地了解到,为描述的方便和简洁,上述描述的系统、装置和单元的具体工作过程,可以参考前述方法实施例中的对应过程,在此不再赘述。

60.在本发明所提供的实施例中,应该理解到,所揭露的装置和方法,可以通过其它的方式实现。例如,以上所描述的装置实施例仅仅是示意性的,例如,所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,装置或单元的间接耦合或通信连接,可以是电性,机械或其它的形式。

61.所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

62.另外,在本发明各个实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。

63.所述功能如果以软件功能单元的形式实现并作为独立的产品销售或使用时,可以

存储在一个计算机可读取存储介质中。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行本发明各个实施例所述方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、rom、ram、磁碟或者光盘等各种可以存储程序代码的介质。

64.此外,需要指出的是,在本发明的装置和方法中,显然,各部件或各步骤是可以分解和/或重新组合的。这些分解和/或重新组合应视为本发明的等效方案。并且,执行上述系列处理的步骤可以自然地按照说明的顺序按时间顺序执行,但是并不需要一定按照时间顺序执行,某些步骤可以并行或彼此独立地执行。对本领域的普通技术人员而言,能够理解本发明的方法和装置的全部或者任何步骤或者部件,可以在任何计算装置(包括处理器、存储介质等)或者计算装置的网络中,以硬件、固件、软件或者它们的组合加以实现,这是本领域普通技术人员在阅读了本发明的说明的情况下运用他们的基本编程技能就能实现的。

65.因此,本发明的目的还可以通过在任何计算装置上运行一个程序或者一组程序来实现。所述计算装置可以是公知的通用装置。因此,本发明的目的也可 以仅仅通过提供包含实现所述方法或者装置的程序代码的程序产品来实现。也就是说,这样的程序产品也构成本发明,并且存储有这样的程序产品的存储介质也构成本发明。显然,所述存储介质可以是任何公知的存储介质或者将来所开发出来的任何存储介质。还需要指出的是,在本发明的装置和方法中,显然,各部件或各步骤是可以分解和/或重新组合的。这些分解和/或重新组合应视为本发明的等效方案。并且,执行上述系列处理的步骤可以自然地按照说明的顺序按时间顺序执行,但是并不需要一定按照时间顺序执行。某些步骤可以并行或彼此独立地执行。

66.以上所述是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明所述原理的前提下,还可以作出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1