动态模块与决策回馈均衡器的制作方法

1.本发明涉及一种动态模块与决策回馈均衡器,且特别是涉及一种可缓解推测式第一阶抽头(first-tap,简称为tap1)的时间边限的动态模块与决策回馈均衡器。

背景技术:

2.请参见图1,其是传送器与接收器之间的传输路径的示意图。传送器11传送至接收器13的数据在传输路径12中产生失真。因此,接收器13需要将失真的数据加以还原。使数据失真的原因不尽相同,其中之一为,因先前符码所引起的符码间干扰(inter-symbol interference,简称为isi)。

3.为减少isi,目前采用连续时间线性均衡器(continuous-time linear equalizer,简称为ctle)131与决策回馈均衡器(decision feedback equalizer,简称为dfe)133并将其应用于接收器13。简言之,ctle可调整频域的增益,而dfe 13可不放大噪声的情况下,处理isi所衍生的信号。因此,可搭配ctle 131与dfe 133移除isi并增强信噪比(signal-to-noise ratio,简称为snr)。接着,dfe输出d

out

将被传送至串列器/解串列器(serializer/deserializer,简称为serdes)135。

4.请参见图2,其是dfe结构的示意图。dfe 133包含加法器133a、感测放大器133b与rs锁存器133c。加法器133a接收输入数据d

in

与推测式第一阶抽头(tap1)后,将输入数据d

in

与推测式第一阶抽头(tap1)的加总结果传送至感测放大器133b。时钟信号clk触发感测放大器133b与rs锁存器133。

5.感测放大器133b将放大信号输出至rs锁存器133c,且rs锁存器133c产生dfe输出d

out

。由于dfe 133与多个步骤相关,且dfe 133须即时且递回地调整其操作,使dfe 133的设计复杂化。在高频(例如,高于10ghz)的应用中,抽头的速度相当关键,使dfe 133的设计面临挑战。

技术实现要素:

6.本公开涉及一种动态模块与决策回馈均衡器。通过有效地将多工器与动态锁存器整合为动态模块的方式,可以减少传递延迟并缓解推测式第一阶抽头(tap1)的操作边限。

7.根据本发明的第一方面,提出一种动态模块。动态模块包含第一骨牌电路与第二骨牌电路。第一骨牌电路产生第一多工输出。第一骨牌电路包含:第一多工器、至少一第一相位设定电路与第一决定选择级电路。第一多工器接收第一单轨输出、第二单轨输出、第三单轨输出,以及第四单轨输出其中的二者。至少一第一相位设定电路接收第一时钟信号。第一决定选择级电路电连接于第一多工器与至少一第一相位设定电路。第一决定选择级电路,其接收第一先前决定位元与第二先前决定位元。其中,第一先前决定位元与第二先前决定位元彼此互补。第二骨牌电路,电连接于所述第一骨牌电路并产生第二多工输出。第二骨牌电路包含:第二多工器、至少一第二相位设定电路与第二决定选择级电路。第二多工器接收第一单轨输出、第二单轨输出、第三单轨输出与第四单轨输出其中的另外二者。至少一第

二相位设定电路接收第二时钟信号。其中,第一时钟信号与第二时钟信号为互补。第二决定选择级电路电连接于第二多工器与至少一第二相位设定电路。第二决定选择级电路接收第一先前决定位元与第二先前决定位元。在评鉴期间,第一多工输出与第二多工输出选择性以第一单轨输出、第二单轨输出、第三单轨输出与第四单轨输出更新。在预充电期间,第一多工输出与所述第二多工输出维持不变。

8.根据本发明的第二方面,提出一种决策回馈均衡器。决策回馈均衡器包含第一推测路径与第二推测路径。第一推测路径于评鉴期间提供第一先前决定位元与第二先前决定位元。其中,第一先前决定位元与第二先前决定位元彼此互补。第二推测路径电连接于第一推测路径。第二推测路径包含:第一感测放大器、第二感测放大器、与动态模块。第一感测放大器输出包含第一单轨输出与第二单轨输出的第一轨对轨输出对。第二感测放大器输出包含第三单轨输出与第四单轨输出的第二轨对轨输出对。动态模块电连接于第一感测放大器与第二感测放大器。动态模块包含彼此电连接的第一骨牌电路与第二骨牌电路。第一骨牌电路产生第一多工输出,第二骨牌电路产生第二多工输出。第一骨牌电路包含:第一多工器、至少一第一相位设定电路以及第一决定选择级电路。第一多工器接收第一单轨输出、第二单轨输出、第三单轨输出,以及第四单轨输出其中的二者。至少一第一相位设定电路接收第一时钟信号。第一决定选择级电路电连接于第一多工与至少一第一相位设定电路。第一决定选择级电路接收第一先前决定位元与第二先前决定位元。第二骨牌电路包含:第二多工器、至少一第二相位设定电路与第二决定选择级电路。第二多工器接收第一单轨输出、第二单轨输出、第三单轨输出与所述四单轨输出中的另外二者。至少一第二相位设定电路接收第二时钟信号。其中,第一时钟信号与第二时钟信号彼此互补。第二决定选择级电路电连接于第二多工器与至少一第二相位设定电路。第二决定选择级电路接收第一先前决定位元与第二先前决定位元。在评鉴期间,第一多工输出与第二多工输出选择性以第一轨对轨输出对与第二轨对轨输出对的其中一者更新。在预充电期间,第一多工输出与第二多工输出维持不变。

9.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合所附图式详细说明如下。

附图说明

10.图1,其是传送路径的示意图。

11.图2,其是dfe结构的示意图。

12.图3,其是推测式dfe的示意图。

13.图4,其是偶数推测路径与奇数推测路径之间彼此交错的操作期间的波形图。

14.图5a,其是一种推测式dfe的举例的示意图。

15.图5b,其是另一种推测式dfe的举例的示意图。

16.图6,其是比较图5a、图5b的推测式dfe中的延迟成因的示意图。

17.图7,其是根据本公开构想的动态模块的通用方框图。

18.图8a,其是根据本公开第一实施例的动态模块的方框图。

19.图8b,其是根据本公开第一实施例的动态模块的电路设计的示意图。

20.图9,其是说明根据本公开第一实施例的动态模块,如何在预充电期间t

pre

运行的

示意图。

21.图10a,其是在正向先前决定位元s

po

为低逻辑电平(s

po

=0),且反向先前决定位元sb

po

为高逻辑电平(sb

po

=1)时,根据本公开的第一实施例的动态模块于评鉴期间t

eva

运行的示意图。

22.图10b,其是在正向先前决定位元s

po

为高逻辑电平(s

po

=1),且反向先前决定位元sb

po

为低逻辑电平(sb

po

=0)时,根据本公开的第一实施例的动态模块于评鉴期间t

eva

运行的示意图。

23.图11,其是列示根据本公开第一实施例的动态模块,在预充电期间t

pre

与评鉴期间t

eva

时的信号状态的摘要表。

24.图12,其是以一数据流为例,说明如何根据本公开构想的第一实施例的推测式dfe对其进行处理的波形图。

25.图13a,其是根据本公开第二实施例的动态模块的方框图。

26.图13b,其是根据本公开第二实施例的动态模块的电路设计的示意图。

27.图14,其是根据本公开构想的第二实施例的动态模块,在于预充电期间t

pre

运行的示意图。

28.图15a,其是在正向先前决定位元s

po

为低逻辑电平(s

po

=0),且反向先前决定位元sb

po

为高逻辑电平(sb

po

=1)时,根据本公开构想的第二实施例的动态模块于评鉴期间t

eva

运行的示意图。

29.图15b,其是在正向先前决定位元s

po

为高逻辑电平(s

po

=1),且反向先前决定位元sb

po

为低逻辑电平(sb

po

=0)时,根据本公开构想的第二实施例的动态模块于评鉴期间t

eva

运行的示意图。

30.图16,其是根据本公开构想的第二实施例的上方骨牌电路,于评鉴期间t

eva

运行的流程图。

31.图17,其是列示在预充电期间t

pre

与评鉴期间t

eva

,根据本公开第二实施例的动态模块的信号状态的摘要表。

32.图18,其是根据本公开构想的第二实施例的推测式dfe,对一数据流的例子进行处理的波形图。

33.图19a,其是根据本公开构想的第三实施例的动态模块的方框图。

34.图19b,其是根据本公开的第三实施例的动态模块的电路设计的示意图。

35.图20,其是根据本公开构想的第三实施例的动态模块,在预充电期间t

pre

如何运行的示意图。

36.图21a,其是在正向先前决定位元s

po

为低逻辑电平(s

po

=0),且反向先前决定位元sb

po

为高逻辑电平(sb

po

=1)时,根据本公开的第三实施例的动态模块于评鉴期间t

eva

运行的示意图。

37.图21b,其是在正向先前决定位元s

po

为高逻辑电平(s

po

=1),且反向先前决定位元sb

po

为低逻辑电平(sb

po

=0)时,根据本公开的第三实施例的动态模块于评鉴期间t

eva

运行的示意图。

38.图22,其是根据本公开构想的第三实施例的上方骨牌电路,于评鉴期间t

eva

运行的流程图。

39.图23,其是在预充电期间t

pre

与评鉴期间t

eva

,根据本公开构想的第三实施例的动态模块的信号状态的摘要表。

40.图24,其是具有四等分速率结构的推测式dfe的示意图。

41.其中,附图标记说明如下:

42.11:传送器

43.12:传输路径

44.13:接收器

45.131:连续时间线性均衡器

46.133:决策回馈均衡器

47.135:串列器/解串列器

48.133a,211a,211b,231a,231b,311a,311b:加法器

49.d

in

,in(a),in(b),in(c),in(d),in(e),in(f):输入数据

50.tap1:第一阶抽头

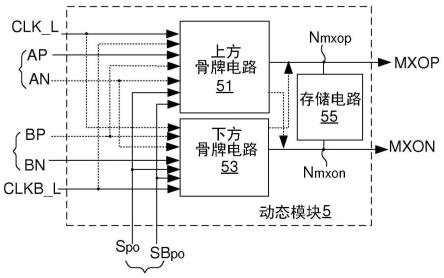

51.133b,213a,213b,233a,233b,313a,313b,333a,333b:感测放大器

52.clk:时钟信号

53.133c:rs锁存器

54.d

out

:dfe输出

55.15:dfe

56.151,21:偶数推测路径

57.153,23:奇数推测路径

58.d

out_evn

:偶数路径决定

59.d

out_odd

:奇数路径决定

60.clk_l(even):偶数路径的正向锁存时钟信号

61.clk_l(odd):奇数路径的正向锁存时钟信号

62.clkb_l(even):偶数路径的反向锁存时钟信号

63.clkb_l(odd):奇数路径的反向锁存时钟信号

64.t

eva

:评鉴期间

65.t

pre

:预充电期间

66.t(n),t(n+1),t(n+2),t(n+3),t1,t2,t3,t4,t5:期间

67.apevn:第一偶数路径的正极单轨输出

68.anevn:第一偶数路径的负极单轨输出

69.bpevn:第二偶数路径的正极单轨输出

70.bnevn:第二偶数路径的负极单轨输出

71.215a,215b,235a,235b:锁存器

72.mux

evn_in1

,mux

evn_in2

,mux

odd_in1

,mux

odd_in2

:多工输入

73.217,237,611,631,711,731,811,831:多工器

74.mux

evn_out

,mux

odd_out

:多工输出

75.219,239:触发器

76.2,3,90:推测式dfe

77.apodd,anodd,bpodd,bnodd:单轨输出

78.31:偶数推测路径

79.315:偶数动态模块

80.315a,335a,51,61,71,81:上方骨牌电路

81.315b,335b,53,63,73,83:下方骨牌电路

82.315c,335c,55,65,75,85:存储电路

83.mxopevn,mx(c):偶数路径的正向多工输出

84.mxonevn,mxb(c):偶数路径的反向多工输出

85.317a,317b:反向器

86.sb

evn

,sb

odd

,sb

po

:反向先前决定位元

87.s

evn

,s

odd

,s

po

:正向先前决定位元

88.33:奇数推测路径

89.331a,331b:加法器

90.335:奇数动态模块

91.mxopodd,mx(b),mx(d):奇数路径的正向多工输出

92.mxonodd,mxb(b),mxb(d):奇数路径的反向多工输出

93.337a,337b,sinv1,sinv2,uinv1,uinv2,linv1,linv2:反向器

94.clkb_l:反向锁存时钟信号

95.ui:数据单位间隔

96.t1~t7:时点

97.t

clk2sa

:时钟传递延迟

98.t

susa

:设置时间

99.t

latch

,t

dyn

,t

mux

:传递延迟

100.c1,c2:虚线圈选处

101.δt

tap1

,δt

tap1’:操作边限

102.clk_l:正向锁存时钟信号

103.ap:第一正极单轨输出

104.an:第一负极单轨输出

105.bp:第二正极单轨输出

106.bn:第二负极单轨输出

107.clkb_l:反向锁存时钟信号

108.5,6,7,8:动态模块

109.n

mxop

:正向多工输出端点

110.n

mxon

:反向多工输出端点

111.mxop:正向多工输出

112.mxon:反向多工输出

113.613,633,713,733,813,833:动态锁存器

114.613a,633a,713c,733c,813c,833c:决定选择级电路

115.613b,633b,713a,713b,733a,733b,813a,813b,833a,833b:相位设定电路

116.n

m1

,n

m2

:中间端点

117.vcc:供应电压端点(供应电压)

118.gnd:接地端点(接地电压)

119.up,lp1,lp2,llatp1,llatp2,lp,unop1,unop2,upop1,upop2,upp,uinp,unp,lnop1,lnop2,lpop1,lpop2,lpp,linp,lnp,upop,unop,lpop,lnop:pmos晶体管

120.un,ulatn1,ultn2,un1,un2,ln,unon2,unon1,upon2,upon1,upn,uinn,unn,lnon2,lnon1,lpon2,lpon1,lpn,linn,lnn,upon,unon,lpon,lnon:nmos晶体管

121.clk_sys:系统时钟信号

122.sa(a),sa(b),sa(c),sa(d),sa(e),sa(f):取样数据

123.sa(a)+,sa(c)+,sa(e)+:第二偶数路径的轨对轨输出对

124.sa(b)+,sa(d)+:第二奇数路径的轨对轨输出对

125.sa(a)-,sa(c)-,sa(e)-:第一偶数路径的轨对轨输出对

126.sa(b)-,sa(d)-:第一奇数路径的轨对轨输出对

127.711b,731b,811b,831b:负极输出电路

128.711a,731a,811a,831a:正极输出电路

129.sa_p,sa_n,sb_p,sb_n:选择信号

130.n

ap

,n

an

,n

bp

,n

bn

:选择端点

131.s71,s71a,s71b,s73,s73a,s73b,s75,s75a,s75b,s77,s81,s81a,s81b,s83,s83a,s83b,s85,s85a,s85b,s87:步骤91,92,93,94:推测路径

132.d

out_p1

,d

out_p2

,d

out_p3

,d

out_p4

:路径决定

具体实施方式

133.在全部的抽头中,第一阶抽头(tap1)的时间限制最为严苛,即,一个数据单位间隔(unit interval,简称为ui)。为放宽第一阶抽头(tap1)的时间限制,可采用推测式(循环展开(loop-unrolling))方式设计dfe。采用推测式结构时,推测式dfe包含偶数推测路径与奇数推测路径,且推测式第一阶抽头(tap1)的时间限制可被延长至两倍的数据单位间隔(2*ui)。

134.请参见图3,其是推测式dfe的示意图。dfe 15包含偶数推测路径151与奇数推测路径153。偶数推测路径151接收输入数据d

in

并产生偶数路径决定d

out_evn

。其中,偶数路径决定d

out_evn

进一步馈入至奇数推测路径153,供奇数推测路径153参酌。奇数推测路径153接收输入数据d

in

并产生奇数路径决定d

out_odd

。其中,奇数路径决定d

out_odd

进一步馈入至偶数推测路径151,供偶数推测路径151参酌。dfe输出d

out

再交替采用偶数路径决定d

out_evn

与奇数路径决定d

out_odd

。

135.请参见图4,其是偶数推测路径与奇数推测路径之间彼此交错的操作期间的波形图。横轴为时间,纵轴为偶数路径的正向锁存时钟信号clk_l(even)与奇数路径的正向锁存时钟信号clk_l(odd)的波形。偶数路径的正向锁存时钟信号clk_l(even)提供予偶数推测路径151,且奇数路径的正向锁存时钟信号clk_l(odd)提供予奇数推测路径153。

136.当偶数路径的正向锁存时钟信号clk_l(even)为高逻辑电平(clk_l(even)=1)时,偶数推测路径151运行于评鉴阶段。偶数推测路径151运行在评鉴阶段的期间定义为,与

偶数推测路径151对应的评鉴期间t

eva

。当偶数路径的正向锁存时钟信号clk_l(even)为低逻辑电平(clk_l(even)=0)时,偶数推测路径151运行于预充电阶段。偶数推测路径151运行在预充电阶段的期间定义为,与偶数推测路径151对应的预充电期间t

pre

。

137.当奇数路径的正向锁存时钟信号clk_l(odd)为高逻辑电平(clk_l(odd)=1)时,奇数推测路径运行于评鉴阶段。奇数推测路径153运行在评鉴阶段的期间定义为,与奇数推测路径153对应的评鉴期间t

eva

。当奇数路径的正向锁存时钟信号clk_l(odd)为低逻辑电平(clk_l(odd)=0)时,奇数推测路径153运行于预充电阶段。奇数推测路径153运行在预充电阶段的期间定义为,与奇数推测路径153对应的预充电期间t

pre

。

138.偶数路径的正向锁存时钟信号clk_l(even)与奇数路径的正向clk_l(odd)的相位彼此互补,且偶数推测路径151与奇数推测路径153的操作阶段彼此交错切换。在t(n)、t(n+2)期间,偶数推测路径151运行于评鉴阶段,且奇数推测路径153运行于预充电阶段。在t(n+1)、t(n+3)期间,偶数推测路径151运行于预充电阶段,且奇数推测路径153运行于评鉴阶段。据此,当偶数推测路径151处于评鉴期间t

eva

时,奇数推测路径153处于预充电期间t

pre

,反之亦然。

139.图5a、图5b为两个具有循环展开结构的推测推测式dfe的例子。图5a、图5b说明偶数推测路径151与奇数推测路径153具有类似且对称的设计。

140.请参见图5a,其是一种推测式dfe的举例的示意图。推测式dfe 2包含偶数推测路径21与奇数推测路径23。偶数推测路径21包含加法器211a、211b、感测放大器213a、213b、锁存器215a、215b、多工器217与触发器219。奇数推测路径23包含加法器231a、231b、感测放大器233a、233b、锁存器235a、235b、多工器237与触发器239。

141.感测放大器213a、213b、233a、233b各自基于对应的锁存时钟信号clk_l运行,且各个感测放大器213a、213b、233a、233b具有差动输入与双轨输出。在偶数推测路径21中的感测放大器213a、213b的运行,以及在奇数推测路径23中的感测放大器233a、233b的运行彼此对称。例如,当偶数路径的正向锁存时钟信号clk_l(even)为高逻辑电平时,位于偶数推测路径21的感测放大器213a、213继续执行取样与保持操作,且位于奇数推测路径23的感测放大器233a、233b停止其操作。反之亦然。当感测放大器213a、213b、233a、233b继续进行取样与保持操作时,属于同一个感测放大器213a、213b、233a、233b的两个输出中的一者(依据输入差动电压的极性)被设为放大器供应电压电平;另一者则维持在放大器接地电压电平(低逻辑电平)。

142.偶数推测路径21与奇数推测路径23交替接收输入数据d

in

并因应产生与其对应的偶数路径决定d

out_evn

、奇数路径决定d

out_odd

。奇数推测路径23自偶数推测路径21接收偶数路径决定d

out_evn

,且偶数推测路径21自奇数推测路径23接收奇数路径决定d

out_odd

。

143.接着说明dfe 2中的偶数推测路径21的运行。加法器211a、211b同时接收输入数据d

in

与推测式第一阶抽头(tap1)。加法器211a从输入数据d

in

扣除推测式第一阶抽头(tap1)后,将加法器输出(d

in-tap1)传送至感测放大器213a。加法器211b将推测式第一阶抽头(tap1)与输入数据d

in

相加(d

in

+tap1)后,将加法器输出(d

in

+tap1)传送至感测放大器213b。

144.感测放大器213a根据加法器211a的加法器输出(d

in-tap1),产生第一偶数路径的正极单轨输出apevn与第一偶数路径的负极单轨输出anevn。感测放大器213b根据加法器211b的加法器输出(d

in

+tap1),产生第二偶数路径的正极单轨输出bpevn与第二偶数路径的

负极单轨输出bnevn。

145.锁存器215a自感测放大器213a接收第一偶数路径的正极单轨输出apevn与第一偶数路径的负极单轨输出anevn,并据以产生偶数路径多工输入mux

evn_in1

。锁存器215b自感测放大器213b接收第二偶数路径的正极单轨输出bpevn与第二偶数路径的负极单轨输出bnevn,并据以产生偶数路径多工输入mux

evn_in2

。多工器217根据奇数路径的决定输出d

out_odd

,选择多工输入mux

evn_in1

、mux

evn_in2

的其中一者作为多工输出mux

evn_out

。将多工输出mux

evn_out

进一步传送至触发器219。触发器219提供偶数路径的决定输出d

out_evn

至奇数推测路径23。

146.因奇数推测路径23的运行与偶数推测路径21的运行相似,其细节不予详述。另请留意,本文毋须限定推测式第一阶抽头(tap1)的来源与权重,且推测式dfe可能具有多个抽头。

147.请参见图5b,其是另一种推测式dfe的举例的示意图。推测式dfe 3包含偶数推测路径31与奇数推测路径33。偶数推测路径31包含加法器311a、311b、感测放大器313a、313b、偶数动态模块315与反向器317a、317b。奇数推测路径33包含加法器331a、331b、感测放大器333a、333b、奇数动态模块335与反向器337a、337b。

148.偶数动态模块315与奇数动态模块335的设计相似。偶数动态模块315包含上方骨牌电路315a、下方骨牌电路315b与存储电路315c。奇数动态模块335包含上方骨牌电路335a、下方骨牌电路335b与存储电路335c。表1汇整推测式dfe 3的元件的运行方式。

149.表1

150.[0151][0152]

由表1可以得知,偶数推测路径31与奇数推测路径33的运行与元件彼此类似且对称,故偶数动态模块315与奇数动态模块335可采用相同的实现方式。偶数动态模块315与奇数动态模块335的差异处为其输入信号的来源,且其互相使用彼此的多工输出。

[0153]

在图5b中,偶数动态模块315将锁存器215a、215b与多工器217的功能整合在一起,且奇数动态模块335将锁存器235a、235b与多工器237的功能整合在一起。偶数动态模块315与奇数动态模块335以动态逻辑的方式设计,借以高效率地进行锁存与多工操作。

[0154]

请参见图6,其是比较图5a、图5b的推测式dfe中的延迟成因的示意图。图6的横轴为时间。时点t1至时点t7的期间相当于推测式第一阶抽头(tap1)的时间限制。即,两个数据单位间隔(2*ui)。图6的上方绘示造成推测式dfe 2延迟的成因,图6的下方绘示造成推测式dfe 3延迟的成因。

[0155]

推测式dfe 2的延迟成因包含:感测放大器213a、213b的时钟传递延迟(介于时点t1至时点t2)、感测放大器213a、213b的设置时间t

susa

(介于时点t2至时点t3),多工器锁存器215a、215ba的传递延迟t

latch

(介于时点t3至时点t4),以及,多工器217的传递延迟t

mux

(介于时点t4至时点t6)。两倍的数据单位间隔(2*ui)与推测式dfe 2的延迟成因的加总结果的差值(即,时点t6至时点t7),即为采用推测式dfe 2时的第一阶抽头(tap1)的操作边限δt

tap1

。

[0156]

推测式dfe 3的延迟成因包含:感测放大器313a、313b的时钟传递延迟t

clk2sa

(介于时点t1至时点t2)、感测放大器313a、313b的设置时间t

susa

(介于时点t2至时点t3),以及奇数/偶数动态模块315、335的传递延迟t

dyn

(介于时点t3至时点t5)。两倍的数据单位间隔(2*ui)与推测式dfe 3的延迟成因的加总结果的差值(即,时点t5至时点t7期间),即为选用推测式dfe 3时的第一阶抽头(tap1)的操作边限δt

tap1’。

[0157]

虚线圈选处c1为图5a中,沿着奇数/偶数推测路径的传递延迟。虚线圈选处c2为,图5b中沿奇数/偶数推测路径的传递延迟。比较虚线圈选处c1、c2可以发现,虚线圈选处c1所圈选的期间,较虚线圈选处c2所圈选的期间长。且,图5b的推测式第一阶抽头(tap1)的操作边限δt

tap1’,较图5a中的推测式第一阶抽头(tap1)的操作边限δt

tap1

更长。因此,图5b的推测式dfe 3可提供具有较佳容许度的推测式第一阶抽头(tap1)。

[0158]

请参见图7,其是根据本公开构想的动态模块的通用方框图。动态模块5包含上方骨牌电路51、下方骨牌电路53与存储电路55。动态模块5可为图5b中的偶数动态模块315或

奇数动态模块335的任一者。表2列出图5b、图7中的信号的对应关系。

[0159]

表2

[0160][0161][0162]

上方骨牌电路51与下方骨牌电路53接收三种输入信号,包含:正向/反向锁存时钟信号(clk_l,clkb_l)、第一轨对轨输出对(ap,an)、第二轨对轨输出对(bp,bn),以及先前决定位元(s

po

,sb

po

)。先前决定位元(s

po

,sb

po

)是接收自其他的动态模块,而正向锁存时钟信号clk_l、反向锁存时钟信号clkb_l是接收自系统中的其他电路(例如,pll)。

[0163]

存储电路55电连接于正向多工输出端点n

mxop

与反向多工输出端点n

mxon

间,用以跨接上方骨牌电路51与下方骨牌电路53。正向多工输出mxop在正向多工输出端点n

mxop

产生,反向多工输出mxon在反向多工输出端点n

mxon

产生。

[0164]

本文使用一些符号表示信号的状态。在本文中,以符号"x"表示信号的变动不影响电路的运行;以符号"z"表示信号为浮接(高阻抗)。

[0165]

根据本公开的实施例,动态模块5运行于双重阶段。在评鉴期间t

eva

,动态模块5依据正向先前决定位元s

po

、反向先前决定位元sb

po

,以第一轨对轨输出对(ap,an)与第二轨对轨输出对(bp,bn)的其中一者更新正向多工输出mxop、反向多工输出mxon。在预充电期间t

pre

,动态模块5维持正向多工输出mxop、反向多工输出mxon不变而不更新。

[0166]

本公开以三个实施例说明动态模块5的作法。图8a、图8b、图9、图10a、图10b、图11、图12为第一实施例。图13a、图13b、图14、图15a、图15b、图16、图17、图18为第二实施例。图19a、图19b、图20、图21a、图21b、图22、图23为第三实施例。这些实施例将以方框图、电路设计、信号状态的比较表呈现,并说明基于这些实施例的动态模块的运行。另请留意,本公开构想的实现方式并不限于下述的实施例。

[0167]

第一实施例

[0168]

图8a、图8b分别为,根据本公开第一实施例的动态模块6的方框图与电路设计。图9说明动态模块6在预充电期间t

pre

的运行。图10a、图10b说明动态模块6在评鉴期间t

eva

的运行。图11列示动态模块6在预充电期间t

pre

与评鉴期间t

eva

的信号状态的摘要表。图12说明如何将动态模块6应用于推测式dfe 3。

[0169]

请参见图8a,其是根据本公开第一实施例的动态模块的方框图。动态模块6包含上方骨牌电路61、下方骨牌电路63与存储电路65。存储电路65经由正向多工器端点n

mxop

而电连接于上方骨牌电路61,以及经由反向多工器端点n

mxon

而电连接于下方骨牌电路63。

[0170]

上方骨牌电路61还包含多工器611与动态锁存器613,且下方骨牌电路63还包含多工器631与动态锁存器633。动态锁存器613包含决定选择级电路613a与相位设定电路613b,且动态锁存器633包含决定选择级电路633a与相位设定电路633b。

[0171]

请参见图8b,其是根据本公开第一实施例的动态模块的电路设计的示意图。在上方骨牌电路61中,多工器611包含nmos晶体管un1、un2,决定选择级电路613a包含nmos晶体管ulatn1、ulatn2,而相位设定电路613b包含pmos晶体管up与nmos晶体管un。在下方骨牌电路63中,多工器631包含pmos晶体管lp1、lp2,决定选择级电路633a包含pmos晶体管llatp1、llatp2,而相位设定电路633b包含pmos晶体管lp与nmos晶体管ln。存储电路65包含反向器sinv1、sinv2。

[0172]

接着,分别说明与上方骨牌电路61中的多工器611、决定选择级电路613a和相位设定电路613b相关的信号与连接关系。在多工器611中,nmos晶体管un1、un2的漏极电连接于决定选择级电路613a;nmos晶体管un1、un2的源极电连接于接地端点(gnd)。nmos晶体管un1的栅极接收第一正极单轨输出ap,且nmos晶体管un2的栅极接收第二正极单轨输出bp。

[0173]

在决定选择级电路613a中,nmos晶体管ulatn1、ulatn2的漏极电连接于中间端点n

m1

,且nmos晶体管ulatn1、ulatn2的源极分别电连接于多工器611中的nmos晶体管un1、un2的漏极。nmos晶体管ulatn1的栅极接收正向先前决定位元spo,nmos晶体管ulatn2的栅极接收反向先前决定位元sb

po

。

[0174]

在相位设定电路613b中,pmos晶体管up的源极电连接于供应电压端点(vcc),且nmos晶体管un的源极电连接于中间端点n

m1

。pmos晶体管up的栅极与nmos晶体管un的栅极彼此电连接,用以接收正向锁存时钟信号clk_l。pmos晶体管up与nmos晶体管un的漏极均电连接于正向多工输出端点n

mxop

。

[0175]

接着,分别说明与下方骨牌电路63中的多工器631、决定选择级电路633a与相位设

定电路633b相关的信号与连线关系。在多工器631中,pmos晶体管lp1、lp2的漏极电连接于决定选择级电路633a。pmos晶体管lp1、lp2的源极电连接于供应电压端点(vcc)。pmos晶体管lp1的栅极接收第一负极单轨输出an,pmos晶体管lp2的栅极接收第二负极单轨输出bn。

[0176]

在决定选择级电路633a中,pmos晶体管llatp1、llatp2的漏极均电连接于中间端点n

m2

,且pmos晶体管llatp1、llatp2的源极分别电连接于pmos晶体管lp1、lp2的漏极。pmos晶体管llatp1的栅极接收反向先前决定位元sb

po

,pmos晶体管llatp2的栅极接收正向先前决定位元s

po

。

[0177]

在相位设定电路633b中,nmos晶体管ln的源极电连接于接地端点(gnd),pmos晶体管lp的源极电连接于中间端点n

m2

。pmos晶体管lp与nmos晶体管ln的栅极彼此电连接,用以接收反向锁存时钟信号ckb_l。pmos晶体管lp与nmos晶体管ln的漏极均电连接于反向多工输出端点n

mxon

。

[0178]

在存储电路65中,反向器sinv1的输入端点与输出端点分别电连接于正向多工输出端点n

mxop

与反向多工输出端点n

mxon

。反向器sinv2的输入端点与输出端点分别电连接于反向多工输出端点n

mxon

与正向多工输出端点n

mxop

。

[0179]

请参见图9,其说明根据本公开第一实施例的动态模块,如何在预充电期间t

pre

运行的示意图。以下分别说明上方骨牌电路61与下方骨牌电路63的运行。

[0180]

接着说明在上方骨牌电路61中的元件,在预充电期间t

pre

的运行。在相位设定电路613b中,pmos晶体管up导通,且nmos晶体管un断开。因此,正向多工输出mxop等于供应电压vcc(mxop=1),且决定选择级电路613a与多工器61不影响正向多工输出端点n

mxop

。据此,正向多工输出mxop与上方骨牌电路61的输入(即,第一正极单轨输出ap与第二正极单轨输出ap)无关。此处以点状网底绘示被禁能的多工器611与决定选择级电路613a。

[0181]

接着说明下方骨牌电路63中的元件在预充电期间t

pre

的运行。在相位设定电路633b中,pmos晶体管lp断开,且nmos晶体管ln导通。因此,反向多工输出mxon等于接地电压gnd(mxon=0),且决定选择级电路633a与多工器631不影响反向多工输出端点n

mxon

。据此,反向多工输出mxon与下方骨牌电路63的输入(即,第一负极单轨输出an与第二负极单轨输出bn)无关。此处以点状网底绘示被禁能的多工器631与决定选择级电路633a。

[0182]

图10a、图10b说明动态模块6在评鉴期间t

eva

运行时,动态模块6的信号与元件状态。在动态模块6中,可将决定选择级电路613a、633a与多工器611、631内的pmos晶体管与nmos晶体管,依据其位置与连接方式区分成四个分支。这四个分支包含:左下方分支(nmos晶体管ulatn1、un1)、右下方分支(nmos晶体管ulatn2、un2)、左上方分支(pmos晶体管lp1、llatp1),以及,右上方分支(pmos晶体管lp2、llatp2)。

[0183]

请参见图10a,其是在正向先前决定位元s

po

为低逻辑电平(s

po

=0),且反向先前决定位元sb

po

为高逻辑电平(sb

po

=1)时,根据本公开的第一实施例的动态模块于评鉴期间t

eva

运行的示意图。请参见图10b,其是在正向先前决定位元s

po

为高逻辑电平(s

po

=1),且反向先前决定位元sb

po

为低逻辑电平(sb

po

=0)时,根据本公开的第一实施例的动态模块于评鉴期间t

eva

运行的示意图。

[0184]

随着先前决定位元(s

po

,sb

po

)的不同,图10a、图10b的正向多工输出mxop、反向多工输出mxon可能维持不变,或以第一轨对轨输出对(ap,an)与第二轨对轨输出对(bp,bn)的其中一者更新。

[0185]

接着说明上方骨牌电路61中的相位设定电路613b、决定选择级电路613a,以及多工器611如何在评鉴期间t

eva

运行。由于正向锁存时钟信号clk_l为高逻辑电平(clk_l=1),相位设定电路613b中的pmos晶体管up断开,且nmos晶体管un导通。正向多工输出mxop由决定选择级电路613a与多工器611决定。

[0186]

当正向先前决定位元s

po

为低逻辑电平(s

po

=0),且反向先前决定位元sb

po

为高逻辑电平(sb

po

=1)时(如图10a所示),决定选择级电路613a内的nmos晶体管ulatn1断开,且nmos晶体管ulatn2导通。连带的,因为决定选择级电路613中的nmos晶体管ulatn1断开的缘故,使多工器611中的nmos晶体管un1断开,且多工器611中的nmos晶体管un2随第二正极单轨输出bp的改变而导通或断开。在图10a中,以点状网底绘示位于左下方分支的nmos晶体管ulatn1、un1,代表其与正向多工输出mxop无关。

[0187]

在图10a中,因应第二正极单轨输出bp的变化,多工器611中的nmos晶体管un2可能导通或断开。若第二正极单轨输出bp为低逻辑电平(bp=0),则位于多工器611的nmos晶体管un2断开,且不更新正向多工输出mxop。若第二正极单轨输出bp为高逻辑电平(bp=1),则位于多工器611的nmos晶体管un2将导通,使正向多工输出mxop等于接地电压gnd(mxop=0)。简言之,在图10a中,正向多工输出mxop由右下方分支决定。

[0188]

当正向先前决定位元s

po

为高逻辑电平(s

po

=1),且反向先前决定位元sb

po

为低逻辑电平(sb

po

=0)时(如图10b所示),决定选择级电路613a内的nmos晶体管ulatn1导通,且nmos晶体管ulatn2断开。连带的,在多工器611中的nmos晶体管un1可能随着第一正极单轨输出ap的改变而导通或断开,且多工器611中的nmos晶体管un2因决定选择级电路613中的nmos晶体管ulatn2为断开而断开。在图10b中,以点状网底绘示位于右下方分支的nmos晶体管ulatn2、un2,代表其与正向多工输出mxop无关。

[0189]

在图10b中,因应第一正极单轨输出ap的变化,多工器611中的nmos晶体管un1可能导通或断开。若第一正极单轨输出ap为低逻辑电平(ap=0),则位于多工器611的nmos晶体管un1将断开,且不更新正向多工输出mxop。若第一正极单轨输出ap为高逻辑电平(ap=1),则位于多工器611的nmos晶体管un1将导通,且正向多工输出mxop等于接地电压gnd(mxop=0)。简言之,在图10b中,正向多工输出mxop由左下方分支所决定。

[0190]

当动态模块6处于评鉴期间t

eva

时,上方骨牌电路61中的相位设定电路613b、决定选择级电路613a与多工器611将依序动作。相位设定电路613b先判断正向多工输出mxop是否与决定选择级电路613a和多工器611相关。接着,决定选择级电路613a判断多工器611中的nmos晶体管un1、un2中的何者将影响正向多工输出mxop。

[0191]

下方骨牌电路63中的相位设定电路633b、决定选择级电路633a,以及多工器631在评鉴期间t

eva

的动作,均与上方骨牌电路61相似。若反向锁存时钟信号clkb_l处于低逻辑电平(clkb_l=0),相位设定电路633b中的pmos晶体管lp导通,且nmos晶体管ln断开。反向多工输出mxon由决定选择级电路633a与多工器631决定。

[0192]

当正向先前决定位元s

po

为低逻辑电平(s

po

=0)时,反向先前决定位元sb

po

为高逻辑电平(sb

po

=1)(如图10a所示)。此时,pmos晶体管llatp1断开,且pmos晶体管llatp2导通,使反向多工输出mxon由右上方分支决定。图10a以点状网底绘示位于左上方分支的pmos晶体管llatp1、lp1,代表其与反向多工输出mxon无关。

[0193]

或者,当正向先前决定位元s

po

为高逻辑电平(s

po

=1)时,反向先前决定位元sb

po

为

低逻辑电平(sb

po

=0)(如图10b所示)。此时,pmos晶体管llatp1导通,且pmos晶体管llatp2断开,使反向多工输出mxon由左上方分支决定。图10b以点状网底绘示位于右上方分支的pmos晶体管llatp2、lp2,代表其与反向多工输出mxon无关。

[0194]

当动态模块6处于评鉴期间t

eva

时,下方骨牌电路63中的相位设定电路633b、决定选择级电路633a与多工器631将依序动作。相位设定电路633b先判断反向多工输出mxon是否与决定选择级电路633a和多工器631相关。接着,决定选择级电路633a判断多工器631中的pmos晶体管lp1、lp2中的何者将影响反向多工输出mxon。

[0195]

以上说明动态模块6如何因应不同的输入信号而运行的细节。为便于说明,图11绘示动态模块6的不同的输入信号的组合,以及与其对应的正向多工输出mxop、反向多工输出mxon。

[0196]

请参见图11,其是列示根据本公开第一实施例的动态模块在预充电期间t

pre

与评鉴期间t

eva

的信号状态的摘要表。根据图9的说明,此处汇整动态模块6在预充电期间t

pre

的信号状态。根据图10a、图10b的说明,此处汇整动态模块6在评鉴期间t

eva

的信号状态。

[0197]

在预充电期间t

pre

,因为正向锁存时钟信号clk_k为低逻辑电平clk_l=0),且反向锁存时钟信号clkb_l为高逻辑电平(clkb_l=1)的缘故,第一轨对轨输出对(ap,an)与第二轨对轨输出对(bp,bn)不影响正向多工输出mxop、反向多工输出mxon。据此,存储电路65将正向保持多工输出mxop、反向多工输出mxon。

[0198]

在评鉴期间t

eva

,当正向先前决定位元s

po

为低逻辑电平(spo=0)且反向先前决定位元sb

po

为高逻辑电平(sb

po

=1)时,动态模块6选择性更新正向多工输出mxop、反向多工输出mxon随着第二轨对轨输出对(bp,bn)。另一方面,在评鉴期间t

eva

,当正向先前决定位元s

po

为高逻辑电平(s

po

=1),且反向先前决定位元sb

po

为低逻辑电平(sb

po

=0)时,动态模块6选择性更新正向多工输出mxop、反向多工输出mxon以第一轨对轨输出对(ap,an)。

[0199]

如图3所述,推测式dfe 15以递回方式运行,且偶数推测路径31与奇数推测路径33互相影响。为阐释如何将动态模块6应用至图5b的推测式dfe 3,接着以波形图说明推测式dfe 3采用动态模块6时的信号关系。

[0200]

请参见图12,其是以一数据流为例,说明如何根据本公开构想的第一实施例的推测式dfe对其进行处理的波形图。图12的上方为,系统时钟信号clk_sys、输入数据in(a)~in(f)、偶数路径的正向锁存时钟信号clk_l(even)与奇数路径的正向锁存时钟信号clk_l(odd)的波形。

[0201]

偶数动态模块315与奇数动态模块335同时接收系统时钟信号clk_sys与输入数据in(a)~in(f)。偶数动态模块315接收偶数路径的正向锁存时钟信号clk_l(even),奇数动态模块335接收奇数路径的正向锁存时钟信号clk_l(odd)。系统时钟信号clk_sys可能由锁相回路(phase-locked loop,简称为pll)提供。

[0202]

在本文中,假设在偶数路径的正向锁存时钟信号clk_l(even)为高逻辑电平(clk_l(even)=1)的期间,偶数推测路径31中的感测放大器313a、313b进行取样与保持操作,且奇数推测路径33的感测放大器333a、333b暂停操作。再者,此处假设在奇数路径的正向锁存时钟信号clk_l(odd)为高逻辑电平(clk_l(odd)=1)时,奇数推测路径31中的感测放大器333a、333b进行取样与保持操作;偶数推测路径33中的感测放大器313a、313b暂停操作。然而,在实际应用时,用于触发感测放大器313a、313b、333a、333b的锁存时钟信号的逻辑电

平,并不以此处的叙述为限。

[0203]

图12绘示两个虚线方框。上方的虚线方框中的波形为与偶数推测路径31相关的信号;下方的虚线方框中的波形为与奇数推测路径33相关的信号。

[0204]

图12绘示的输入数据in(a)~in(f)随系统时钟信号clk_sys的上升缘与下降缘变化。偶数推测路径31与奇数推测路径33交错处理输入数据in(a)~in(f)。偶数推测路径31由偶数路径的正向锁存时钟信号clk_l(even)触发后,对输入数据in(a)、in(c)、in(e)进行处理。奇数推测路径33由奇数路径的正向锁存时钟信号clk_l(odd)触发后,对输入数据in(b)、in(d)、in(f)进行处理。

[0205]

因时钟传递延迟t

clk2sa

的缘故,偶数路径的正向锁存时钟信号clk_l(even)的上升缘略为落后系统时钟信号clk_sys的上升缘,且奇数路径的正向锁存时钟信号clk_l(odd)的下降缘略为落后系统时钟信号clk_sys的上升缘。

[0206]

在偶数推测路径31中,当偶数路径的正向锁存时钟信号clk_l(even)为高逻辑电平(clk_l(even)=1)时,感测放大器313a、313b对输入数据in(a)、in(c)、in(e)取样并产生取样数据sa(a)、sa(c)、sa(e)。另一方面,当偶数路径的正向锁存时钟信号clk_l(even)为低逻辑电平(clk_l(even)=0)时,感测放大器313a、313b暂停操作。

[0207]

在奇数推测路径33中,当奇数路径的正向锁存时钟信号clk_l(odd)为高逻辑电平(clk_l(odd)=1)时,感测放大器333a、333b对输入数据in(b)、in(d)取样并产生取样数据sa(b)、sa(d)。当奇数路径的正向锁存时钟信号clk_l(odd)为低逻辑电平(clk_l(odd)=0)时,感测放大器333a、333b暂停操作。

[0208]

针对每一笔取样数据sa(a)~(e),推测式dfe 3将对应产生两组轨对轨输出对。偶数推测路径31中的两组轨对轨输出对包含:第一偶数路径的轨对轨输出对(apevn,anevn),以及第二偶数路径的轨对轨输出对(bpevn,bnevn)。奇数推测路径33中的两组轨对轨输出对包含:第一奇数路径的轨对轨输出对(apodd,anodd),以及第二奇数路径的轨对轨输出对(bpodd,bnodd)。

[0209]

当偶数路径的锁存时钟信号clk_l(even)的时钟电平等于高逻辑电平(clk_l(even)=1)时,在偶数推测路径31中,感测放大器313a根据取样数据sa(a)、sa(c)、sa(e)产生第一偶数路径的轨对轨输出对(apevn,anevn),且感测放大器313b根据取样数据sa(a)、sa(c)、sa(e)产生第二轨对轨输出对(bpevn,bnevn)。在t1、t3、t5期间,感测放大器313a所产生的第一偶数路径的轨对轨输出对(apevn,anevn)分别为,与取样数据sa(a)、sa(c)、sa(e)对应的sa(a)-、sa(c)-、sa(e)-;感测放大器313b所产生的第二偶数路径的轨对轨输出对(bpevn,bnevn)分别为,与取样数据sa(a)、sa(c)、sa(e)对应的sa(a)+、sa(c)+、sa(e)+。在此同时,奇数路径的正向锁存时钟信号clk_l(odd)的时钟电平等于低逻辑电平(clk_l(odd)=0),故奇数推测路径33中的感测放大器331a、331b并不会对任何输入数据进行取样与保持。

[0210]

当奇数路径的正向锁存时钟信号clk_l(odd)的时钟电平等于高逻辑电平(clk_l(odd)=1)时,偶数路径的锁存时钟信号clk_l(even)的时钟电平等于低逻辑电平(clk_l(even)=0),故偶数推测路径31中的感测放大器311a、311b不对任何输入数据进行取样与保持。此时,在奇数推测路径33中,感测放大器333a根据取样数据sa(b)、sa(d)产生第一奇数路径的轨对轨输出对(apodd,anodd),且感测放大器333b根据取样数据sa(b)、sa(d)产生

第二奇数路径的轨对轨输出对(bpodd,bnodd)。在t2、t4期间,感测放大器333a产生的第一奇数路径的轨对轨输出对(apodd,anodd),分别为与取样数据sa(b)、sa(d)对应的sa(b)-、sa(d)-;感测放大器333b产生的第二奇数路径的轨对轨输出对(bpodd,bnodd),分别为与取样数据sa(b)、sa(d)对应的sa(b)+、sa(d)+。

[0211]

在与偶数推测路径31对应的评鉴期间t

eva

内,偶数动态模块315产生偶数路径的正向多工输出mxopevn、偶数路径的反向多工输出mxonevn。与取样数据sa(c)、sa(e)对应的偶数路径的正向多工输出mxopevn为mx(c)、mx(e),且与取样数据sa(c)、sa(e)对应的偶数路径的反向多工输出mxonevn为mxb(c)、mxb(e)。

[0212]

在与奇数推测路径33对应的评鉴期间t

eva

,奇数动态模块335产生奇数路径的正向多工输出mxopodd、奇数路径的反向多工输出mxonodd。与取样数据sa(b)、sa(d)对应的奇数路径的正向多工输出mxopodd为mx(b)、mx(d),且与取样数据sa(b)、sa(d)对应的奇数路径的反向多工输出mxonodd为mxb(b)、mxb(d)。

[0213]

接着说明部分的输入数据的处理过程。请同时参见图5b、图12。首先,在偶数推测路径31中,对输入数据in(a)取样产生取样数据sa(a)。由于输入数据in(a)为第一笔输入数据,奇数动态模块335直接根据取样数据sa(a)选择与取样数据sa(b)对应的第一奇数路径的轨对轨输出对(apodd,anodd)或第二奇数路径的轨对轨输出对(bpodd,bnodd)。

[0214]

在奇数推测路径33中,对输入数据in(b)取样产生取样数据sa(b)。接着,感测放大器333a产生第一奇数路径的轨对轨输出对sa(b)-,感测放大器333b产生第二奇数路径的轨对轨输出对sa(b)+。在参考取样数据sa(a)后,奇数动态模块335选择以第一奇数路径的轨对轨输出对sa(b)-与第二奇数路径的轨对轨输出对sa(b)+的其中一者,作为与取样数据sa(b)对应的奇数路径的正向多工输出mxopodd、奇数路径的反向多工输出mxonodd,(即,mx(b)、mxb(b))。

[0215]

若奇数动态模块335选取第一奇数路径的轨对轨输出对sa(b)-时,奇数路径的正向多工输出mx(b)等于第一奇数路径的正极单轨输出apodd,且奇数路径的反向多工输出mxb(b)等于第一奇数路径的负极单轨输出anodd。若奇数动态模块335选取第二奇数路径的轨对轨输出对sa(b)+时,奇数路径的正向多工输出mx(b)等于第二奇数路径正极单轨输出bpodd,且奇数路径的反向多工输出mxb(b)等于第二奇数路径负极单轨输出bnodd。反向器337a、337b进一步将奇数路径的正向多工输出mx(b)、奇数路径的反向多工输出mxb(b)转换为奇数路径决定d

out_odd

。

[0216]

在偶数推测路径31中,对输入数据in(c)取样产生取样数据sa(c)。接着,感测放大器313a产生第一偶数路径的轨对轨输出对sa(c)-,感测放大器313b产生第二偶数路径的轨对轨输出对sa(c)+。在参考奇数路径决定d

out_odd

后,偶数动态模块315选择以第一偶数路径的轨对轨输出对sa(c)-与第二偶数路径的轨对轨输出对sa(c)+的其中一者,产生与取样数据sa(c)对应的偶数路径的正向多工输出mxopevn、偶数路径的反向多工输出mxonevn。即,mx(c)、mxb(c)。

[0217]

若偶数动态模块315选择第一偶数路径的轨对轨输出对sa(c)-时,偶数路径的正向多工输出mx(c)相当于第一偶数路径的正极单轨输出apevn,且反向多工输出mxb(c)相当于第一偶数路径的负极单轨输出anevn。若偶数动态模块315选择第二偶数路径的轨对轨输出对sa(c)+时,偶数路径的正向多工输出mx(c)相当于第二偶数路径正极单轨输出bpevn,

且偶数路径的反向多工输出mxb(c)相当于第二偶数路径负极单轨输出bnevn。反向器317a、317b进一步将偶数路径的正向多工输出mx(c)、偶数路径的反向多工输出mxb(c)转换为偶数路径决定d

out_evn

。

[0218]

对输入数据in(d)、in(f)的处理与对输入数据in(b)的处理相似;且,对输入数据in(e)的处理与对输入数据in(c)的处理相似。因此,此处不再说明对输入数据in(d)、in(e)、in(f)的处理。

[0219]

图12下方列出与输入数据in(b)相关的延迟成因。请同时参见图5b、图6、图12。感测放大器333a、333b的时钟传递延迟t

clk2sa

介于时点t1至时点t2间、感测放大器333a、333b的设置时间t

susa

介于时点t2至时点t3间,且奇数动态模块335的传递延迟t

dyn

介于时点t3至时点t5间。因此,奇数推测路径33的处理和传递延迟介于时点t1和时点t4间,且推测式第一阶抽头(tap1)的操作边限δt

tap1’介于时点t4与时点t5间。

[0220]

第二实施例

[0221]

图13a、图13b分别为,根据本公开第二实施例的动态模块7的方框图与电路设计。图14说明动态模块7在预充电期间t

pre

的运行。图15a、图15b、图16说明动态模块7在评鉴期间t

eva

的运行。图17列出动态模块7的不同的信号状态的组合。图18进一步说明如何将动态模块7应用于推测式dfe 3。

[0222]

请参见图13a,其是根据本公开第二实施例的动态模块的方框图。动态模块7包含上方骨牌电路71、下方骨牌电路73与存储电路75。存储电路75通过多工输出端点n

mxop

、n

mxon

而电连接于上方骨牌电路71与下方骨牌电路73。上方骨牌电路71包含动态锁存器713与多工器711,下方骨牌电路73包含动态锁存器733与多工器731。

[0223]

在上方骨牌电路71中,动态锁存器713包含相位设定电路713a、713b与决定选择级电路713c,且多工器711包含正极输出电路711a与负极输出电路711b。在下方骨牌电路73中,动态锁存器733包含相位设定电路733a、733b与决定选择级电路733c,且多工器731包含正极输出电路731a与负极输出电路731b。

[0224]

请参见图13b,其是根据本公开第二实施例的动态模块的电路设计的示意图。请同时参见图13a、图13b。

[0225]

接着说明上方骨牌电路71的元件与连接关系。在动态锁存器713中相位设定电路713a包含pmos晶体管upp与nmos晶体管upn,相位设定电路713b包含pmos晶体管unp与nmos晶体管unn,且决定选择级电路713c包含pmoa晶体管uinp、nmos晶体管uinn与交互耦接的反向器uinv1、uinv2。

[0226]

在相位设定电路713a中,pmos晶体管lpp与nmos晶体管lpn的栅极电连接于彼此,用于接收正向锁存时钟信号clk_l,且pmos晶体管lpp与nmos晶体管lpn的漏极均电连接于选择端点n

bp

。pmos晶体管upp的源极电连接于供应电压vcc,且nmos晶体管upn的源极电连接于决定选择级电路713c。在相位设定电路713b中,pmos晶体管unp与nmos晶体管unn的栅极电连接于彼此,用于接收锁存时钟信号clk_l,且pmos晶体管unp与nmos晶体管unn的漏极均电连接于选择端点n

an

。pmos晶体管unp的源极电连接于决定选择级电路713c,且nmos晶体管unn的源极电连接于接地端点gnd。

[0227]

在决定选择级电路713c中,pmos晶体管uinp的源极电连接于供应电压端点vcc,且pmos晶体管uinp的漏极电连接于相位设定电路713b。nmos晶体管uinn的源极电连接于接地

端点gnd,且nmos晶体管uinn的漏极电连接于相位设定电路713a。pmos晶体管uinp的栅极接收正向先前决定位元s

po

,且pmos晶体管uinn的栅极接收反向先前决定位元sb

po

。彼此交叉耦合的反向器uinv1、uinv2电连接于选择端点n

ap

、n

an

间。反向器uinv1的输入端点,以及反向器uinv2的输出端点电连接于选择端点n

ap

。反向器uinv1的输出端点,以及反向器uinv2的输入端点电连接于选择端点n

an

。

[0228]

在多工器711中,正极输出电路711a包含pmos晶体管upop1、upop2与nmos晶体管upon1、upon2;负极输出电路711b包含pmos晶体管unop1、unop2与nmos晶体管unon1、unon2。简言之,正极输出电路711a与正向多工输出mxop相关,负极输出电路711b与反向多工输出mxon相关。

[0229]

在正极输出电路711a中,pmos晶体管upop2的栅极电连接于选择端点n

ap

,且nmos晶体管upon2的栅极电连接于选择端点n

an

。pmos晶体管upop1与nmos晶体管upon1的栅极电连接于彼此,用以接收第一负极单轨输出an。pmos晶体管upop1的源极电连接于供应电压端点vcc,且pmos晶体管upop1的漏极电连接于pmos晶体管upop2的源极。nmos晶体管upon1的源极电连接于接地端点gnd,且nmos晶体管lnon1的漏极电连接于nmos晶体管upon2的源极。此外,pmos晶体管upop2与nmos晶体管upon2的漏极均电连接于正向多工输出端点n

mxop

。

[0230]

在负极输出电路711b中,pmos晶体管unop2的栅极电连接于选择端点n

ap

,且nmos晶体管upon2的栅极电连接于选择端点n

an

。pmos晶体管unop1与nmos晶体管unon1的栅极电连接于彼此,用以接收第一正极单轨输出ap。pmos晶体管unop1的源极电连接于供应电压端点vcc,且pmos晶体管unop1的漏极电连接于pmos晶体管unop2的源极。nmos晶体管unon1的源极电连接于接地端点gnd,且nmos晶体管unon1的漏极电连接于nmos晶体管unon2的源极。此外,pmos晶体管unop2与nmos晶体管unon2的漏极均电连接于反向多工输出端点n

mxon

。

[0231]

接着说明下方骨牌电路73的元件与连接关系。在动态锁存器733中,相位设定电路733a包含pmos晶体管lpp与nmos晶体管lpn;相位设定电路733b包含pmos晶体管lnp与nmos晶体管lnn;且决定选择级电路733c包含pmos晶体管linp、nmos晶体管linn与交互耦接的反向器linv1、linv2。

[0232]

在相位设定电路733b中,pmos晶体管lpp与nmos晶体管lpn的栅极电连接于彼此,用于接收正向锁存时钟信号clk_l,且pmos晶体管lpp与nmos晶体管lpn的漏极电连接于选择端点n

bp

。pmos晶体管lpp的源极电连接于供应电压vcc,nmos晶体管lpn的源极电连接于决定选择级电路733c。在相位设定电路733b中,pmos晶体管lnp与nmos晶体管lnn的栅极电连接于彼此,用于接收锁存时钟信号clkb_l,且pmos晶体管lnp与nmos晶体管lnn的漏极电连接于选择端点n

bn

。pmos晶体管lnp的源极电连接于决定选择级电路733c,nmos晶体管lpn的源极电连接于接地端点gnd。

[0233]

在决定选择级电路733c中,pmos晶体管linp的源极电连接于供应电压vcc,且pmos晶体管linp的漏极电连接于相位设定电路733b。nmos晶体管linn的源极电连接于接地端点gnd,且nmos晶体管linn的漏极电连接于相位设定电路733a。pmos晶体管linp的栅极接收反向先前决定位元sb

po

,且nmos晶体管linn的栅极接收正向先前决定位元s

po

。彼此交叉耦合的反向器linv1、linv2电连接于选择端点n

bp

、n

bn

间。反向器linv1的输入端点,以及反向器linv2的输出端点电连接于选择端点n

bp

。反向器linv1的输出端点,以及反向器linv2的输入端点电连接于选择端点n

bn

。

[0234]

在多工器731中,正极输出电路731a包含pmos晶体管lpop1、lpop2与nmos晶体管lpon1、lpon2;负极输出电路731b包含pmos晶体管lnop1、lnop2与nmos晶体管lnon1、lnon2。基本上,正极输出电路731a与正向多工输出mxop相关,且负极输出电路711b与反向多工输出mxon相关。

[0235]

在正极输出电路731a中,pmos晶体管lpop2的栅极电连接于选择端点n

bp

,nmos晶体管lpon2的栅极电连接于选择端点n

bn

。pmos晶体管lpop1与nmos晶体管lpon1的栅极电连接于彼此,用于接收第二负极单轨输出bn。pmos晶体管lpop1的源极电连接于供应电压端点vcc;pmos晶体管lpop1的漏极电连接于pmos晶体管lpop2的源极。nmos晶体管lpon1的源极电连接于接地端点gnd,且nmos晶体管lpon1的漏极电连接于nmos晶体管lpon2的源极。此外,pmos晶体管lpop2与nmos晶体管lpon2的漏极均电连接于正向多工输出端点n

mxop

。

[0236]

在负极输出电路731b中,pmos晶体管lnop2的栅极电连接于选择端点n

bp

,且nmos晶体管lnon2的栅极电连接于选择端点n

bn

。pmos晶体管lnop1与nmos晶体管lnon1的栅极电连接于彼此,用于接收第二正极单轨输出bp。pmos晶体管lpop1的源极电连接于供应电压端点vcc,且pmos晶体管lnop1的漏极电连接于pmos晶体管lnop2的源极。nmos晶体管lnon1的源极电连接于接地端点gnd,nmos晶体管lnon1的漏极电连接于nmos晶体管lnon2的源极。此外,pmos晶体管lnop2与nmos晶体管lnon2的漏极均电连接于反向多工输出端点n

mxon

。

[0237]

存储电路75包含交叉耦合的反向器sinv1、sinv2。反向器sinv1的输入端点与输出端点分别电连接于正向多工输出端点n

mxop

与反向多工输出端点n

mxon

。反向器sinv2的输入端点与输出端点分别电连接于反向多工输出端点n

mxon

与正向多工输出端点n

mxop

。

[0238]

请参见图14,其是根据本公开构想的第二实施例的动态模块,在于预充电期间t

pre

运行的示意图。以下分别说明上方骨牌电路71与下方骨牌电路73的运行。

[0239]

接着依序说明上方骨牌电路711中,相位设定电路713a、713b、决定选择级电路713c与多工器711的运行。由于正向锁存时钟信号clk_l处于低逻辑电平(clk_l=0),相位设定电路713a中的pmos晶体管upp导通,且nmos晶体管upn断开。由于反向锁存时钟信号clkb_l为高逻辑电平(clkb_l=1),pmos晶体管unp断开,且nmos晶体管unn导通。因此,在上方骨牌电路71中,选择信号sa_p等于供应电压vcc(sa_p=1),且选择信号sa_n等于接地电压gnd(sa_n=0)。

[0240]

由于选择信号sa_p等于供应电压vcc(sa_p=1),使正极输出电路711a中的pmos晶体管upop2断开,以及使负极输出电路731b中的pmos晶体管unop2断开。由于选择信号sa_n等于接地电压gnd(sa_n=0),正极输出电路711a中的nmos晶体管upon2断开,且负极输出电路731b中的nmos晶体管unon2断开。连带的,多工器711中,与多工输出端点n

mxon

、n

mxop

相关的pmos晶体管unop2、upop2与nmos晶体管unon2、upon2均断开,且上方骨牌电路7在预充电期间t

pre

不影响正向多工输出mxop、反向多工输出mxon。

[0241]

简言之,当动态模块7处于预充电期间t

pre

,上方骨牌电路71不更新正向多工输出mxop、反向多工输出mxon。在图14中,以点状网底绘示多工器711,用于表示多工器711在预充电期间t

pre

不影响正向多工输出mxop、反向多工输出mxon。

[0242]

下方骨牌电路73中的相位设定电路733a、733b、决定选择级电路733c以及多工器731的运行方式,均与在上方骨牌电路71中与其相对应的元件类似。由于pmos晶体管lop被正向锁存时钟信号clk_l(clk_l=0)导通的缘故,选择信号sb_p等于供应电压vcc(sb_p=

1)。因为反向锁存时钟信号clkb_l(clkb_l=1)导通nmos晶体管lnn的缘故,选择信号sb_n等于接地电压gnd(sb_n=0)。连带的,在多工器731中,与多工输出端点n

mxon

、n

mxop

相关的pmos晶体管lnop2、lpop2与nmos晶体管lnon2、lpon2均断开,且下方骨牌电路73在预充电期间t

pre

不影响正向多工输出mxop、反向多工输出mxon。图14以点状网底绘示多工器731,代表多工器731不影响正向多工输出mxop、反向多工输出mxon。

[0243]

接着说明动态锁存器713、813与多工器811、831在评鉴期间t

eva

的运行。图15a、图15b说明正向锁存时钟信号clk_l为高逻辑电平(clk_l=1),且反向锁存时钟信号clkb_l为低逻辑电平(clkb_l=0)时,动态模块7的运行。

[0244]

图15a是在正向先前决定位元s

po

为低逻辑电平(s

po

=0),且反向先前决定位元sb

po

为高逻辑电平(sb

po

=1)时,根据本公开构想的第二实施例的动态模块于评鉴期间t

eva

运行的示意图。另一方面,图15b是在正向先前决定位元s

po

为高逻辑电平(s

po

=1),且反向先前决定位元sb

po

为低逻辑电平(sb

po

=0)时,根据本公开构想的第二实施例的动态模块于评鉴期间t

eva

运行的示意图。

[0245]

请参见图16,其是根据本公开第二实施例的上方骨牌电路,运行于评鉴期间t

eva

的流程图。以下说明图15a、图15b所示的上方骨牌电路71的运行。首先,动态锁存器713同时产生选择信号sa_p(步骤s71)与选择信号sa_n(步骤s73)。

[0246]

由于锁存时钟信号clk_l(clk_l=1)导通nmos晶体管upn的缘故,决定选择级电路713c中的nmos晶体管uinn被导通至选择信号sa_p(步骤s71a),且选择信号sa_p由nmos晶体管uinn的导通状态决定。nmos晶体管uinn进一步由反向先前决定位元sb

po

控制(步骤s71b)。如图15a所示,当反向先前决定位元sb

po

为高逻辑电平(sb

po

=1)时,选择信号sa_p等于接地电压gnd(sa_p=0)。如图15b所示,当反向先前决定位元sb

po

为低逻辑电平(sb

po

=0)时,选择信号sb_n为浮接(sb_n=z)。

[0247]

由于反向锁存时钟信号clkb_l(clkb_l=1)导通pmos晶体管unp的缘故,决定选择级电路713c中的pmos晶体管uinp被导通至选择信号sa_n(步骤s73a),且选择信号sa_n由pmos晶体管uinp的导通状态决定。pmos晶体管uinp进一步由正向先前决定位元s

po

控制(步骤s73b)。如图15a所示,当正向先前决定位元s

po

为低逻辑电平(s

po

=0)时,选择信号sa_n等于供应电压vcc(sa_n=1)。如图15b所示,当正向先前决定位元s

po

为高逻辑电平(spo=1)时,选择信号sa_n为浮接(sa_n=z)。

[0248]

因此,选择信号sa_p随着反向先前决定位元sb

po

改变,且选择信号sa_n随着正向先前决定位元s

po

改变。因应正向先前决定位元s

po

、反向先前决定位元sb

po

的变化,须考虑两种不同的情形。

[0249]

当选择信号sa_p、sa_n为浮接(sa_p=z、sa_n=z)时,多工器711被禁能,且上方骨牌电路71不影响正向多工输出mxop、反向多工输出mxon(步骤s77)。图15b以点状网底绘示上方骨牌电路71的元件,代表在评鉴期间t

eva

,若正向先前决定位元s

po

为高逻辑电平(spo=1)且当反向先前决定位元为低逻辑电平(sb

po

=0)时,上方骨牌电路73不影响正向多工输出mxop、反向多工输出mxon。

[0250]

当选择信号sa_p为接地电压gnd(sa_p=0),且选择信号sa_n为供应电压(sa_n=1)时,多工器711基于第一正极单轨输出ap与第一负极单轨输出an产生正向多工输出mxop、反向多工输出mxon(mxop=ap且mxon=an)(步骤s75)。

[0251]

如图15a所示,低逻辑电平的选择信号sa_n(sa_n=0)导通正极输出电路711a中的pmos晶体管upop2,以及负极输出电路711b中的pmos晶体管unop2;高逻辑电平的选择信号sa_n(sa_n=1)导通正极输出电路711a的nmos晶体管upon1与负极输出电路711b的nmos晶体管unon2。

[0252]

接着,正向多工输出mxop由正极输出电路711a中的pmos晶体管upop1与nmos晶体管unon1的导通状态决定。其中,pmos晶体管upop1与nmos晶体管unon1由第一负极单轨输出an控制(步骤s75a)。另一方面,反向多工输出mxon由负极输出电路711b中的pmos晶体管unop1与nmos晶体管unon1的导通状态决定。其中,pmos晶体管unop1与nmos晶体管unon1由第一正极单轨输出ap控制(步骤s75b)。

[0253]

步骤s75需考虑第一轨对轨输出对的两种情形:(ap=0且an=1)与(ap=1且an=0)。

[0254]

首先说明ap=0且an=1的情形。由于第一负极单轨输出an为高逻辑电平(an=1),在正极输出电路711a中,pmos晶体管upop1断开,且nmos晶体管upon1导通。连带的,正向多工输出mxop等于接地电压gnd(mxop=0)。在此同时,在负极输出电路711b中,由于第一正极单轨输出ap为低逻辑电平(ap=0)的缘故,pmos晶体管unop1导通,且nmos晶体管unon1断开。连带的,反向多工输出mxon等于供应电压vcc(mxon=1)。因此,当第一轨对轨输出对(ap,an)满足第一正极单轨输出ap为低逻辑电平(ap=0),且第一负极单轨输出an为的情况为高逻辑电平(an=1)时,正向多工输出mxop与第一正极单轨输出ap的关系为mxop=ap=0,且反向多工输出mxon与第一负极单轨输出an的关系为mxon=an=1。

[0255]

接着说明ap=1且an=0的情形。由于第一负极单轨输出an为低逻辑电平(an=0)的缘故,在正极输出电路711a中,pmos晶体管upop1导通,且nmos晶体管upon1断开。据此,正向多工输出mxop等于供应电压vcc(mxop=1)。在此同时,由于第一正极单轨输出ap为高逻辑电平(ap=1)的缘故,在负极输出电路711b中,pmos晶体管unop1断开,且nmos晶体管unon1导通。连带的,反向多工输出mxon等于接地电压gnd(mxon=0)。因此,当第一轨对轨输出对(ap,an)符合第一正极单轨ap输出为高逻辑电平(ap=1),且第一负极单轨输出an为低逻辑电平(an=0)的条件时,正向多工输出mxop与第一正极单轨输出ap的关系为mxop=ap=1,且反向多工输出mxon与第一负极单轨输出an的关系为mxon=an=0。

[0256]

当动态模块7处于评鉴期间t

eva

时,上方骨牌电路71中的相位设定电路713a、713b、决定选择级电路713c与多工器711依序动作。相位设定电路713a、713b先判断决定选择级电路713c是否与上方骨牌电路81中的选择信号sa_p、sa_n相关。若否(如图15b所示),上方骨牌电路71中的选择信号sa_p、sa_n为浮接(sa_p=z、sa_n=z)。若是(如图15a所示),上方骨牌电路71中的选择信号sa_p、sa_n将致能正极输出电路711a与负极输出电路711b,且第一轨对轨输出对ap、an用于更新正向多工输出多工输出mxop、反向多工输出mxonn。即,mxop=ap、mxon=an。

[0257]

在图15a、图15b中,下方骨牌电路73与上方骨牌电路71的运行类似,故不再详述其细节。当动态模块7运行于评鉴期间t

eva

时,相位设定电路733a、733b先判断决定选择级电路733c是否与下方骨牌电路73中的选择信号sb_p、sb_n相关。若否(如图15a所示),下方骨牌电路73中的选择信号sb_p、sb_n为浮接(sb_p=z、sb_n=z)。若是(如图15b所示),下方骨牌电路73中的选择信号sb_p、sb_n将致能正极输出电路731a与负极输出电路731b,并利用第

二轨对轨输出对(bp,bn)更新正向多工输出mxop、反向多工输出mxon。即,mxop=bp且mxon=bn。

[0258]

以上说明动态模块7如何因应不同的输入信号而运行的细节。为便于比较,图17绘示不同的输入信号的组合,以及与其对应的正向多工输出mxop、反向多工输出mxon。

[0259]

请参见图17,其是列示根据本公开第二实施例的动态模块在预充电期间t

pre

与评鉴期间t

eva

的信号状态的摘要表。动态模块7在预充电期间t

pre

的运行,可从图14、图15a、图15b、图16的说明归纳得出。

[0260]

在预充电期间t

pre

,锁存时钟信号clk_l为低逻辑电平(clk_l=0),且反向锁存时钟信号clkb_l为高逻辑电平(clkb_l=1)。据此,选择信号sa_p为高逻辑电平(sa_p=1);选择信号sa_n为低逻辑电平(sa_n=0);选择信号sb_p为高逻辑电平(sb_p=1);以及,选择信号sb_n为低逻辑电平(sb_n=0)。根据选择信号sa_p、sa_n、sb_p、sb_n,正向先前决定位元s

po

、反向先前决定位元sb

po

、第一轨对轨输出对(ap,an)以及第二轨对轨输出对(bp,bn)不影响正向多工输出mxop、反向多工输出mxon,且存储电路75保持正向多工输出mxop、反向多工输出mxon。

[0261]

在评鉴期间t

eva

,选择信号sa_p、sa_n、sb_p、sb_n随着正向先前决定位元s

po

、反向先前决定位元sb

po

而变化。若正向先前决定位元s

po

为低逻辑电平(s

po

=0),且反向先前决定位元sb

po

为高逻辑电平(sb

po

=1)时,上方骨牌电路71中的选择信号sa_p、sa_n与正向先前决定位元s

po

、反向先前决定位元sb

po

的关系为,sa_p=0=s

po

、sa_n=1=sb

po

。且,下方骨牌电路73中的选择信号sb_p、sb_n为浮接(sb_p=z、sb_n=z)。接着,以第一轨对轨输出对(ap,an)更新正向多工输出mxop、反向多工输出mxon(mxop=ap、mxon=an)。另一方面,若正向先前决定位元s

po

为高逻辑电平(s

po

=1),且反向先前决定位元sb

po

为低逻辑电平(sb

po

=0)时,下方骨牌电路73中的选择信号sb_p、sb_n与正向先前决定位元s

po

、反向先前决定位元sb

po

的关系为,sb_p=0=s

po

、sb_n=1=sb

po

。且,在上方骨牌电路71中的选择信号sa_p、sa_n为浮接(sa_p=z,sa_n=z)。接着,以第二轨对轨输出对(bp,bn)更新正向多工输出mxop、反向多工输出mxon(mxop=bp、mxon=bn)。

[0262]

如上所述,推测式dfe 3是以递回的方式运行,且偶数推测路径31与奇数推测路径33互相影响。为阐释如何将动态模块7应用至推测dfe 3,接着以波形图说明当推测式dfe 3采用动态模块7时的信号关系。

[0263]

请参见图18,其是根据本公开构想的第二实施例的推测式dfe,对一数据流的例子进行处理的波形图。除选择信号sa_p、sa_n、sb_p、sb_n外,图12、图18的波形均类似。因此,此处不重复说明系统时钟信号clk_sys、输入数据in(a)~in(f)、偶数路径正向锁存时钟信号clk_l(even)、奇数路径正向锁存时钟信号clk_l(odd)、轨对轨输出对(apevn,anevn)、(bpevn,bnevn)、(apodd,anodd)、(bpodd,bpevn)与偶数/奇数路径的正向/反向多工输出(mxopevn、mxonevn、mxopodd、mxonodd)的波形。

[0264]

在偶数推测路径31中,选择信号sa_p、sa_n用于决定第一偶数路径的轨对轨输出对(apevn,anevn)是否应被选为偶数路径的正向多工输出mxopevn、偶数路径的反向多工输出mxonevn;选择信号sb_p、sb_n用于决定第二偶数路径的轨对轨输出对(bpevn,bnevn)是否应被选为偶数路径的正向多工输出mxopevn、偶数路径的反向多工输出mxonevn。因为相位设定电路的传递延迟的缘故,在偶数推测路径31中,选择信号sb_p、sb_n产生的期间落后

于第一偶数路径的轨对轨输出对(apevn,anevn)、第二偶数路径的轨对轨输出对(bpevn,bnevn)产生的期间,且偶数路径的正向多工输出mxopevn、偶数路径的反向多工输出mxonevn的产生期间落后于偶数推测路径31中,选择信号sb_p、sb_n的产生期间。偶数推测路径31针对与取样数据sa(a)产生的选择信号sa_p、sa_n、sb_p、sb_n分别标示为ap(a)、an(a)、bp(a)、bn(a)。偶数推测路径31针对与取样数据sa(c)、sa(e)产生的选择信号sa_p、sa_n、sb_p、sb_n的标示方式类似而不重复说明。

[0265]

在奇数推测路径33中的选择信号sa_p、sa_n用于决定是否选取第一奇数路径的轨对轨输出对(apodd,anodd)作为奇数路径的正向多工输出mxopodd、奇数路径的反向多工输出mxonodd;选择信号sb_p、sb_n用于决定是否选取第二奇数路径的轨对轨输出对(bpodd,bnodd)作为奇数路径的正向多工输出mxopodd、奇数路径的反向多工输出mxonodd。因为相位设定电路的传递延迟的缘故,在奇数推测路径33中,选择信号sb_p、sb_n的产生期间落后于第一奇数路径的轨对轨输出对(apodd,anodd)、第二偶数路径的轨对轨输出对(bpodd,bnodd)的产生期间,且奇数路径的正向多工输出mxopodd、奇数路径的反向多工输出mxonodd的产生期间落后于奇数推测路径33中的选择信号sb_p、sb_n产生的期间。奇数推测路径33针对与取样数据sa(b)产生的选择信号sa_p、sa_n、sb_p、sb_n分别标示为ap(b)、an(b)、bp(b)、bn(b)。奇数推测路径33针对与取样数据sa(d)产生的选择信号sa_p、sa_n、sb_p、sb_n的标示方式类似而不重复说明。

[0266]

图18的下方绘示产生输入数据in(b)的推测式第一阶抽头(tap1)的延迟成因。请同时参见图5b、图6、图18。感测放大器333a、333b的时钟传递延迟t

clk2sa

介于时点t1与时点t2间,感测放大器333a、333b的设置时间t

susa

介于时点t2与时点t3间,且奇数动态模块335的传递延迟t

dyn

介于时点t3与时点t5间。因此,奇数推测路径33的处理和传递延迟介于时点t1和时点t4间,且推测式第一阶抽头(tap1)的操作边限介于时点t4与时点t5间。

[0267]

请同时参见图12、图18。在图12中,第一实施例的正向多工输出mxop、反向多工输出mxon直接由第一轨对轨输出对(ap,an)与第二轨对轨输出对(bp,bn)决定。另一方面,在图18中,第二实施例的多工输出正向多工输出mxop、反向多工输出mxon间接通过由第一轨对轨输出对(ap,an)与第二轨对轨输出对(bp,bn)决定的选择信号sa_p、sa_n、sb_p、sb_n而决定。因此,动态模块6的传递延迟t

dyn

较动态模块7的传递延迟t

dyn

短。

[0268]

换言之,第一实施例与第二实施例的正向多工输出mxop、反向多工输出mxon,分别为以单一阶段的方式与两阶段的方式产生。即,与第一实施例直接基于单轨输出(ap,an)、(bp,bn)产生正向多工输出mxop、反向多工输出mxon不同的是,第二实施例是在产生选择信号(sa_p、sa_n、sb_p、sb_n)后,方利用选择信号(sa_p、sa_n、sb_p、sb_n)产生正向多工输出mxop、反向多工输出mxon。

[0269]

第三实施例

[0270]

图19a、图19b分别为,根据本公开第三实施例的动态模块8的方框图与电路设计。图20说明动态模块8在预充电期间t

pre

的运行。图21a、图21b、图22说明动态模块8在评鉴期间t

eva

的运行。图23列出动态模块8的不同的信号状态的组合。

[0271]

请参见图19a,其是根据本公开构想的第三实施例的动态模块的方框图。动态模块8包含上方骨牌电路81、下方骨牌电路83与存储电路85。上方骨牌电路81还包含动态锁存器813与多工器811,且下方骨牌电路63还包含动态锁存器833与多工器831。

[0272]

请同时参见图13a、图19a。图13a的动态模块与图19a的动态模块具有类似的元件和连线关系。动态模块7与动态模块8的差异处为,多工器711、811、731、831的位置与排列方式。在动态模块7中,多工器711与多工器731内的元件沿纵向排列。另一方面,在动态模块8中,多工器811与多工器831内的元件沿横向排列。

[0273]

请参见图19b,其是根据本公开的第三实施例的动态模块的电路设计的示意图。由于第三实施例的动态锁存器813、833与第二实施例的动态锁存器相似,此处不再说明动态锁存器813、833内的元件与连接关系,仅说明多工器811、831的元件与连接关系。基本上,正极输出电路811a、831a与负极输出电路811b、831b采用传输闸实现。

[0274]

在多工器811中,正极输出电路811a包含pmos晶体管upop与nmos晶体管upon,且负极输出电路811b包含pmos晶体管unop与nmos晶体管unon。pmos晶体管upop、unon的栅极电连接于选择端点n

ap

。nmos晶体管upon、unon的栅极电连接于选择端点n

an

。接着说明多工器811的元件间的信号关系。

[0275]

在正极输出电路811中,pmos晶体管upop源极与nmos晶体管upon的漏极共同接收第一正极单轨输出ap,且pmos晶体管upop的漏极与nmos晶体管的源极电连接于正向多工输出端点n

mxop

。在负极输出电路811b中,pmos晶体管unop的源极与nmos晶体管unon的漏极共同接收第一负极单轨输出an,且pmos晶体管unop的漏极与nmos晶体管unon的源极电连接于反向多工输出端点n

mxon

。

[0276]

在多工器831中,正极输出电路831a包含pmos晶体管lpop与nmos晶体管lpon,且负极输出电路831b包含pmos晶体管lnop与nmos晶体管lnon。pmos晶体管lpop、lnop的栅极均电连接于选择端点n

bp

。nmos晶体管lpon、lnon的栅极均电连接于选择端点n

bn

。接着说明多工器811的信号关系。

[0277]

在正极输出电路831a中,pmos晶体管lpop的源极与nmos晶体管lpon的漏极共同接收第二正极单轨输出bp,且pmos晶体管lpop的漏极与nmos晶体管lpon的源极电连接于正向多工输出端点n

mxop

。在负极输出电路831b中,pmos晶体管lnop的源极与nmos晶体管lnon的漏极共同接收第二负极单轨输出bn,且pmos晶体管lnop的漏极与nmos晶体管lnon的源极电连接于反向多工输出端点n

mxon

。

[0278]

存储电路85包含交叉耦合的反向器sinv1、sinv2。反向器sinv1的输入端点与输出端点分别电连接于正向多工输出端点n

mxop

与反向多工输出端点n

mxon

。反向器sinv2的输入端点与输出端点分别电连接于反向多工输出端点n

mxon

与正向多工输出端点n

mxop

。

[0279]

请参见图20,其是根据本公开构想的第三实施例的动态模块,在预充电期间t

pre

如何运行的示意图。由于第三实施例的相位设定电路813a、813b、决定选择级电路813c均与第二实施例相似,产生选择信号sa_p=1、sa_n=0、sb_p=1、sb_n=0的方式也与图14相似,此处不再说明。

[0280]

接着说明多工器811的运行。由于选择信号sa_p等于供应电压vcc(sa_p=1),正极输出电路811a中的pmos晶体管upop断开,且在负极输出电路811b中的pmos晶体管unop断开。由于选择信号sa_n等于接地电压gnd(sa_n=0),正极输出电路811a中的nmos晶体管upon断开,且负极输出电路811b中的nmos晶体管unon断开。在预充电期间t

pre

,由于多工器811中的pmos晶体管upop、unop与nmos晶体管upon、unon均断开的缘故,多工器811被禁能,故上方骨牌电路81不影响正向多工输出mxop、反向多工输出mxon。

[0281]

同理,因为选择信号sb_p等于供应电压vcc(sb_p=1),且选择信号sb_n等于接地电压gnd(sb_n=0)的缘故,多工器831中的pmos晶体管lpop、lnop与nmos晶体管lpon、lnon均为断开。因此,根据本公开的第三实施例,在预充电期间t

pre

,多工器831被禁能,故下方骨牌电路83不影响正向多工输出mxop、反向多工输出mxon。

[0282]

在预充电期间t

pre

,存储电路65将正向多工输出mxop、反向多工输出mxon保持在如评鉴期间t

eva

所存储的状态。在图20中,以点状网底绘示多工器811、831,代表多工器811、831在预充电期间t

pre

被禁能。

[0283]

图21a、图21b,其是说明动态模块8在评鉴期间t

eva

运行时,动态模块8的信号与元件状态。请参见图21a,其系在正向先前决定位元s

po

为低逻辑电平(s

po

=0),且反向先前决定位元sb

po

为高逻辑电平(sb

po

=1)时,根据本公开的第三实施例的动态模块于评鉴期间t

eva

运行的示意图。请参见图21b,其是在正向先前决定位元s

po

为高逻辑电平(s

po

=1),且反向先前决定位元sb

po

为低逻辑电平(sb

po

=0)时,根据本公开的第三实施例的动态模块于评鉴期间t

eva

运行的示意图。

[0284]

请参见图22,其是根据本公开构想的第三实施例的上方骨牌电路,运行于评鉴期间t

eva

的流程图。请同时参见图21a、图21b、图22。

[0285]

如前所述,动态锁存器813的元件与其连接关系与第二实施例的动态锁存器713相似。是故,图22的步骤s81a、s81b、s83a、s83b与图16的步骤s71a、s71b、s73a、s73b相似且此处不予重述。此处仅说明步骤s85、s87。

[0286]

当选择信号sa_p、sa_n为浮接(sa_p=z、sa_n=z)时,多工器811被禁能,且上方骨牌电路71不影响正向多工输出mxop、反向多工输出mxon(步骤s87)。在图21b中,以点状网底绘示上方骨牌电路83,用以表示当正向先前决定位元s

po

为高逻辑电平(s

po

=1),且反向先前决定位元sb

po

为低逻辑电平(sb

po

=0)时,上方骨牌电路83不影响正向多工输出mxop、反向多工输出mxon。

[0287]

当选择信号sa_p为接地电压gnd(sa_p=0),且选择信号sa_n为供应电压vcc(sa_n=1)时,多工器811依据第一正极单轨输出ap与第一负极单轨输出an产生正向多工输出mxop、反向多工输出mxon。即,mxop=ap且mxon=an(步骤s85)。

[0288]

如图21a所示,低逻辑电平的选择信号sa_n(sa_n=0)导通正极输出电路811a中的pmos晶体管upop,与负极输出电路811b中的pmos晶体管unop;以及,高逻辑电平的选择信号sa_n(sa_n=1)导通正极输出电路811a中的nmos晶体管upon,与负极输出电路811b中的nmos晶体管unon。

[0289]

接着,正极输出电路811a将第一正极单轨输出ap导通至正向多工输出端点n

mxop

,作为正向多工输出mxop(步骤s85a)。另一方面,负极输出电路811b将第一负极单轨输出ap导通至反向多工输出端点n

mxon

,以其作为反向多工输出mxon(步骤s85b)。

[0290]

根据图22,当动态模块8操作在评鉴期间t

eva

时,上方骨牌电路81中的相位设定电路813a、813b、决定选择级电路813c与多工器811依序动作。相位设定电路813a、813b先判断决定选择级电路813c是否与上方骨牌电路81中的选择信号sa_p、sa_n相关。若否(请参见图21b),选择信号sa_p、sa_n为浮接(sa_p=z、sa_n=z),且多工器811为禁能。若是(请参见图21a),选择信号sa_p、sa_n将致能正极输出电路811a与负极输出电路811b,且第一轨对轨输出对ap、an用于更新正向多工输出mxop、反向多工输出mxon。即,mxop=ap且mxon=an。

[0291]

在图21a、图21b图中,下方骨牌电路83上方骨牌电路81的运行对称,故不再详述其细节。当动态模块8在评鉴期间t

eva

运行时,下方骨牌电路83中的相位设定电路833a、833b、决定选择级电路833c与多工器711依序动作。相位设定电路833a、833b先判断决定选择级电路833c是否与下方骨牌电路83中的选择信号sb_p、sb_n相关。若否(如图21a所示),选择信号sb_p、sb_n为浮接(sb_p=z、sb_n=z),且多工器831被禁能。若是(如图21b所示),选择信号sb_p、sb_n致能正极输出电路831a与负极输出电路831b,并利用第二轨对轨输出对(bp,bn)更新多工输出正向多工输出mxop、反向多工输出mxon。即,mxop=bp且mxon=bn。

[0292]

请参见图23,其是在预充电期间t

pre

与评鉴期间t

eva

,根据本公开构想的第三实施例的动态模块的信号状态的摘要表。动态模块8在预充电期间t

pre

的操作可自图20推导得出。动态模块8在评鉴期间t

eva

的操作可自图21a、图21b、图22推导得出。

[0293]

在预充电期间t

pre

,因为正向锁存时钟信号clk_l为低逻辑电平(clk_l=0),且反向锁存时钟信号clkb_l为高逻辑电平(clkb_l=1)的缘故,选择信号sa_p等于供应电压vcc(sa_p=1);选择信号sa_n等于接地电压gnd(sa_n=0);选择信号sb_p等于供应电压vcc(sb_p=1);以及,选择信号sb_n等于接地电压gnd(sb_n=0)。根据选择信号sa_p、sa_n、sb_p、sb_n,多工器811、831被禁能,且正向多工输出mxop、反向多工输出mxon不受正向先前决定位元s

po

、反向先前决定位元sb

po

影响。连带的,存储电路85维持正向多工输出mxop、反向多工输出mxon。

[0294]

在评鉴期间t

eva

,选择信号sa_p、sa_n、sb_p、sb_n随着正向先前决定位元s

po

、反向先前决定位元sb

po

而改变。在评鉴期间t

eva

,若正向先前决定位元s

po

为低逻辑电平(s

po

=0),且反向先前决定位元sb

po

为高逻辑电平(sb

po

=1)时,上方骨牌电路81中的选择信号sa_p、sa_n与正向先前决定位元s

po

、反向先前决定位元sb

po

的关系为,sa_p=0=s

po

、sa_n=1=sb

po

。且,在下方骨牌电路83中的选择信号sb_p、sb_n为浮接(sb_p=z,sb_n=z)。接着,以第一轨对轨输出对(ap,an)更新正向多工输出mxop、反向多工输出mxon。另一方面,在评鉴期间t

eva

,若正向先前决定位元s

po

为高逻辑电平(s

po

=1),且反向先前决定位元sb

po

为低逻辑电平(sb

po

=0)时,下方骨牌电路中的选择信号sb_p、sb_n与正向先前决定位元s

po

、反向先前决定位元sb

po

关系为,sb_p=0=s

po

、sb_n=1=sb

po

。且,在上方骨牌电路81中的选择信号sa_p、sa_n为浮接(sa_p=z、sa_n=z)。接着,以第二轨对轨输出对(bp,bn)更新正向多工输出mxop、反向多工输出mxon。

[0295]

前述的推测式dfe的实施例可以纾解推测式第一阶抽头(tap1)的时间要求,且将动态模块内的锁存器与动态模块合并在一起,可进一步节省较多的时间边限。本公开亦可以四等分速率实现。

[0296]

请参见图24,其是具有四等分速率结构的推测式dfe的示意图。推测式dfe 90包含四个等分路径,即,推测路径91、92、93、94。推测路径91、92、93、94接收输入数据d

in

,且推测路径91、92、93、94分别产生路径决定d

out_p1

、d

out_p2

、d

out_p3

、d

out_p4

。路径决定d

out_p1

、d

out_p2

、d

out_p3

、d

out_p4

共同形成dfe输出d

out

。由于推测式dfe 90的操作可基于前述半速率推测式架构的实施例而推导得出,此处不再详细说明推测式dfe 90。

[0297]

综上所述,虽然本发明已以实施例公开如上,然其并非用以限定本发明。本发明所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,当可作各种的更动与润饰。因此,本发明的保护范围当视后附的权利要求所界定者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1