一种基于并行LVDS接口的高速数据采集系统

一种基于并行lvds接口的高速数据采集系统

技术领域

1.本发明属于信号采集领域,涉及并行lvds接口形式的高速数字信号的采集,尤其是一种基于并行lvds接口的高速数据采集系统。

背景技术:

2.随着5g时代的到来,移动网络的数据传输速率逐步提升解决了超高清等领域面临的高数据传输速率的问题,使得这些领域蓬勃发展。与此同时,超高清等领域的数据源所产生的数据量也在逐步增加,对后级数据采集系统的数据传输速率提出了新的要求。而现有的并行lvds接口的数据采集系统仅用32位lvds接口采集数据,其最高存储速度仅为800mb/s,远低于采集和缓存4k 60fps的超高清视频数据所需的数据传输速率。

技术实现要素:

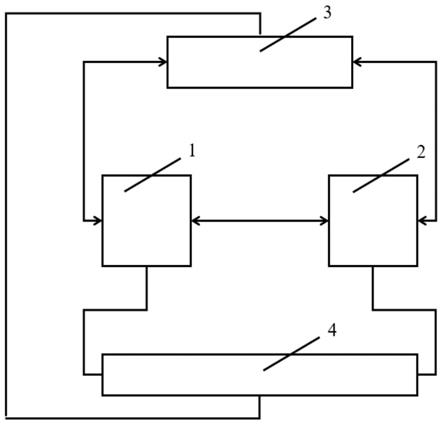

3.本发明的目的是针对现有的数据采集系统数据传输速率不够高而提供的一种基于并行lvds接口的高速数据采集系统,本发明采用soc

‑

fpga可编程门阵列zynq ultrascale

+

子系统、fpga可编程门阵列kintex子系统、子板模块、电源模块,针对大数据量信号源的高速数据采集应用开发。

4.本发明的数据采集接口为并行的lvds接口,数据传输速率最高可达160gb/s,满足超高清数据传输速率的要求,能够应用在超高清等需要高数据传输率的领域中。本发明采用两片fpga实现高速数字信号的采集,拥有usb、uart、万兆以太网光口sfp+等多种拓展接口,能将本地采集的数据发送到上位机,由上位机软件实现数据的显示与存储。

5.实现本发明的具体技术方案是:

6.一种基于并行lvds接口的高速数据采集系统,它包括soc

‑

fpga可编程门阵列zynq ultrascale

+

子系统、fpga可编程门阵列kintex子系统、子板模块、电源模块,所述的soc

‑

fpga可编程门阵列zynq ultrascale

+

子系统分别与fpga可编程门阵列kintex子系统、子板模块连接;fpga可编程门阵列kintex子系统与soc

‑

fpga可编程门阵列zynq ultrascale

+

子系统、子板模块连接;电源模块为soc

‑

fpga可编程门阵列zynq ultrascale

+

子系统、fpga可编程门阵列kintex子系统及一子板模块供电;其中:

7.所述的soc

‑

fpga可编程门阵列zynq ultrascale

+

子系统包括zynq ultrascale

+

芯片、4gb 64bit ddr4存储器、第一flash模块、usb模块、usb

‑

uart接口、sd卡及一与子板连接的lvds接口,所述的4gb64bitddr4存储器、第一flash模块、usb模块、usb

‑

uart接口、sd卡、子板lvds接口分别与zynq ultrascale

+

芯片连接;

8.所述的fpga可编程门阵列kintex子系统包括kintex7芯片、sfp/sfp+万兆以太网光口、第二flash模块及一子板控制io接口、所述的sfp/sfp+万兆以太网光口、第二flash模块、子板控制io接口分别与kintex7芯片连接;

9.所述的子板模块包括子板、产生高速数字信号的信号源芯片、lvds接口及一单端io接口,所述的产生高速数字信号的信号源芯片、lvds接口、单端io接口分别与子板连接;

ultrascale

+

芯片11、4gb 64bit ddr4存储器12、第一flash模块13、usb模块14、usb

‑

uart接口15、sd卡16及一与子板连接的lvds接口17,所述的4gb 64bit ddr4存储器12、第一flash模块13、usb模块14、usb

‑

uart接口15、sd卡16、子板lvds接口17分别与zynq ultrascale

+

芯片11连接;zynq ultrascale

+

芯片11通过serdes接口向kintex7芯片21传输采集到的高速数据信号;本子系统中4gb 64bit ddr4存储器12用于采集数据的缓存,核心频率为2400mhz。

25.参阅图3,所述的fpga可编程门阵列kintex子系统2包括kintex7芯片21、sfp/sfp+万兆以太网光口22、第二flash模块23及一子板控制io接口24,所述的sfp/sfp+万兆以太网光口22、第二flash模块23、子板控制io接口24分别与kintex7芯片21连接;kintex7芯片21通过serdes接口接收zynq ultrascale

+

芯片11传来的高速数据信号;本子系统中的子板控制io接口24是使用电平转换芯片实现的40路电平可调io接口,其可兼容1.2v,1.5v,1.8v,2.5v,3.3v的逻辑电平,为子板模块3上产生高速数字信号的信号源芯片32提供不同电平的控制信号。

26.参阅图4,所述的子板模块3包括子板31、产生高速数字信号的信号源芯片32、lvds接口33及一单端io接口34,所述的产生高速数字信号的信号源芯片32、lvds接口33、单端io接口34分别与子板31连接;子板31通过lvds接口33连接到soc

‑

fpga可编程门阵列zynq ultrascale

+

子系统1中的与子板连接的lvds接口17上;子板31通过单端io接口34连接到fpga可编程门阵列kintex子系统2中的子板控制io接口24上;lvds接口33和单端io接口34为两个通用的qsh系列90pin的接口,其中单路lvds接口的数据传输速率为1.6gbps,共有100对lvds信号,最高的数据传输速率为160gbps。

27.参阅图5,所述的usb模块14由usb3.0接口141、usb2.0接口芯片142组成;其中usb3.0接口141中的usb3.0高速差分信号与soc

‑

fpga可编程门阵列zynq ultrascale

+

子系统1中的zynq ultrascale

+

芯片11连接;usb3.0接口141中的usb2.0差分信号与usb2.0接口芯片142连接;usb2.0接口芯片142与soc

‑

fpga片上系统可编程门阵列zynq ultrascale子系统1中的zynq ultrascale

+

芯片11连接。usb3.0接口信号直接从zynq芯片11连接到usb3.0母座,usb2.0接口信号通过usb2.0接口芯片142将信号转为usb2.0差分对连接到usb3.0母座;本发明通过此种方式兼容usb2.0与usb3.0模式。

28.实施例

29.参阅图6,本发明构成的基于并行lvds接口的高速数据采集系统,kintex子系统2中的子板控制io接口24为子板模块3上的信号源芯片32提供所需的控制信号,zynq ultrascale

+

子系统1上的子板lvds接口17接收子板31传来的高速数据,再将数据存储在4gb 64bitddr4存储器12内实现接收数据的缓存。最终通过zynq ultrascale

+

子系统1上的usb模块14或者传输到kintex子系统2通过其上的sfp/sfp+万兆以太网光口22,将缓存的数据传输到上位机中进行显示和存储。

30.具体工作过程:

31.系统上电后,zynq ultrascale

+

芯片11从第一flash模块13中读取编译代码,kintex7芯片21从第二flash模块23中读取编译代码,系统启动。之后,kintex子系统2中的子板控制io接口24产生子板模块3上的信号源芯片32所需的控制信号并通过单端io接口34将控制信号传输给信号源芯片32。信号源芯片32接收到控制信号后,通过lvds接口33输出

高速数据信号,zynq ultrascale

+

子系统1上的与子板连接lvds接口17接收子板31上lvds接口33传来的高速数据并将其传给zynq ultrascale

+

芯片11。接着,zynq ultrascale

+

芯片11将数据存储在4gb 64bit ddr4存储器12内实现接收数据的缓存。随后,zynq ultrascale

+

芯片11将4gb 64bit ddr4存储器12中缓存的数据读出,通过zynq ultrascale

+

芯片11上的serdes接口将数据传输到kintex7芯片21中,最终通过kintex子系统2上的sfp/sfp+万兆以太网光口22,将缓存的数据传输到上位机中进行显示和存储。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1