一种量子密钥分发的光源编码驱动系统的制作方法

1.本发明涉及量子信息与光通信领域,具体涉及一种量子密钥分发的光源编码驱动系统。

背景技术:

2.在量子密钥分发系统中,光源编码驱动系统负责将alice端单光子信号调控编码后,发送到量子信道,bob端的收到光子信息后进行解码。

3.传统的qkd光编码方式是单偏振的或单相位的,一个单光子只携带1bit编码信息,这种编码方式,光子在传输的过程中,会受到一定的损耗,大大降低了密钥的生成率。

4.因此需要对现有的量子编码方式进行改进,专利公开号为cn111555863a,专利名称为《用于时间相位

‑

偏振联合编码的发送端、编码方法及量子密钥分发系统》专利提供了一种高维的联合编码方式,对1个光子同时进行时间相位调制和偏振调制。其技术方案为:包括光源、编码模块、第一反射单元和第二反射单元,其中,

5.所述光源用于提供待编码的信号光;

6.所述编码模块包括相位调制单元,且被设置成:将所述待编码的信号光分成第一信号光分量和第二信号光分量;借助所述相位调制单元对所述第一和第二信号光分量中的至少一个进行第一次相位调制;以及使所述第一和第二信号光分量发生干涉并输出一路或两路第一干涉光信号;

7.所述第一反射单元和所述第二反射单元具有彼此不同的光程,且设置成接收所述第一干涉光信号并将其反射回所述编码模块;

8.所述编码模块还设置成:接收反射光信号并将其分成第一反射光信号分量和第二反射光信号分量,其中,所述反射光信号分量具有时间相位编码信息;借助所述相位调制单元对所述第一和第二反射光信号分量中的至少一个进行第二次相位调制;以及使所述第一和第二反射光信号分量发生干涉并输出第二干涉光信号,其中,所述第二干涉光信号具有所述时间相位编码信息和偏振编码信息。

9.针对以上现有技术的不足,还需对现有的编码技术进行进一步地改进。

技术实现要素:

10.为了解决上述技术问题,提出了偏振相位双编码的,密钥生成率高的一种量子密钥分发系统的光源编码驱动系统。

11.为实现上述目的,本发明采取的技术方案如下:一种量子密钥分发的光源编码驱动系统,包括偏振编码驱动单元,相位编码驱动单元,衰减控制驱动单元和控制单元,所述控制单元采用fpga控制单元,所述偏振编码驱动单元,相位编码驱动单元,衰减控制驱动单元均分别与fpga控制单元连接,其中:

12.所述偏振编码驱动单元与偏振调制器连接,用于驱动与控制偏振调制器,为所述偏振调制器提供rf激励信号和偏置电压;

13.所述相位编码驱动单元与相位调制器连接,用于驱动与控制相位调制器,为偏振调制器提供rf激励信号;

14.所述衰减控制单元与衰减器连接,用于调节衰减器衰减值,为衰减器提供模拟量调节信号;

15.所述fpga控制单元通过调节偏振编码驱动单元rf的频率、幅度、延时,从而调节偏置电压的大小;所述fpga控制单元调节相位编码驱动单元rf的频率、幅度和延时;所述fpga控制单元通过调节衰减控制驱动单元输出的模拟量数值。

16.优选地,所述偏振编码驱动单元包括第一信号延迟电路,第二信号延迟电路,第一高速数模转换dac电路、第一信号放大电路、第二低速数模转换dac电路,其中:

17.所述第一信号延迟电路,第二信号延迟电路通过各自的输入端口分别与fpga控制单元连接,所述第一信号延迟电路的输出端口与第二信号延迟电路连接,所述第二信号延迟电路端口与所述第一高速数模转换dac电路连接;所述第一高速数模转换dac电路、第一信号放大电路和偏振调制器依次顺序连接;

18.所述第二低速数模转换dac电路输入端与fpga控制单元连接,输出端与偏振调制器。

19.优选地,所述fpga控制单元发送出rf_in脉冲信号依次经过第一信号延迟电路,第二信号延迟电路进行两次延迟处理后输入到第一高速数模转换dac电路中,第一高速数模转换dac电路根据接收的rf_in脉冲信号,随机输出水平、垂直、正45度、负45度偏振态的信号光对应的不同幅度的脉冲,然后输入到第一信号放大电路经放大后,rf_in信号输入到偏振调制器驱动偏振调制器;

20.所述第二低速数模转换dac电路接收fpga控制单元通过spi总线传输的设置参数,调节偏振调制器的偏置电压。

21.优选地,所述第一信号延迟电路和第二信号延迟电路均设置有延时芯片采用nb6l系列芯片,两片所述延时芯片串行级联,两片芯片分别通过延时配置口与fpga控制单元连接,通过fpga控制单元连接配置延时芯片的延时时间;

22.所述第一高速数模转换dac电路采用ad970x系列的dac芯片,fpga控制单元通过spi总线配置dac芯片;

23.优选地,所述第一信号放大电路包括opa系列的高速运放芯片,放大后的信号经电容隔直后连接到偏振调制器;

24.所述第二低速数模转换dac电路采用16位的ad57x1系列的dac芯片,fpga控制单元通过spi总线配置第二低速数模转换dac电路的dac芯片,并通过spi总线设置第二低速数模转换dac电路的输出模拟电压输出值,输出端口dc

‑

10/10连接到偏振调制器偏置电压输入端。

25.优选地,所述相位编码驱动单元包括第三延时电路,第四延时电路,第三高速数模转换dac电路和第三信号放大电路;

26.所述第三信号延迟电路,第四信号延迟电路通过各自的输入端口分别与fpga控制单元连接,所述第三信号延迟电路的输出端口与第四信号延迟电路连接,所述第四信号延迟电路端口与所述第三高速数模转换dac电路连接;所述第三高速数模转换dac电路、第二信号放大电路和相位调制器依次顺序连接。

27.优选地,所述fpga控制单元发送出rf_in脉冲信号依次经过第三信号延迟电路,第四信号延迟电路进行两次延迟处理后输入到第三高速数模转换dac电路中,第三高速数模转换dac电路根据接收的rf_in脉冲信号,随机输出0,π,π/2,3π/2四种相位的信号光对应的不同幅度的脉冲,然后输入到第三信号放大电路经放大后,rf_in信号输入到相位调制器驱动相位调制器。

28.优选地,所述衰减控制驱动单元包括第四低速数模转换dac电路和第四信号放大电路;

29.所述第四低速数模转换dac电路的输入端通过config端口以及数据data端口与所述控制单元连接,输出端与所述第四信号放大电路连接,所述第四信号放大电路又与所述可控衰减器连接;

30.优选地,所述fpga控制单元通过config端口配置所述第四低速数模转换器dac电路,所述数据data端口的数字量通过第四低速数模转换器dac电路转换为模拟信号,模拟信号经过第四信号放大电路控制衰减器的衰减值大小。

31.优选地,所述第四低速数模转换器dac电路包括数模转换芯片,数模转换芯片采用ad56x5系列芯片,所述fpga通过i2c总线配置数模转换芯片,i2c总线用于设定需要转换的数字值;

32.所述第四信号放大电路包括运算放大器和mems芯片,经过数模转换后的经过运算放大器同向放大后,mems驱动芯片改变光功率衰减值。

33.本发明的有益效果:

34.本发明采用相位偏振联合调制,码率是传统bb84协议的2倍;

35.本发明采用激光窄脉冲结合rf调制信号的方式,与传统的激光器连续发光相比,降低了激光器的能耗,提升了光源的使用寿命。

附图说明

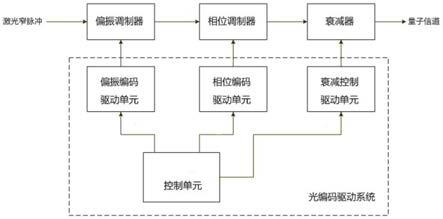

36.图1为本发明的整体原理结构框图;

37.图2为本发明中偏振编码驱动单元的硬件原理框图;

38.图3为本发明中rf_in与激光窄脉冲的相位关系示意图;

39.图4为本发明中相位编码驱动单元的硬件原理框图;

40.图5为本发明中衰减控制驱动单元的硬件原理框图;

41.图6为本发明中信号放大电路原理图。

具体实施方式

42.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合实施例对本发明进行进一步详细说明,但本发明要求保护的范围并不局限于下述具体实施例。

43.如图1

‑

6所示,一种量子密钥分发系统的光源编码驱动系统,包括偏振编码驱动单元,相位编码驱动单元,衰减控制驱动单元和控制单元,所述控制单元采用fpga控制单元,所述偏振编码驱动单元,相位编码驱动单元,衰减控制驱动单元均分别与fpga控制单元连接,其中:

44.所述偏振编码驱动单元与偏振调制器连接,用于驱动与控制偏振调制器,为所述

偏振调制器提供rf激励信号和偏置电压;

45.所述相位编码驱动单元与相位调制器连接,用于驱动与控制相位调制器,为偏振调制器提供rf激励信号;

46.所述衰减控制单元与衰减器连接,用于调节衰减器衰减值,为衰减器提供模拟量调节信号;

47.所述fpga控制单元通过调节偏振编码驱动单元rf(radio frequency,射频信号)的频率,使rf频率与激光窄脉冲频率相同、调节rf幅度,使之产生四种不同的幅度,对应四种量子偏振态;调节rf延时,使rf信号与激光窄脉冲对齐,同时调节偏振调制器偏置电压dc_in。dc_in的大小与偏振调制器的半波电压的关系,决定了偏振调制器的工作模式。

48.所述fpga控制单元调节衰减控制驱动单元输出的模拟量数值,模拟量的不同值对应着可控衰减器的衰减值,通过衰减,将光信号能量衰减到单光子态。

49.所述偏振编码驱动单元包括第一信号延迟电路,第二信号延迟电路,第一高速数模转换dac电路、第一信号放大电路、第二低速数模转换dac电路,其中:

50.所述第一信号延迟电路,第二信号延迟电路通过各自的输入端口分别与fpga控制单元连接,所述第一信号延迟电路的输出端口与第二信号延迟电路连接,所述第二信号延迟电路输出端口与所述第一高速数模转换dac电路连接;所述第一高速数模转换dac电路、第一信号放大电路和偏振调制器依次顺序连接;

51.所述第二低速数模转换dac电路输入端与fpga控制单元连接,输出端与偏振调制器连接。

52.所述fpga控制单元发送出rf_in脉冲信号依次经过第一信号延迟电路,第二信号延迟电路进行两次延迟处理后输入到第一高速数模转换dac电路中,第一高速数模转换dac电路根据接收的rf_in脉冲信号,随机输出水平、垂直、正45度、负45度偏振态的信号光对应的不同幅度的脉冲,然后输入到第一信号放大电路经放大后的rf_in信号输入到偏振调制器驱动偏振调制器,经过驱动后的偏振调制器产生水平、垂直、正45度和负45度四种偏振态的信号光。

53.所述第二低速数模转换dac电路接收fpga控制单元的设置参数,通过改变第二低速数模转换dac电路dc_in的电压值,调节偏振调制器的偏置电压,fpga控制单元与第二低速数模转换dac电路通过spi总线进行传输。

54.所述第一信号延迟电路和第二信号延迟电路均设置有延时芯片,延迟芯片采用nb6l系列芯片,两片延时芯片串行级联,两片延时芯片分别通过延时配置口与fpga控制单元连接,通过fpga控制单元来配置延时芯片的延时时间,从而调节rf_in与激光窄脉冲的相位关系,每片延时芯片可提供15ns内的延时,两片级联最大可达到30ns的延时。

55.第一信号延时电路、第二信号延时电路的作用是调节rf_in脉冲与激光窄脉冲对齐,通过偏振调制器将rf_in射频信号调制到激光上,rf_in与激光窄脉冲的相位如图2所示,fpga控制单元通过第一延时#1配置接口控制第一信号延时电路,第二延时#2配置接口控制第二信号延时电路。

56.所述第一高速数模转换dac电路采用ad970x系列dac芯片,fpga控制单元通过spi总线配置第一高速数模转换dac电路。

57.所述第一信号放大电路包括高速运放芯片,经第一信号放大电路放大后的信号经

电容隔直后输入到偏振调制器。

58.所述第二低速数模转换dac电路采用ad57x1系列dac芯片,fpga控制单元通过spi总线配置16位第二低速数模转换dac电路的dac芯片,并通过spi总线设置dac芯片的输出模拟电压输出值,输出端口dc

‑

10/10连接到偏振调制器偏置电压输入端。

59.所述相位编码驱动单元包括第三延时电路,第四延时电路,第三高速数模转换dac电路和第三信号放大电路;

60.所述第三信号延迟电路,第四信号延迟电路通过各自的输入端口分别与fpga控制单元连接,所述第三信号延迟电路的输出端口与第四信号延迟电路连接,所述第四信号延迟电路端口与所述第三高速数模转换dac电路连接;所述第三高速数模转换dac电路、第二信号放大电路和相位调制器依次顺序连接。

61.所述fpga控制单元发送出rf_in脉冲信号依次经过第三信号延迟电路,第四信号延迟电路进行两次延迟处理后输入到第三高速数模转换dac电路中,第三高速数模转换dac电路根据接收的rf_in脉冲信号,随机输出0,π,π/2,3π/2四种相位的信号光对应的不同幅度的脉冲,然后输入到第三信号放大电路经放大后,rf_in信号输入到相位调制器驱动相位调制器,相位调制器根据rf_in产生0,π,π/2,3π/2四种不同相位的调制信号光。

62.所述衰减控制驱动单元包括第四低速数模转换dac电路和第四信号放大电路;

63.所述第四低速数模转换dac电路的输入端通过config端口以及数据data端口与所述控制单元连接,输出端与所述第四信号放大电路连接,所述第四信号放大电路又与所述可控衰减器连接;

64.所述fpga控制单元通过config端口配置所述第四低速数模转换器dac电路,所述数据data端口的数字量通过第四低速数模转换器dac电路转换为模拟信号,模拟信号经过第四信号放大电路控制衰减器的衰减值大小,衰减器将信号光的能量衰减到单光子态。

65.所述第四低速数模转换器dac电路包括数模转换芯片,数模转换芯片的型号采用ad56x5系列芯片,所述fpga通过i2c总线配置数模转换芯片,i2c总线用于设定需要转换的数字值。

66.所述第四信号放大电路包括运算放大器opa和mems驱动芯片mems,经过数模转换后的经过运算放大器opa同向放大后,mems驱动芯片改变光功率衰减值。运算放大器放大倍数等于通过调整电阻值可以改变运算放大器opa的放大倍数。

67.如图1所示,经过本系统的作用,激光窄脉冲首先经过偏振调制器,将光脉冲调制成偏振态如水平、垂直、正45度或负45度的偏振信号光,然后该偏振信号光再经过相位调制器,将偏振信号光再调制上0、π、π/2或3π/2的相位信息,然后经过衰减器将光信号能量衰减成单光子态,通过量子信道发送出去。

68.根据上述说明书的揭示和教导,本发明所属领域的技术人员还可以对上述实施方式进行变更和修改。因此,本发明并不局限于上面揭示和描述的具体实施方式,对发明的一些修改和变更也应当落入本发明的权利要求的保护范围内。此外,尽管本说明书中使用了一些特定的术语,但这些术语只是为了方便说明,并不对发明构成任何限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1