一种应用于物理层的占空比控制方法、装置、电路及设备与流程

1.本发明实施例涉及集成电路设计技术领域,尤其涉及一种应用于物理层的占空比控制方法、装置、电路及设备。

背景技术:

2.为了满足物联网或移动设备降低功耗的需求,通常会采用工作和空闲占空比(duty cycle)的调制模式以避免这类设备长时间处于工作状态而造成功耗的浪费。

3.当前对于占空比进行控制的方案,通常采用软件程序或者协议层面进行实施,具体来说,软件控制方案实施简单但是延迟较大,协议层面也存在这类问题,因此,通过软件程序或者协议层面进行占空比控制的方案目前只能够对设备中的整体通信系统以及系统内较大的组件模块间的占空比进行控制,无法达到更加精细的调节控制从而仍会造成功耗的浪费。

技术实现要素:

4.有鉴于此,本发明实施例期望提供一种应用于物理层的占空比控制方法、装置、电路及设备;通过在物理层实现对占空比的精细控制,降低了功耗。

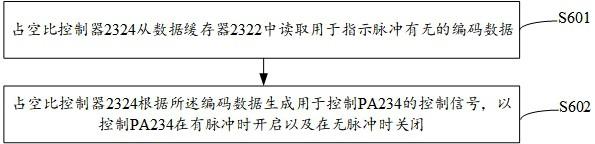

5.本发明实施例的技术方案是这样实现的:第一方面,本发明实施例提供了一种应用于物理层的占空比控制方法,所述方法包括:占空比控制器从数据缓存器中读取用于指示脉冲有无的编码数据;所述占空比控制器根据所述编码数据生成用于控制功率混频器pa的控制信号,以控制所述pa在有脉冲时开启以及在无脉冲时关闭。

6.第二方面,本发明实施例提供了一种占空比控制器,所述占空比控制器包括:读取部分和生成部分;其中,所述读取部分,经配置为从数据缓存器中读取用于指示脉冲有无的编码数据;所述生成部分,经配置为根据所述编码数据生成用于控制功率混频器pa的控制信号,以控制所述pa在有脉冲时开启以及在无脉冲时关闭。

7.第三方面,本发明实施例提供了一种应用于物理层的占空比控制电路,所述电路包括:数据缓存器、功率混频器以及第二方面所述的占空比控制器。

8.第四方面,本发明实施例提供了一种发射设备,所述发射设备的发射前端包括第三方面所述的应用于物理层的占空比控制电路。

9.本发明实施例提供了一种应用于物理层的占空比控制方法、装置、电路及设备;利用占空比控制器根据编码数据是否有脉冲来控制功率混频器pa的开启和关闭,从而实现了数据帧内部的占空比控制,相较于目前利用软件程序以及协议层面进行占空比控制的方案,在物理层提高了占空比控制的精细度,进一步地降低了功耗。

附图说明

10.图1为本发明实施例提供的一种示例性的网络环境示意图。

11.图2为本发明实施例提供的一种示例性的通信系统架构示意图。

12.图3为本发明实施例提供的一种发射前端的架构示意图。

13.图4为本发明实施例提供的一种uwb脉冲射频信号示意图。

14.图5为本发明实施例提供的另一种发射前端的架构示意图。

15.图6为本发明实施例提供的一种应用于物理层的占空比控制方法流程示意图。

16.图7为本发明实施例提供的一种生成信号的时序图。

17.图8为本发明实施例提供的占空比控制器的组成示意图。

具体实施方式

18.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。

19.参见图1,其示出了能够适用于本发明实施例所阐述技术方案的网络环境100示意图,作为解说性示例而非限定,以无线通信设备102为例,无线通信设备102能够在该网络环境100内与处于该无线通信设备102近程的其他无线通信设备进行无线通信,其他无线通信设备比如打印机104、个人数字助理(pda,personal digital assistant)106、照相机108和接入点110,此外,还可以通过接入点110与通信耦合至接入点110的扬声器系统112和无线网络114进行无线通信。网络环境100中的所有无线通信设备均可利用任何适当的无线标准诸如802.11x或超宽带(uwb,ultra wide

‑

band)进行无线通信。

20.需要说明的是,在图1所示的网络环境100中,术语“无线通信设备”也可以被本领域技术人员称之为移动站(ms)、订户站、移动单元、订户单元、无线单元、远程单元、移动设备、无线设备、远程设备、移动订户站、接入终端(at,access termination)、移动终端、无线终端、远程终端、手持机、终端、用户代理、移动客户端、客户端、或某个其他合适的术语;并且,无线通信设备在某些示例中不一定需要具有移动能力,也可以是驻定的;此外,无线通信设备可包括大小、形状被设定成并且被布置成有助于实施无线通信的数个硬件结构组件,此类组件可包括彼此电耦合的天线、天线阵列、射频(rf,radio frequency)链、放大器、一个或多个处理器等等。另外,在一些非限定性示例中,除了以上所述的打印机、pda、照相机、接入点、扬声器系统和无线网络以外,无线通信设备的其他非限定性示例还包括移动设备、蜂窝(蜂窝小区)电话、智能电话、会话发起协议(sip,session initiation protocol)电话、膝上型设备、个人计算机(pc,personal computer)、笔记本、上网本、智能本、平板设备、以及广泛多样的嵌入式系统,例如,对应于“物联网”(iot)。附加地,无线通信设备可以是汽车或其他运输车辆、遥感器或致动器、机器人或机器人设备、卫星无线电、全球定位系统(gps,global positioning system)设备、对象跟踪设备、无人机、多轴飞行器、四轴飞行器、遥控设备、消费者和/或可穿戴设备(诸如眼镜)、可穿戴相机、虚拟现实设备、智能手表、健康或健身跟踪器、数字音频播放器(例如,mp3播放器)、相机、游戏控制台等。附加地,无线通信设备还可以是数字家用或智能家用设备,诸如家用音频、视频和/或多媒体设备、电器、自动售货机、智能照明设备、家用安全系统、智能仪表等。附加地,无线通信设备也可以是智能能源设备,安全设备,太阳能电池板或太阳能电池阵,控制电力、照明、水等的市政基础设

施设备(例如,智能电网);工业自动化和企业设备;物流控制器;农业装备;军事防御装备、车辆、飞机、船和武器等。

21.针对上述无线通信设备102,其能够在网络环境100中与其他无线通信设备任意一个实现双向的无线通信以形成通信系统200,如图2所示的通信系统200架构示意图,该通信系统200可以包括发射机202(比如图1所示的网络环境100中的无线通信设备102)和接收机206(比如图1所示的网络环境100中的其他无线通信设备的任一个),其中,发射机202可以包括一个或多个发射天线204(例如,n1个发射天线),并且接收机206包括一个或多个接收天线208(例如,n2个接收天线)。发射机202通过发射天线204发射uwb脉冲以传送数据流,数据流经过无线信道210到达接收机206的每个接收天线208,接收机206可以接收来自每个接收天线208信号对数据流进行重构。

22.对于图2中所示的发射机202来说,每个发射天线204均对应于一发射前端230。每个发射前端230的硬件架构可以参见图3所示,包括:arm处理器231、发射端数字控制器232、数模转换器(dac,digital

‑

to

‑

analog converter)233和功率混频器234;具体来说,发射端数字控制器232通过spi接口与arm处理器231相连以获取待发送的原始数据。该原始数据经过发射端数字控制器232中的编码器2321完成编码之后存入数据缓存器2322,接着dac数据流生成器2323基于完成编码的数据产生与dac 233相适配的数据流以使得dac 233根据该完成编码的数据所产生的数据流转换为对应的基带模拟信号并传输至功率混频器pa 234;最后,功率混频器234将通过数字控制振荡器(dco)和射频分频器(rf divider)所提供的本振信号lo与基带模拟信号进行混频生成uwb脉冲射频信号,最后经由发射天线204向无线信道210发射。

23.基于图3所示的发射前端230的硬件架构,以uwb脉冲射频信号为例,如图4所示,一帧uwb数据包含前导码preamble、帧首定界符(sfd,start of frame delimiter)、物理层帧头(phr,physical header)和物理层服务数据单元(psdu,phy service data unit);并且在一帧uwb数据内,并不是一直有脉冲发出,根据协议规定,脉冲之间会存在一段时间的零电平。基于此,编码器2321在对待发送的原始数据进行编码时,通常会基于原始数据形成两个编码数据部分,其中一个部分(以b0为标识)表示有无脉冲,另一部分(以b1为标识)表示脉冲的极性;这两个编码数据部分各自通过1bit来进行表示,具体表示如下表所示:表1也就是说,当b0为零的情况下,就可以表示脉冲之间的零点平,从而就完成将原始数据通过编码以进行表示。编码完成后,上述两个编码数据部分将缓存于数据缓存器2322中,并相应地经过dac数据流生成器2323与dac 233以生成基带模拟信号,进而利用pa 234生成uwb脉冲射频信号。

24.对于图4中所示的零点平持续时段内,可以把pa 234进行关闭,从而能够达到节省功耗的目的。软件程序以及协议层面目前仅能够对数据帧之间零点平实现占空比控制,无

法实现数据帧内部的占空比控制,也就是说,目前相关方案中无法利用软件程序以及协议层面实现更为精细的占空比控制。

25.基于以上之阐述,本发明实施例期望通过在物理层实现更为精细的占空比控制,特别是能够针对数据帧内部实现占空比控制。基于此,结合图3所示的发射前端230的硬件架构,参见图5,本发明实施例在发射端数字控制器232中额外设置一占空比控制器2324,如图5所示,该占空比控制器2324分别与数据缓存器2322以及pa 234相连,应用于图5所示的占空比控制器2324,本发明实施例提供了一种应用于物理层的占空比控制方法,参见图6,该方法可以包括:s601:占空比控制器2324从数据缓存器2322中读取用于指示脉冲有无的编码数据,如上述以b0为标识的编码数据部分;s602:占空比控制器2324根据所述编码数据生成用于控制pa 234的控制信号,以控制pa 234在有脉冲时开启以及在无脉冲时关闭。

26.通过上述图6所示的技术方案,利用占空比控制器2324根据编码数据是否有脉冲来控制pa 234的开启和关闭,从而实现了数据帧内部的占空比控制,相较于目前利用软件程序以及协议层面进行占空比控制的方案,在物理层提高了占空比控制的精细度,进一步地降低了功耗。

27.对于图6所示的技术方案,在一些可能的实现方式中,所述占空比控制器2324根据所述编码数据生成用于控制pa 234的控制信号,具体包括:占空比控制器2324根据所述编码数据生成数据有效信号data_valid;其中,当所述编码数据指示有脉冲时,数据有效信号data_valid为高电平;当所述编码数据指示无脉冲时,数据有效信号data_valid为低电平。

28.对于上述实现方式,需要说明的是,在利用数据有效信号data_valid控制pa 234的开启和关闭过程中,并没有考虑到pa 234的启动时间,也就是说,若pa 234的关闭和启动的时间间隔不足,会由于pa不稳定导致发射脉冲的异常。详细来说,为了避免发生由于pa 234的关闭和启动的时间间隔不足而发生pa不稳定进而导致发射脉冲的异常情况,在执行s602所述的生成用于控制pa 234的控制信号的过程中,考虑pa 234的启动时间,在一些可能的实现方式中,本发明实施例在生成数据有效信号data_valid之后,图6所示的方法还可以包括:占空比控制器2324读取启动延时tdelay寄存器中存储的pa 234的启动时长值tdelay,并将数据有效信号data_valid按照tdelay延迟后获得数据缓存器2321的控制信号data_valid_delay。

29.对于上述实现方式,在具体实施过程中,arm处理器231可以通过spi接口配置启动延时tdelay寄存器,其中所存储的tdelay为pa 234的启动时长,arm处理器231可以根据pa 234的模拟电路的特性,将tdelay配置为不同的值。数据缓存器2321可以根据其控制信号data_valid_delay将从编码器231所获得的编码数据按照tdelay进行延迟,以b0和b1为例,数据缓存器2321将这两个编码数据均延迟tdelay,从而相应得到b0 delay和b1 delay。

30.在一些可能的实现方式中,图6所示的方法还可以包括:占空比控制器2324根据数据有效信号data_valid,在data_valid的高电平的第一个时钟周期的产生起始脉冲信号valid_start;在data_valid_delay高电平的最后一个时

钟周期产生延迟停止脉冲信号valid_delay_stop。

31.占空比控制器2324通过valid_start触发起始计数器start_counter开始计数;并通过延迟停止脉冲信号valid_delay_stop触发停止计数器stop_counter计数器开始计数;当stop_counter计数器的值与start_counter计数器的值相等且大于0时,占空比控制器2324产生重置reset脉冲信号,并且在reset脉冲信号的下降沿,将start_counter和stop_counter清零;当valid_start为高时,占空比控制器2324将pa使能信号pa_en拉高,从而能够控制pa 234启动;在reset脉冲信号的下降沿,占空比控制器2324将pa_en拉低,从而能够控制pa 234关闭。

32.由于dac和dac数据流生成器同样也存在硬件固定延迟值dac delay,所以为了考虑这部分的延迟,在一些示例中,在获取到pa_en后,所述方法还包括:占空比控制器2324将pa_en延迟dac delay个时钟周期以得到pa使能延迟信号pa_en_delay,需要说明的是,pa_en_delay恰好可以和dac输出的模拟信号在时间上对齐,从而更加准确控制pa 234的开关。

33.针对上述实现方式及其示例,参见图7,其示出了根据b0生成相应信号的时序图,在图7中,以tdelay=3,即b0 delay被延迟3个时钟周期为例,从而该部分延迟保证了pa 234有足够的启动时间。从图7中可以看出,b0=1时,data_valid为高,当b0=0时,data_valid为低。data_valid的上升沿与valid_start的上升沿一致,并且与pa_en的上升沿一致。此外,data_valid_delay的下降沿与valid_delay_stop的下降沿一致,并且还与reset信号和pa_en 的下降沿一致。根据时序图中的b1_delay信号,当与b0_delay信号同时延迟dac delay之后,就能够形成模拟脉冲信号以及对应的极性,如图7中最后一行所示信号。此外,还需要注意的是,如图7中的箭头所示,b0短暂为0的时候,比如仅维持1个时钟周期的情况下,由于start_counter和stop_counter的作用,使得pa_en不会短暂拉低,而是维持到下一个b0为0,从而避免了由于频繁关开pa 234而导致启动时间不够。

34.基于前述技术方案相同的发明构思,参见图8,其示出了本发明实施例提供的一种占空比控制器2324,所述占空比控制器2324包括:读取部分801和生成部分802;其中,所述读取部分801,经配置为从数据缓存器中读取用于指示脉冲有无的编码数据;所述生成部分802,经配置为根据所述编码数据生成用于控制功率混频器pa的控制信号,以控制所述pa在有脉冲时开启以及在无脉冲时关闭。

35.在上述方案中,所述生成部分802,经配置为:根据所述编码数据生成数据有效信号data_valid;其中,当所述编码数据指示有脉冲时,所述data_valid为高电平;当所述编码数据指示无脉冲时,所述data_valid为低电平。

36.在上述方案中,所述生成部分802,还经配置为:读取启动延时寄存器中存储的所述pa的启动时长值tdelay,并将所述data_valid按照所述tdelay延迟后获得所述数据缓存器的控制信号data_valid_delay,以使得所述数据缓存器根据所述data_valid_delay将从编码器所获得的编码数据按照所述tdelay进行延迟。

37.在上述方案中,所述生成部分802,还经配置为:根据所述data_valid,在所述data_valid的高电平的第一个时钟周期的产生起始脉冲信号valid_start;在所述data_valid_delay高电平的最后一个时钟周期产生延迟停

止脉冲信号valid_delay_stop;以及,通过所述valid_start触发起始计数器start_counter开始计数;并通过所述valid_delay_stop触发停止计数器stop_counter计数器开始计数;以及,当所述stop_counter的值与所述start_counter的值相等且大于0时,产生重置reset脉冲信号,并且在所述reset脉冲信号的下降沿,将所述start_counter和所述stop_counter清零;以及,当所述valid_start为高时,将pa使能信号pa_en拉高,以控制所述pa启动;在所述reset脉冲信号的下降沿,所述占空比控制器2324将所述pa_en拉低,以控制所述pa关闭。

38.在上述方案中,所述生成部分802,还经配置为:将所述pa_en按照数模转换器dac和dac数据流生成器的硬件固定延迟值进行延迟以得到pa使能延迟信号pa_en_delay。

39.可以理解地,在本实施例中,“部分”可以是部分电路、部分处理器,当然也可以是单元,还可以是模块也可以是非模块化的。

40.另外,在本实施例中的各组成部分可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。上述集成的单元可以采用硬件的形式实现。对于硬件实现,上述部分可以实现在一个或多个专用集成电路(application specific integrated circuits,asic)、数字信号处理器(digital signal processing,dsp)、数字信号处理设备(dsp device,dspd)、可编程逻辑设备(programmable logic device,pld)、现场可编程门阵列(field

‑

programmable gate array,fpga)、通用处理器、控制器、微控制器、微处理器、用于执行本申请所述功能的其它电子单元或其组合中。

41.可以理解地,上述占空比控制器2324的示例性技术方案,与前述应用于物理层的占空比控制方法的技术方案属于同一构思,因此,上述对于占空比控制器2324的技术方案未详细描述的细节内容,均可以参见前述应用于物理层的占空比控制方法的技术方案的描述。本发明实施例对此不做赘述。

42.需要说明的是:本发明实施例所记载的技术方案之间,在不冲突的情况下,可以任意组合。

43.以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1