一种VDES-A型机系统的制作方法

一种vdes

‑

a型机系统

技术领域

1.本发明涉及通信数据技术领域,具体来说,涉及一种vdes

‑

a型机系统。

背景技术:

2.船舶自动识别系统(automatic identification system,ais)是工作在甚高频(very high frequency,vhf)海上频段的船舶和岸基广播系统,是集现代通信、网络技术以及信息技术于一体的助航系统或海上安全系统。ais采用sotdma多址通信,将航行时的信息传送给周边船舶和岸上基站设施,以求在最大程度上降低船舶之间发生碰撞的概率,确保船舶海上航行的安全。随着ais的快速推广,ais的局限性逐渐显现:一方面,航标、水文以及气象等扩展应用的不断增加,ais的数据交换能力严重不足,在一些繁忙区域出现了很高的数据链路载荷;另一方面,由于早期的ais还是以陆基基站的vhf为主,覆盖范围只有30海里左右,无法实现全球性的覆盖。为了提高数据处理能力,扩大通信传输距离,因此,2015年11月itu世界无线电通信大会(wrc

‑

15)审议决定引入甚高频数据交换系统(vhf data exchange system,vdes)来进一步推动水上无线电数字通信产业的发展。vdes是针对水上移动业务领域中的船舶自动识别系统(automatic identification system,ais)发展起来的新一代数字通信系统。

3.vdes是对ais的一次升级,并使用卫星通信作为远距离的信息传输方式,其主要目的是在实现全球范围内海事vhf移动波段通信的同时,为船舶用户提供更强的数据交换能力,并拓宽数据应用业务。vdes整合了ais、asm数据交换(asm exchange)、电子导航(e

‑

navigation)以及增强海事通讯(enhanced maritime communication,emc)和全球海上遇险与安全系统(global maritime distress and safety system,gmdss)现代化(modernized gmdss)等既有功能。简言之,vdes将集成ais、特殊应用消息(asm)以及宽带甚高频数据交换(vhf data exchange,vde)三项功能。

4.在vdes架构下,ais保持其最初的设计目的不变,只用于船舶身份识别、位置报告、航行数据、搜寻以及救援;asm是一种实时可靠的信息接收机制,主要是除去与航行安全关系最为紧密的船舶位置和航行状态信息之外的其它非导航安全信息,包括水文和气象等信息;vde是vdes的核心功能,是vdes实现高带宽数据通信的基础,其又分为陆基vde及天基(卫星)vde两部分

5.因此,亟需一种vdes

‑

a型机系统。

6.针对相关技术中的问题,目前尚未提出有效的解决方案。

技术实现要素:

7.针对相关技术中的问题,本发明提出一种vdes

‑

a型机系统,以克服现有相关技术所存在的上述技术问题。

8.本发明的技术方案是这样实现的:

9.一种vdes

‑

a型机系统,包括:

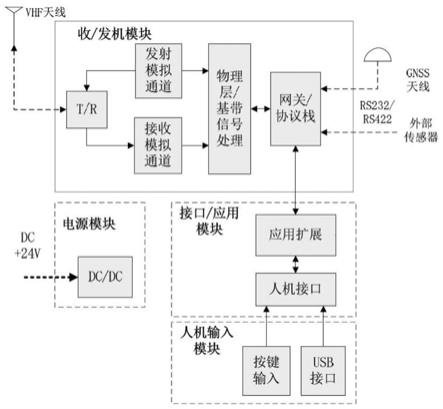

10.收发机模块、接口模块、人机输入模块和电源模块,所述人机输入模块与所述接口模块电性连接,所述接口模块与所述收发机模块连接,其中;

11.所述收发机模块,用于实现报文的封装/解析、cstdma/sotdma组网协议和物理层调制解调,且所述收发机模块包括t/r开关、发射模拟通道、接收模拟通道、基带信号处理和网关/协议栈;

12.所述接口模块,用于实现人机输入/输出接口处理、电子海图显示、和用户扩展应用功能;

13.所述人机输入模块,用于实现用户的按键和usb接口输入功能;

14.所述电源模块,用于将24v直流电源转换成各个模块所需要的电压值,为设备内部各个元器件供电。

15.进一步的,所述发射模拟通道,包括dac,所述基带信号处理的输出端连接所述dac的输入端,且所述dac的输出端连接低通滤波器的输入端,所述低通滤波器的输出端连接rf功率放大的输入端,所述rf功率放大的输出端连接rf信号滤波的输入端,所述rf信号滤波的输出端连接t/r开关的输入端。

16.进一步的,所述接收模拟通道包括射频agc和基带agc,其中,所述射频agc的输入端连接所述t/r开关的输出端,所述射频agc的输出端连接功分器的输入端,所述功分器的输出端连接所述基带agc的输入端,所述基带agc的输出端连接所述基带信号处理的输入端。

17.进一步的,所述物理层调制解调包括:

18.所述射频agc的输出端连接功分器的输入端,且所述功分器的输出端分别包括vde正交解调、ais正交解调和asm正交解调。

19.进一步的,所述ais正交解调处理流程,包括以下步骤:

20.fpga接收从数据链路层发送来的数据,对发送数据进行基带帧组帧,其中包括crc校验生成,数据连续六个1插零操作;

21.对基带帧进行物理帧组帧,主要操作有增加训练序列、起始缓冲区以及结束缓冲区;

22.二进制到nrzi码转换,得到物理层比特流数据;

23.nzri比特流进行高斯滤波成形,得到高斯形状基带信号;

24.高斯基带信号进行连续积分运算,控制复数正弦信号的载波频率,等效于进行fm调制;

25.复数正弦信号的sin与cos分量分别进行数字上变频,直接合成到rf射频信号。

26.进一步的,asm正交解调处理流程,包括以下步骤:

27.fpga接收从数据链路层发送来的数据,对发送数据进行asm基带帧组帧,其中包括crc校验生成;

28.对asm物理层进行fec纠错编码;

29.对fec编码后的asm基带帧进行物理帧组帧,主要操作有插入训练序列、起始缓冲区以及结束缓冲区等;

30.对asm物理帧进行π/4

‑

qpsk数字调制;

31.将数字调整的i/q符号经过平方根升余弦滤波器,进行频谱成形,得到基带信号;

32.基带信号的sin与cos分量分别进行数字上变频,最后直接合成到asm rf射频信号。至此,asm调制器工作完成。

33.进一步的,所述vde正交解调处理流程,包括以下步骤:

34.fpga接收从数据链路层发送来的数据,对发送数据进行vde基带帧组帧,其中包括crc校验生成;

35.对vde基带帧进行turbo fec纠错编码;

36.对fec编码后的vde基带帧进行物理帧组帧,主要操作有插入训练序列、起始缓冲区以及结束缓冲区等;

37.根据vde随路的调制信息,对vde物理帧进行π/4

‑

qpsk、8psk或者16qam的数字调制;

38.将数字调制的i/q符号进行1:32的串并转换;

39.串并转换的32点数据按照每32点一组,进行32点反傅里叶变换;

40.将ifft输出的并行数据分别与多相滤波器进行成形滤波操作,使得每个子载波具有平方根升余弦滤波器形状;

41.成形之后的基带信号,再经过duc进行数字上变频,直接合成vde rf信号。

42.本发明的有益效果:

43.本发明vdes

‑

a型机系统,集成收发机模块和接口模块以及人机输入模块和电源模块,其实现报文的封装/解析、cstdma/sotdma组网协议和物理层调制解调,实现人机输入/输出接口处理、电子海图显示、和用户扩展应用功能;用于实现用户的按键和usb接口输入功能;不仅结合数据交换场景的具体需求,得到的vdes分组数据网关能够高效灵活地实现海事站台之间多种数据格式交换、数据压缩、数据加密以及与异构网络互通等vde功能;而且该系统对vdes协议中的表现层进行了扩展,并在引入发射模拟通道和接收模拟通道以及基带信号处理和网关/协议栈,实现发送/接收的信息清晰理解,数据交互过程更加高效、有效和简洁。

附图说明

44.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

45.图1是根据本发明实施例的一种vdes

‑

a型机系统的原理框图一;

46.图2是根据本发明实施例的一种vdes

‑

a型机系统的原理框图二;

47.图3是根据本发明实施例的一种vdes

‑

a型机系统的原理框图三;

48.图4是根据本发明实施例的一种vdes

‑

a型机系统的原理框图四。

49.图中:

50.1、收发机模块;2、接口模块;3、人机输入模块;4、电源模块。

具体实施方式

51.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完

整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员所获得的所有其他实施例,都属于本发明保护的范围。

52.根据本发明的实施例,提供了一种vdes

‑

a型机系统。

53.如图1

‑

图2所示,根据本发明实施例的vdes

‑

a型机系统,包括:

54.收发机模块(1)、接口模块(2)、人机输入模块(3)和电源模块(4);其中,

55.所述收发机模块(1),包括t/r开关、发射模拟通道、接收模拟通道、基带信号处理和网关/协议栈,用于实现报文的封装/解析、cstdma/sotdma组网协议和物理层调制解调;

56.所述接口模块(2),用于实现人机输入/输出接口处理、电子海图显示、以及用户扩展应用等功能。该模块主要由运行在arm处理器上的linux操作系统以及嵌入式应用软件来实现;

57.所述人机输入模块(3),用于实现用户的按键和usb接口输入功能;

58.所述电源模块(4),用于将船上提供的24v直流电源转换成各个模块所需要的电压值,为vdes

‑

a型机设备内部各个元器件供电。

59.借助于上述方案,集成收发机模块和接口模块以及人机输入模块和电源模块,其实现报文的封装/解析、cstdma/sotdma组网协议和物理层调制解调,实现人机输入/输出接口处理、电子海图显示、和用户扩展应用功能;用于实现用户的按键和usb接口输入功能;不仅结合数据交换场景的具体需求,得到的vdes分组数据网关能够高效灵活地实现海事站台之间多种数据格式交换、数据压缩、数据加密以及与异构网络互通等vde功能;而且该系统对vdes协议中的表现层进行了扩展,并在引入发射模拟通道和接收模拟通道以及基带信号处理和网关/协议栈,实现发送/接收的信息清晰理解,数据交互过程更加高效、有效和简洁。

60.此外,如图3所示,发射模拟通道,包括:

61.1)直接rf合成:发射rf信号的合成采用高速dac实现,dac采样速率为800mhz,可以直接产生高达320mhz的射频信号。dac后面接一个镜像抑制低通滤波器,即可完美实现直接rf信号合成,这样就避免了中频信号再到射频信号的频谱搬移,降低了电路体积。

62.2)rf功率放大:rf功率放大采用级联的两级放大方案,第一级放大器把输入在

‑

4dbm的vhf信号放大到17dbm左右;末级功放采用1db压缩点在35dbm,增益18db的功放,把信号推到所需要的发射功率;在两级放大之间用衰减器来进行阻抗匹配的调整。

63.3)功率放大后rf信号滤波:功率放大后的rf信号,通常谐波和杂散不能满足发射机指标,因此需要用带通滤波器进行滤波;

64.4)t/r开关:t/r开关实现收/发信号时分复用功能,收/发切换主要由mac层控制。

65.其中,发射通道技术指标:频率稳定度:1

×

10

‑

6;发射功率:2w;谐波抑制:≥60db;杂散抑制:≥60db;收/发转换时间:≤100ms;具有负载开路、短路和过热保护。

66.另外,对于上述dac来说,因为vdes的射频频率在160mhz左右,属于较低的频率。所以发射机方案中,用d/a直接把数字的rf信号转换成模拟rf信号。因此,无需额外的频率上变处理,降低了发射机复杂度。相对于模拟变频方案来说,数字rf信号的产生策略对信号的失真最小,从而也带来了性能指标的提升。d/a转换器仍然沿用第一版的器件,也即采用ad9785芯片。ad9785分别是双通道、12位、高动态范围数模转换器(dac),提供800msps采样

速率,可以产生最高达奈奎斯特频率的多载波,也即500mhz。这些器件具有针对直接变频传输应用进行优化的特性,包括复合数字调制以及增益与失调补偿。串行外设接口允许对许多内部参数进行编程和回读。

67.其中,第一级放大器选型:第一级放大器选qorvo的tqp3m9036,该放大器可以作为低噪声放大器使用,具有线性度高,内部集成了阻抗匹配等优点,该器件主要特性如下:宽带工作范围:100mhz~2000mhz宽带工作范围;低噪声系数:900mhz时噪声系数为0.45db;高增益:在900mhz时增益为19.8db;高线性度:输出ip3为+36dbm;集成片内阻抗匹配:输入/输出均为50ω;无条件稳定;集成信号输出关闭控制;电源简单:3~5v正电压供电。

68.其中,末级放大器选型:末级放大器选用rfpa3800芯片,该芯片主要特性如下:宽带工作范围:150mhz~960mhz;p1db输出功率:5w;高线性度:oip3>48dbm高效率;低噪声系数:nf=3.2db(945mhz);宽电压范围:5v~7v。

69.其中,放大器输出分段开关:放大器输出分段开关选择pe42820芯片,该芯片为高功率反射式单刀双掷开关,主要特性如下:高功率范围:45dbm@850mhz;高线性度:85dbm iip3@850mhz;低插入损耗:0.25db@850mhz;宽电源输入范围:2.3v~5.5v;控制逻辑电压:+1.8v;esd性能:在每个管脚都有1.5kvhbm。

70.其中,t/r开关:射频开关选用hswa2

‑

63dr+单刀双掷rf开关,其主要技术指标如下:频率范围:100mhz~6ghz;隔离度:69db(在1ghz时);插损:0.95db(在1ghz时)。输入ip3:65dbm(典型值)。切换时间:300ns(典型值)。

71.另外,如图4所示,接收模拟通道,考虑到接收机饱和以及邻道干扰抑制,把agc分成两级级联,两个agc分别设计在正交下变频前后。包括:

72.第一级为射频agc:主要用于通带信号很强时,避免接收机饱和。拟选用hmc629a,该器件最大衰减为45db,可以大大减小接收机饱和发生。

73.第二阶为基带agc:在基带低通滤波器后使用,主要用于对邻道干扰抑制。拟选用adrf6520,该器件最大增益为53db。

74.另外,fpga是基带信号处理、调制解调、协议栈软件交互、信道控制、外围通信等核心处理器件。因此,fpga器件的逻辑资源、实时处理速度、外围接口等指标是系统稳定运行的重要因素。

75.此外,对于上述电源模块(4)来说,其输入为24vdc,经过一次电源到二次电源的转换,为系统提供+12v的电源,由各个模块电路进一步稳压实现到三次电源电压的转换。具体的:

76.功放电路:选用dc/dc电路供电,功放为突发rf信号发送(占空比10%计算),未发送时功放为静默状态,在电路设计中采用mos管控制功放电源供电,同时使用大电容储能,满足电路的负载特性要求。

77.接收通道供电:选用低噪声的ldo电源,用于模拟前端供电,降低引入信号的噪声,为了兼顾ldo电源效率,选择低压差adi公司的器件。

78.基带数字电路供电:选用dc/dc电路供电,兼顾电源面积和转换效率。

79.电源供电:dc 24v。电源波动范围:

‑

20%~+30%。

80.电源异常保护:欠压保护:额定值的

‑

25%,持续工作30s;过压保护:额定值的+50%,持续工作30s。

81.工作温度:

‑

15℃~55℃;湿度要求:湿热温度为40℃

±

3℃,相对湿度为93

±

2%,持续时间10小时,设备应能正常工作。

82.防水等级:ip67。防潮、防盐雾。

83.此外,对于上述报文的封装/解析、cstdma/sotdma组网协议和物理层调制解调来说,具体的:

84.物理层由fpga逻辑来实现,物理层主要完成vhf频段多信道数据半双工收发功能,支持同时接收最多6路信号的功能。fpga逻辑主要功能需求如下:具备在vhf频段实现vde1

‑

a\vde1

‑

b\ais1\ais2\asm1\asm2信道数据半双工收发功能;具备支持同时接收最多6路信号的功能;支持gmsk

‑

fm、π/4qpsk、8psk、16qam等多种调制体制,并具备自适应解码解调技术向发射调制、返向接收解调能力;具有接收1pps信号的能力。

85.其中,ais调制器的逻辑处理流程说明如下:

86.fpga接收从数据链路层发送来的数据,对发送数据进行基带帧组帧,其中包括crc校验生成,数据连续六个1插零操作;

87.对基带帧进行物理帧组帧,主要操作有增加训练序列、起始缓冲区以及结束缓冲区;

88.二进制到nrzi码转换,得到物理层比特流数据;

89.nzri比特流进行高斯滤波成形,得到高斯形状基带信号;

90.高斯基带信号进行连续积分运算,控制复数正弦信号的载波频率,等效于进行fm调制;

91.复数正弦信号的sin与cos分量分别进行数字上变频,直接合成到rf射频信号。

92.至此,ais调制器工作完成。

93.另外,ais解调器逻辑处理流程如下:

94.ais信道实时接收到基带信号,并输入以adc采样速率信号经过数字下变频(ddc)模块,输出速率为9.6ksps

×

4=38.4ksps的基带信号,以便后续模块处理。

95.数字下变频后的基带信号进入数字鉴频器,等效于对信号载频进行一阶微分运算;

96.载波频率进行一阶微分后的信号进行低通滤波,以对抵消道噪声的影响,提高参数估计信噪比;

97.低通滤波后的频率微分信号进行fft运算,估计出如下信道参数:ais突发号起始时刻;发送与接收之间载波的频率偏差;以及接收adc与发送dac之间的相位误差;

98.用估计的载波频率偏差对接收信号进行频率校正,得到一个收发频率完全一致的基带信号;

99.对频率偏差校正后的信号进行定时误差补偿,得到收发参数弯曲一致的理想采样基带信号;

100.理想基带信号进行匹配滤波,并在理想采样时刻对基带信号采样,得到nrzi比特流;

101.将nrzi比特流进行viterbi最大似然概率估计,得到整个物理帧的最低误码概率的比特数据;

102.viterbi解码后的数据进行nrzi到二进制转换,并进行crc校验,将校验通过的数

据帧还原到与发送一致的基带帧。

103.至此,ais解调器工作完成。

104.此外,asm调制器的逻辑处理流程说明如下:

105.fpga接收从数据链路层发送来的数据,对发送数据进行asm基带帧组帧,其中包括crc校验生成;

106.对asm物理层进行fec纠错编码;

107.对fec编码后的asm基带帧进行物理帧组帧,主要操作有插入训练序列、起始缓冲区以及结束缓冲区等;

108.对asm物理帧进行π/4

‑

qpsk数字调制;

109.将数字调整的i/q符号经过平方根升余弦滤波器,进行频谱成形,得到基带信号;

110.基带信号的sin与cos分量分别进行数字上变频,最后直接合成到asm rf射频信号。至此,asm调制器工作完成。

111.另外,对应的,asm解调器逻辑处理流程如下:

112.asm信道实时接收到基带信号,并输入以adc采样速率信号经过数字下变频(ddc)模块,输出速率为9.6ksps

×

4=38.4ksps的基带信号,以便后续模块处理。

113.数字下变频后的基带信号先进入平方根升余弦滤波器,得到匹配滤波后的信号,以提高接收信号信噪比;

114.匹配滤波后的基带信号先进行突发帧检测,当检测到有效突发后再进行定时误差估计(发送与接收之间的采样相位之差);

115.用估计的定时误差对接收信号进行相位校正,得到一个收发相位完全一致的基带信号;

116.把理想基带信号进行匹配滤波,并在理想采样时刻对基带信号采样,得到i/q解调符号;

117.对解调后的符号进行载波频率与相位估计,然后进行相应的校正,即完成载波同步工作。

118.对同步完的i/q符号进行π/4

‑

qpsk软解调,得到每个符号的置信概率;

119.用软解调值进行fec解码,得到最大后验概率比特;

120.fec纠错后的bit进行crc校验,如果通过则恢复成基带帧,并往数据链路层转发。至此,asm解调器工作完成。

121.此外,还包括vde物理层调制器逻辑方案:

122.vde使用了滤波器组多载波调制技术,通过滤波器组将整个带宽划分为若干个子带,在子带上传输信息。其中,每个子载波都具有一个滤波器,它起到了对各个子载波频谱的严格限制作用,使得子载波之间基本没有干扰。这些滤波器是由同一个低通滤波器原型经过等间隔的频率搬移形成的,这个低通滤波器称为原型滤波器。这些滤波器只有中心频率上的搬移,因此构成的滤波器组称为均勾滤波器组。通过处于不同中心频率的滤波器的滤波,实现了子带间基本不重叠的信号传输。

123.另外,vde调制器的逻辑处理流程说明如下:

124.fpga接收从数据链路层发送来的数据,对发送数据进行vde基带帧组帧,其中包括crc校验生成;

125.对vde基带帧进行turbo fec纠错编码;

126.对fec编码后的vde基带帧进行物理帧组帧,主要操作有插入训练序列、起始缓冲区以及结束缓冲区等;

127.根据vde随路的调制信息,对vde物理帧进行π/4

‑

qpsk、8psk或者16qam的数字调制;

128.将数字调制的i/q符号进行1:32的串并转换;

129.串并转换的32点数据按照每32点一组,进行32点ifft(反傅里叶变换);

130.将ifft输出的并行数据分别与多相滤波器进行成形滤波操作,使得每个子载波具有平方根升余弦滤波器形状;

131.成形之后的基带信号,再经过duc进行数字上变频,直接合成vde rf信号。至此,vde调制器工作完成。

132.另外,对应的,其vde体制解调器逻辑处理流程如下:

133.vde信道实时接收基带信号,并输入以adc采样速率信号经过数字下变频(ddc)模块,输出速率为.4ksps

×

32

×

2=153.6ksps的基带信号,以便后续模块处理。

134.数字下变频后的基带信号进行匹配滤波,匹配滤波器以平方根升余弦滤波器作为原型,采用32相的多相滤波器架构,得到32路匹配滤波后的并行的基带信号,以提高接收信号信噪比;

135.匹配滤波后的基带信号先进行突发帧检测,当检测到有效突发后再进行定时误差估计(发送与接收之间的采样相位之差)以及载波频率偏差估计;

136.在均衡模块用估计的定时误差对接收信号进行相位校正,得到一个收发相位完全一致的基带信号;同时用估计的载波频率偏差,对基带信号进行载波频率校正;同时进行信道均衡,以消除基带信号的码间串扰;

137.根据突发帧的信号信息,对同步完的i/q符号进行π/4

‑

qpsk、8psk或者16qam软解调,得到每个符号的置信概率;

138.用软解调值进行turbo fec解码,得到最大后验概率比特;

139.fec纠错后的bit进行crc校验,如果通过则恢复成基带帧,并往数据链路层转发。至此,vde解调器工作完成。

140.此外,对于上述网关/协议栈来说,其主要负责解析接收数据中的普通电文信息,并将解析出的应用信息相应地分发给船舶列表管理模块以及应用业务管理模块,同时将vdes相关电文参数和本机参数进行存储。具体的,包括:负责将接收数据处理模块发来的接收电文和发送数据处理模块发来的自身发送电文,结合时隙等相关信息,打包后发送给应用业务管理模块;负责接收应用业务管理模块传输过来的vdl电文相关配置信息,并进行信息存储;负责接收应用业务管理模块传输过来的电文发送信息,并传递给发送数据处理模块,进行电文发送;负责接收特殊电文处理模块电文中的指配和信道管理信息,并传输给应用业务管理模块;调用vdes电文封装与解析处理模块解析岸站和船站相关信息,分发给船舶列表管理模块;当发送数据处理模块需要打包vdes电文时,调用本模块相应电文参数接口返回相应vdes电文参数结构体供其打包vdes电文;负责接收fpga射频部分物理状态和间接同步失效报警信息,并传输给应用业务管理模块。

141.综上所述,借助于本发明的上述技术方案,实现报文的封装/解析、cstdma/sotdma

组网协议和物理层调制解调,实现人机输入/输出接口处理、电子海图显示、和用户扩展应用功能;用于实现用户的按键和usb接口输入功能;不仅结合数据交换场景的具体需求,得到的vdes分组数据网关能够高效灵活地实现海事站台之间多种数据格式交换、数据压缩、数据加密以及与异构网络互通等vde功能;而且该系统对vdes协议中的表现层进行了扩展,并在引入发射模拟通道和接收模拟通道以及基带信号处理和网关/协议栈,实现发送/接收的信息清晰理解,数据交互过程更加高效、有效和简洁。

142.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1