一种用于高速数字通信的多路并行上采样方法

本发明属于数字通信,具体涉及一种用于高速数字通信的多路并行上采样方法。

背景技术:

1、在高速数字通信领域经常需要产生任意符号速率的信号。对于采样率的转换,较为常见的方法是改变时钟频率或对信号过采样再抽取,但这两种方法在硬件实现上复杂度较高,硬件资源消耗较大,因此不适合产生较大范围符号速率的信号。

2、若不改变时钟频率,一般都会采用时域插值法来实现变采样,即在时域上利用各种曲线拟合输入采样值序列,得到数字重采样基本方程中的时变系数,进而获得插值滤波器的冲激响应。

3、对于任意小数倍的变换,使用多相结构会导致多相子滤波器数目很大且不可控,因此需要一个大容量的rom存储滤波器的系数来实现分数倍以及整数倍滤波器。针对上述问题目前一般采用farrow结构来实现任意小数倍的重采样,每计算一个内插值只需传输一个变量插值因子μm,由μm和输入采样点直接计算出内插值,不需要计算中间滤波器系数,更加便于硬件实现。

4、主流的插值方法主要有线性插值、采样保持插值、拉格朗日插值、以及新型的抛物线插值和三角插值等。在多种插值方法中,立方插值法最接近理想特性,而分段抛物插值(ppi)复杂度介于线性和立方插值算法之间,且通过合理调整设计参数可以获得接近理想的插值效果。

5、现有技术一,2019年,专利“一种farrow类型滤波器的fpga实现方法及系统”(申请号:201910124543.7,公开号:cn109905100a)提供了一种farrow类型滤波器的fpga实现方法及系统。其步骤如下:第一,对farrow滤波器的滤波器系数进行量化;第二,实时计算误差间隔uk以及对应插值基点,并将插值基点与系数作乘累加运算;第三,乘累加结果再与误差间隔uk进行乘加运算,得到输出。该专利可以实现基本的变符号率插值,但仍有几点不足:第一,该专利中插值器采用4阶拉格朗日插值器,其插值结果与理论插值结果存在较大误差;第二,该专利处理流程均为串行,无法满足高速数字通信的需求。

6、现有技术二,2021年,专利“一种可变符号速率、可任意路并行输入插值方法”(申请号:202110085533.4,公开号:cn112905946 a)公开了一种可变符号速率、可任意路并行输入插值方法。其步骤如下:第一,上位机输入控制参数确定并行数数p;第二,从ram中顺序读出p路数据;第三,计算误差间隔uk;第四,代入公式进行计算,得到对应的输出ysum值。该专利着重说明了如何对p路连续数据经过插值得到一个样点,对于n路并行输出的情况,该专利在上述基础上再并行了n-1路,但在实际处理过程中,这n-1路的输入数据与第1路的输入数据有明显的相关性,使用相同的1组ram读出数据不符合多路数据插值需求,即仅将插值器复用n次得到的n路数据无法保证相位连续性。并且,变采样率必须在上采样信号基础上进行,否则会影响到宽带信号的带内一致性,比如在200mhz的工作时钟频率以及典型4倍升余弦滚降滤波器条件下,采用最高8路的并行重采样只能处理400mbaud符号率以内的高速数字信号。

技术实现思路

1、针对现有技术存在的问题,本发明提供了一种用于高速数字通信的多路并行上采样方法,包括如下方案:

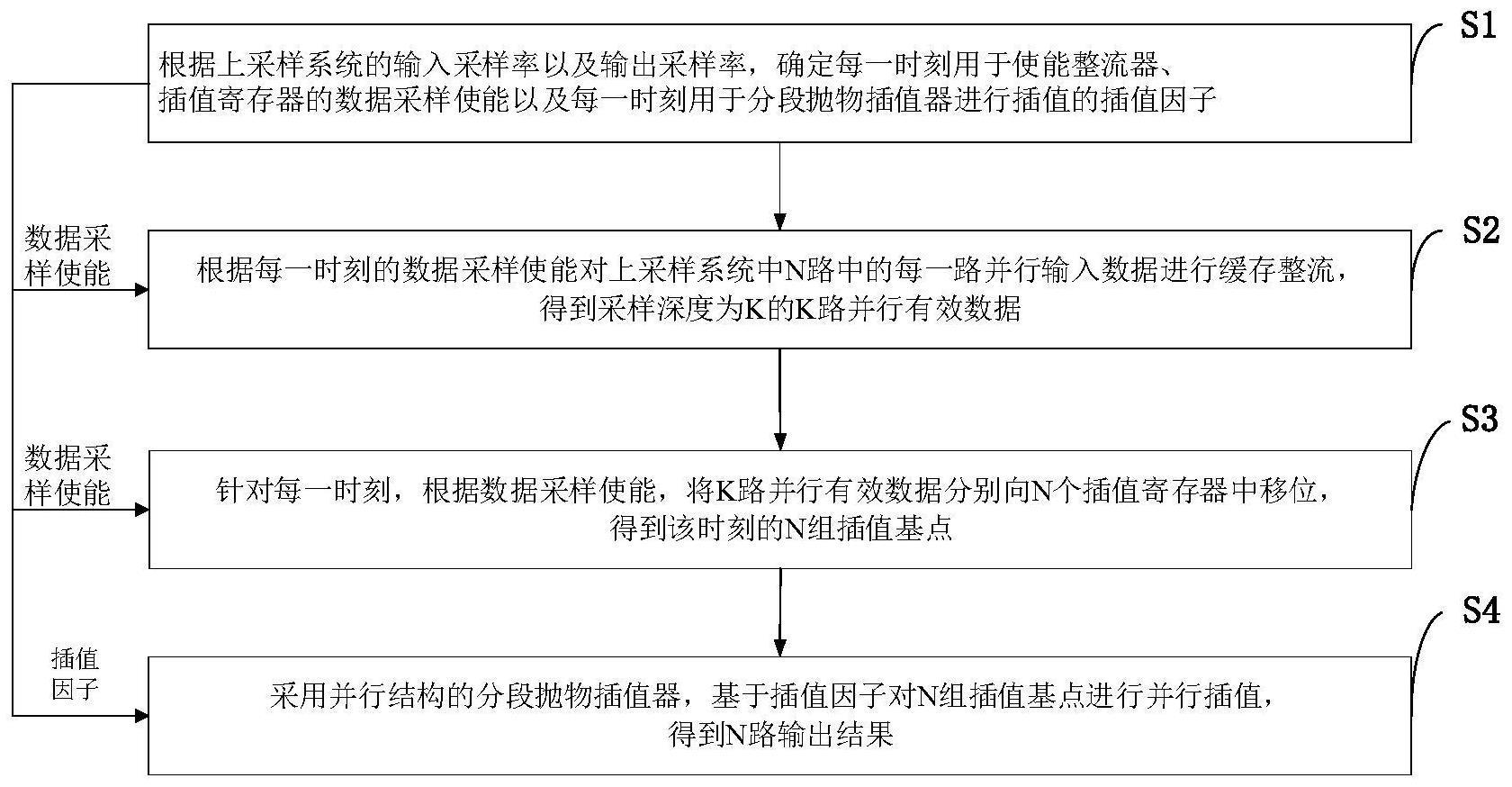

2、本发明提供的一种高速数字通信中的多路并行上采样方法应用于上采样系统,该上采样系统包括并行数控振荡器、整流器、插值寄存器以及分段抛物插值器,所述多路并行上采样方法包括:

3、s1:根据所述上采样系统的输入采样率以及输出采样率,确定每一时刻用于使能整流器以及所述插值寄存器的数据采样使能以及每一时刻用于分段抛物插值器进行插值的插值因子;

4、s2:根据每一时刻的所述数据采样使能对所述上采样系统中n路中的每一路并行输入数据进行缓存整流,得到采样深度为k的k路并行有效数据;

5、s3:针对每一时刻,根据所述数据采样使能,将所述k路并行有效数据分别向n个插值寄存器中移位,得到该时刻的n组插值基点;

6、s4:采用并行结构的分段抛物插值器,基于所述插值因子对所述n组插值基点进行并行插值,得到n路输出结果。

7、可选的,在步骤s1之前,所述多路并行上采样方法还包括:

8、将映射符号通过至少2倍根升余弦滚降滤波器srrc进行处理,得到带宽信号;

9、将所述带宽信号作为所述上采样系统的输入数据。

10、可选的,步骤s1包括:

11、s11:初始化第nts时刻所述并行数控振荡器的迭代参数rμ(n)|n=0=0,并计算所述上采样系统输入输出的采样比例i=fin/fout;

12、s12:计算所述上采样系统每一路所述迭代参数的累加结果并同时计算

13、其中,1≤m≤n;

14、s13:计算中间变量

15、其中,表示向下取整;

16、s14:计算插值因子

17、s15:计算数据采样使能validm(n),判断与是否相等,相等时validm(n)=1否则validm(n)=0,得到nts时刻的数据采样使能以及插值因子μm(n);

18、s16:令并置n=n+1,返回步骤s12计算下一时刻数据采样使能以及插值因子;

19、其中,n表示采样时刻,m表示n路中的第m路,n表示所述上采样系统的并行路数,ts表示输出采样间隔,ts=n/fout。

20、可选的,在所述上采样系统前连接有调制器,所述整流器包括ram控制器以及移位寄存器,所述s2包括:

21、s21:使用ram控制器对n路中的每一路并行输入数据进行缓存;

22、s22:移位寄存器根据所述数据采样使能确定读取使能以及所述移位寄存器的输出位置;

23、s23:按照读取使能按需读取输入所述上采样系统中,满足占空比等于fin/fout的并行输入数据;

24、s24:移位寄存器对所述ram控制器读取的每一路并行输入数据进行移位缓存;

25、其中,移位寄存器的长度为3n至4n;

26、s25:所述移位寄存器按照所述输出位置,输出k路并行有效数据。

27、可选的,其特征在于,

28、所述s22包括:

29、s221:移位寄存器初始化数据指针位置为addr(n)|n=0=0,flag=0;

30、s222:移位寄存器计算nts时刻的n路中数据采样使能为1的总个数

31、s223:更新数据指针位置addr(n+1)=addr(n)+svalid(n)+flag;

32、s224:判断addr(n+1)是否大于n,大于n时flag=-n,同时将读取使能置1,从ram控制器中读取数据;如小于n则flag=0,将读取使能置0,以更新flag。

33、可选的,步骤s24包括:

34、若ram控制器按照读取使能读取到并行输入数据,则移位寄存器向右移位,将读取到的并行输入数据从左逐个放入移位寄存器的存储器中,以实现移位缓存;

35、步骤s25包括:

36、从当前指针位置addr(n)开始向地址增加方向顺序读取n路数据作为输出;

37、其中,所述n路数据中的前k路为并行有效数据,k=svalid(n);flag表示指针位置跳变个数。

38、可选的,在所述s25之后,所述方法还包括:

39、s26:ram控制器接收调制器持续发送的数据块,并根据自身写入地址与读出地址的地址差,向调制器反馈标志位,以使调制器调整自身输出数据块的占空比之后,向所述ram控制器输出数据块。

40、可选的,所述s3包括:

41、s31:初始化插值寄存器的存储数值rinterp(n)|n=0=[0,0,0,0,0,0,0,0];

42、s32:计算nts时刻前l个数据采样使能中1的个数1≤l≤n;

43、s33:针对每一时刻的每一组,执行将插值寄存器rinterp(n)右移pl位,得到该时刻的n组插值基点xl(n);

44、其中,l表示n组中的任一组;

45、s34:令存储数值rinterp(n+1)=xn(n),并置n=n+1,返回s32,得到每一时刻的n组插值基点。

46、可选的,所述s33包括:

47、s331:当pl≤8时,将k路并行有效数据中取出最低的pl位数据从左放入插值寄存器;

48、其中高位在左;

49、s332:当pl>8时,取出位置pl,pl-1,pl-2,…,pl-7这8位数据按顺序放入插值寄存器,其中高位pl在左;

50、s333:以1≤l≤n重复执行s331至s332 n次,得到每一时刻的n组插值基点xl(n)。

51、可选的,所述s4包括:

52、s41:计算分段抛物插值器的中间变量

53、其中,cxy表示分段抛物插值器的插值系数,xl表示第l组的插值基点;μl表示第l组的插值因子;

54、s42:分段抛物插值器计算所述上采样系统第l路的输出结果yl=mult1l+μl*(mult2l+μl*(mult3l+μl*mult4l))。

55、本发明的有益效果包括:

56、(1)本发明提供的一种高速数字通信中的多路并行上采样方法,只需要更改寄存器位宽和插值器并行数量即可实现插值并行路数n的改变,灵活性以及可扩展性高,且并行路数上界可以达64;

57、(2)本发明提供的一种高速数字通信中的多路并行上采样方法,64路并行情况支持最高符号率可达3gbaud;

58、(3)本发明提供的一种高速数字通信中的多路并行上采样方法,使用全并行结构,以线性复杂度实时计算控制参数,满足高并行路数下的控制需求;

59、(4)本发明提供的一种高速数字通信中的多路并行上采样方法,采用分段抛物插值器的内插方式实现插值,相比于现有技术插值精度更高。

- 还没有人留言评论。精彩留言会获得点赞!