一种基于FPGA的低功耗多载波射频信号发生方法与流程

一种基于fpga的低功耗多载波射频信号发生方法

技术领域

1.本发明属于数字信号处理的技术领域,具体涉及一种基于fpga的低功耗多载波射频信号发生方法。

背景技术:

2.ad9129作为高性能rf数模转换器,支持最高达5.7gpgs更新速率的射频信号输出,在雷达,干扰发射器、点对点仪器仪表等方面有广泛应用。传统的基于fpga的ad9129应用基于多相处理的方法,对fpga内部dsp资源及时序均有较高要求,特别是需要实现多载波输出功能时该方法需耗费较多fpga内部资源,导致产品功耗及成本增加,开发难度增大。

技术实现要素:

3.本发明的目的在于提供一种基于fpga的低功耗多载波射频信号发生方法,旨在解决上述问题。

4.本发明主要通过以下技术方案实现:一种基于fpga的低功耗多载波射频信号发生方法,包括以下步骤:步骤s100:利用fpga直接数字频率合成ip核产生数字信号数据流,合成各载波的数字信号数据流,并放入ram中;步骤s200:利用多相输出原理将ram中的数据读出并拆分为多相的形式;步骤s300:利用fpga自带的高速传输原语完成数据转换,并通过高速时钟拍到高速数模转换器输入端并实现射频信号的数模转换。

5.为了更好地实现本发明,进一步地,所述步骤s100中,fpga直接数字频率合成ip核的数量由载波数量决定,且fpga直接数字频率合成ip核的工作时钟为高速数模转换器采样速率的1/10。

6.为了更好地实现本发明,进一步地,所述ram深度设置为高速数模转换器采样速率的整数倍。

7.为了更好地实现本发明,进一步地,所述步骤s200中,将输出数据拆分为16相,则ram的读数据宽度为写数据宽度的16倍,同时读数据时钟为规定的高速数模转换器采样速率的1/16。

8.为了更好地实现本发明,进一步地,所述步骤s300中,fpga自带的高速传输原语为oddr或oserdese。所述的高速传输原语选择应满足所选数模转换器的相关接口时序实现数据的正确转换。

9.为了更好地实现本发明,进一步地,所述步骤s300中,在数据输出到高速数模转换器接口时,需按照高速数模转换器接口时序,选择相应的原语,完成输出传输。

10.本发明选用最高采样率为5.7gps的高速数模转换器ad9129作为信号发射端,通过搭建一种新的软件接口在fpga资源消耗率较低的情况下实现射频数字信号到模拟信号的正确转换。本发明充分利用fpga数据转换原理并结合数据多相输出原理减少了fpga内部

dsp资源的消耗,降低了fpga的资源占用,在多载波输出、多目标干扰等领域有广阔应用前景。

11.本发明的有益效果:(1)本发明充分利用fpga数据转换原理并结合数据多相输出原理减少了fpga内部dsp资源的消耗,降低了fpga的资源占用,在多载波输出、多目标干扰等领域有广阔应用前景;(2)将ram深度为ad9129采样速率的整数倍,可以保证数据的连续性,具有较好的实用性;(3)若要实现多载波功能,只需要根据载波数增加相应数量的dds,并将各dds输出的数据进行叠加截位再放入到ram中即可,在软件上易于实现同时极大节约了fpga资源,降低了开发成本。

附图说明

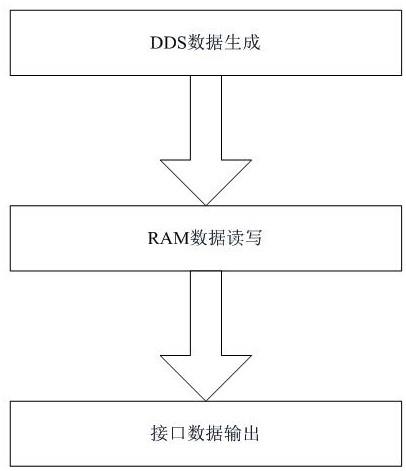

12.图1为本发明的原理框图。

具体实施方式

13.实施例1:一种基于fpga的低功耗多载波射频信号发生方法,如图1所示,包括以下步骤:步骤s100:利用fpga直接数字频率合成ip核产生数字信号数据流,合成各载波的数字信号数据流,并放入ram中;步骤s200:利用多相输出原理将ram中的数据读出并拆分为多相的形式;步骤s300:利用fpga自带的高速传输原语完成数据转换,并通过高速时钟拍到高速数模转换器输入端并实现射频信号的数模转换。在数据输出到高速数模转换器接口时,需按照高速数模转换器接口时序,选择相应的原语,完成输出传输。

14.本发明充分利用fpga数据转换原理并结合数据多相输出原理减少了fpga内部dsp资源的消耗,降低了fpga的资源占用,在多载波输出、多目标干扰等领域有广阔应用前景。

15.实施例2:本实施例是在实施例1的基础上进行优化,所述步骤s100中,所述的直接数字频率合成ip核(dds)数量由载波数量决定,其工作时钟为高速数模转换器ad9129采样速率的1/10,为保证数据连续性,ram深度为ad9129采样速率的整数倍。

16.进一步地,所述步骤s200中,所述的ram读数据宽度及读时钟需符合多相数据输出原理,比如为满足fpga内部时钟要求,将输出数据拆分为16相,则ram的读数据宽度为写数据宽度的16倍,同时读数据时钟为规定的da采样速率的1/16。

17.本发明选用最高采样率为5.7gps的高速数模转换器ad9129作为信号发射端,通过搭建一种新的软件接口在fpga资源消耗率较低的情况下实现射频数字信号到模拟信号的正确转换。本发明充分利用fpga数据转换原理并结合数据多相输出原理减少了fpga内部dsp资源的消耗,降低了fpga的资源占用,在多载波输出、多目标干扰等领域有广阔应用前景。

18.本实施例的其他部分与实施例1相同,故不再赘述。

19.实施例3:一种基于fpga的低功耗多载波射频信号发生方法,如图1所示,包括以下步骤:步骤1,利用fpga直接数字频率合成ip核(dds)产生相应的数字信号数据流,将各载波数据流进行合成,并将其放入一定深度的ram中。

20.根据载波数量,决定需用的dds ip核数量,根据输出信号的频率要求和相位要求,依据dds ip核工作原理,产生相应的相位偏移和相位增量控制字,并将dds ip核工作时钟设为高速da采样速率的1/10。待dds ip核数据输出稳定后,将dds输出的数据存到ram中,为保证信号的连续性,ram深度设置为高速da采样速率的整数倍,将设定深度写满后将ram写使能拉低。

21.步骤2,利用多相输出的原理将ram中的数据读出并拆分为多相的形式。

22.ram读数据宽度及读时钟需符合多相数据输出原理,比如为满足fpga内部时钟要求,将输出数据拆分为16相,则ram的读数据宽度为写数据宽度的16倍,同时读数据时钟为规定的da采样速率的1/16。

23.步骤3,利用fpga自带的高速传输原语,如oddr,oserdese等完成数据转换并通过高速时钟拍到da输入端并实现射频信号的数模转换。

24.在数据输出到da接口时,需按照da接口时序,选择相应的原语,完成输出传输。

25.本发明选用最高采样率为5.7gps的高速数模转换器ad9129作为信号发射端,通过搭建一种新的软件接口在fpga资源消耗率较低的情况下实现射频数字信号到模拟信号的正确转换。本发明充分利用fpga数据转换原理并结合数据多相输出原理减少了fpga内部dsp资源的消耗,降低了fpga的资源占用,在多载波输出、多目标干扰等领域有广阔应用前景。

26.实施例4:一种基于fpga的低功耗多载波射频信号发生方法,如图1所示,根据载波数量,选用一定数量的fpga直接数字频率合成ip核(dds),利用dds ip核产生相应的数字信号数据流,将各载波数据流进行合成,并将其放入一定深度的ram中,利用多相输出的原理将ram中的数据读出并拆分为多相的形式,利用fpga自带的高速传输原语,如oddr,oserdese等完成数据转换并通过高速时钟拍到da输入端,实现射频信号的数模转换。

27.拟通过ad9129产生1g射频信号,并设定采样率为2.8g,依据通过fpga产生高速射频数字信号的一般方法,需要16个采样率为2800/16=175m的dds,根据设定的信号分辨率,通过dds频率增量算法得到频率控制字,并以360/16的步进设定dds相位偏移量,将各dds输出的数据进行叠加截位,并按照da要求的ddr时序输出。该方法需要16个dds ip核及8个加法器才能实现,将消耗大量fpga资源,若需要输出多个载波,则所需dds ip核数量会随着载波数量翻倍,对fpga资源有较高要求。

28.拟通过ad9129产生1g射频信号,并设定采样率为2.8g,本发明的方法为,首先通过采样率为280m的dds产生100m的信号,将数据存入到深度为采样率整数倍(如2800)的ram中,ram写满后切换到读状态,读时钟为175m,读地址深度为ram深度的16/1,读数据宽度为写数据的16倍,将读出的数据拆分为16相,并按照da要求的ddr时序输出。

29.与传统方法相比,本发明只需要1个dds及1个ram,若要实现多载波功能,只需要根据载波数增加相应数量的dds,并将各dds输出的数据进行叠加截位再放入到ram中即可,在

软件上易于实现同时极大节约了fpga资源,降低了开发成本。本发明充分利用fpga数据转换原理并结合数据多相输出原理减少了fpga内部dsp资源的消耗,降低了fpga的资源占用,在多载波输出、多目标干扰等领域有广阔应用前景。

30.以上所述,仅是本发明的较佳实施例,并非对本发明做任何形式上的限制,凡是依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化,均落入本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1