一种支持Wi-SUN协议的Uart-以太网转换模组的制作方法

一种支持wi-sun协议的uart-以太网转换模组

技术领域

1.本实用新型属于物联网通信领域,尤其涉及一种支持wi-sun协议的uart-以太网转换模组。

背景技术:

2.物联网是目前信息化时代的一个大趋势,它强调的是万物联网,物联网的普及将会对我们未来的生活带来极大的便利,因物联网兴起,远距离通讯需求日益增加,低功耗广域网通讯技术犹如百花齐放,包括wi-sun,lorawan, nb-iot,zigbee等。这些方案大致分为两类,一类是运营商的蜂窝网络、一类是自组网络。运营商的蜂窝网络例如nb-iot,它有着布网方便、技术门槛低、网络规模大等优势。自组网络例如比较成熟的lorawan、zigbee等,能够自己掌控网络,且通信的带宽较高,可以自己定制协议等优势。

3.现在nb-iot等的计费方式还不是很明确,导致用户使用成本比较高。另外一个限制在于用户数据都要跑在公网,对于数据安全是一个考验。由于lorawan的核心技术在其公司semtech的手中,这种形式无形中使用者会绑定在lora技术下,该技术的发展和更新以及政策的变动都会影响到lorawan的使用者。而zigbee虽然已经是一个标准的成熟的组网技术,但是他的网络范围是远远达不到物联网需求的。同时,其它厂商wi-sun 边缘路由器(border router简称br)方案上行输出采用uart。导致输出速率低,同时数据只能以串口报文形式交互,失去了wi-sun本身数据格式为ipv6的优势。

4.例如,一种在中国专利文献上公开的“以太网网关、以太网网关设备以及系统”,其公告号为“cn107040461a”,本发明提供了一种以太网网关、以太网网关设备以及系统,涉及通信领域,缓解了现有技术中的网关功能比较单一,不能满足用户日益增长的使用要求的问题,实现以太网网关的多功能性,提高了以太网网关的适应性和使用范围。本发明实施例公开的以太网网关,包括以太网主控板,该以太网主控板包括以太网接口、以太网隔离变压器、以太网控制器、微控制器、串行接口、带有usb接口的usb控制器、sd卡槽接口和存储器;以太网接口、以太网隔离变压器、以太网控制器依次连接;以太网控制器、串行接口、带有usb接口的usb控制器、外围供电电路、sd卡槽接口、存储器分别与微控制器相连接。

技术实现要素:

5.本实用新型是为了创建一个标准的、规范的、不绑定的能够实现大规模组网的一种无线组网方案的硬件模块。一种支持wi-sun协议的uart-以太网转换模组,为wi-sun br提供标准以太网输出接口,保证了通讯速率,以及数据交互格式为标准以太网ipv6,数据通过以太网传输,用户可借助现有网络传输数据,同时解决了传输距离以及传输路径的问题。

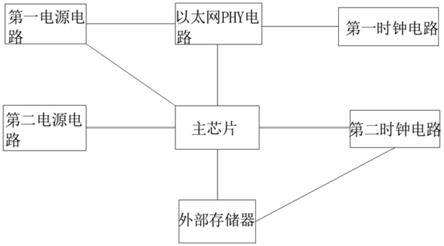

6.为了实现上述目的,本实用新型采用以下技术方案:包括以太网phy电路、主芯片、第一电源电路、第二电源电路、第一时钟电路、第二时钟电路和外部存储器电路,所述以太网phy电路分别连接有第一电源电路、第一时钟电路和主芯片,所述主芯片分别连接有第一电源电路、第二电源电路、第二时钟电路和外部存储器电路,所述第二时钟电路与外部存储

器相连。本实用新型基于ieee802.15.4g,ieee802.1x的规范,为wi-sun br提供标准以太网输出接口,保证了通讯速率,以及数据交互格式为标准以太网ipv6,数据通过以太网传输,用户可借助现有网络传输数据,同时解决了传输距离以及传输路径的问题。

7.作为优选,所述以太网phy电路包括以太网芯片u5、电阻r29、电阻r33、电阻r35、电阻r38、电容c11、电容c13、电容c20、电容c21、电阻r42、电阻r50、电阻r51、电阻r39、电容c12、电容c19和电阻r40,所述以太网芯片u5的测试启用引脚与电阻r35的一端相连,所述电阻r35的另一端与电阻r33的一端相连,所述电阻r33的另一端与以太网芯片u5的管理数据接口引脚相连,所述电阻r29的一端与3.3v使能端相连,所述3.3v使能端还分别与电阻r33和电阻r35相连,所述电阻r29的另一端与以太网芯片u5的多路复用引脚相连,所述电阻r38的一端与以太网芯片u5的带隙电路电阻器引脚相连,所述电阻r38的另一端接地,所述以太网芯片u5的调节器电源输出引脚与电容c11的一端相连,所述电容c11的另一端接地,所述电容c13与电容c11并联,所述以太网芯片u5的3.3v模拟电源输入引脚与电阻r42的一端相连,所述电阻r42的另一端与使能端相连,所述电容c20的一端与以太网芯片u5的3.3v模拟电源输入引脚相连,所述电容c20的另一端接地,所述电容c21的一端与以太网芯片u5的3.3v模拟电源输入引脚相连,所述电容c21的另一端接地,所述电阻r50的一端与以太网芯片u5的传输错误或光纤判断引脚相连,所述电阻r50的另一端接地,所述电阻r51的一端与以太网芯片u5的rmii引脚相连,所述电阻r51的另一端与3.3v电压端相连,所述电阻r39的一端与以太网芯片u5的接受时钟引脚相连,所述电阻r39的另一端与电容c12的一端相连,所述电容c12的另一端接地,所述电阻r40的一端与以太网芯片u5的数字电源输入引脚相连,所述电阻r40的另一端与3.3v使能端相连,所述电容c19的一端与以太网芯片u5的数字电源输入引脚相连,所述电容c19的另一端接地。以太网芯片u5与mcu之间通过rmii接口实现数据的交互,并负责数据从数字到模拟的转换,并将模拟数据通过tdp和tdn以差分的形似发送出去。同时ip101gri也负责将通过rdp和rdn接收到的模拟数据转换成数字数据通过rmii接口发送给mcu。

8.作为优选,所述第一电源电路包括电容c1、电阻r1、电源芯片u1、电容c2、电容c3和电感b1,所述电容c1的一端与电路输入端vdd5.0相连,所述电容c1的另一端接地,所述电阻r1的一端与输入电源vdd5.0相连,所述电阻r1的另一端与电源芯片u1的使能引脚相连,所述电源芯片u1的输入引脚与输入电源vdd5.0相连,所述电源芯片u1的反馈引脚与电容c3的一端相连,所述电容c3的另一端接地,所述电源芯片u1的输出引脚与电容c2的一端相连,所述电容c2的另一端接地,所述电感b1的一端与电源芯片u1的输出引脚相连,所述电感b1的另一端与电路输出端vdd33相连。第一电源电路给主芯片和以太网phy电路供电,供电为dc 5v,内部采用一路ldo电路,输出3.3v同时供给vc5800、ip101gri、有源晶体电路供电。

9.作为优选,所述第一时钟电路包括第一晶振x1、电容c30和电容c31,所述第一晶振x1的输入引脚与电容c31的一端相连,所述电容c31的另一端分别与第一晶振x1的第二接地引脚相连,所述第一晶振x1的第二接地引脚接地,所述第一晶振x1的输出引脚与电容c30的一端相连,所述电容c30的另一端与第一晶振x1的第一接地引脚相连,所述第一晶振x1的第一接地引脚接地。第一时钟电路为无源晶振电路,c30、c31是晶振负载的电容,因为x1为phy内部时钟提供基准时钟源,以太网输入/输出为10m/100m自适应,为了保证数据速率同步采用了高精度晶体。

10.作为优选,所述第二电源电路包括电感l1、电阻r23和电容c7,所述电感l1的一端与主芯片直流转换输出引脚相连,所述电感l1的另一端与直流1.2v电压端d1v2相连,所述电容c7的一端与电源电路输出端d1v2相连,所述电容c7的另一端与电阻r23相连,所述电容c7的另一端还与主芯片低压供电引脚相连,所述电阻r23两端接地。第二电源电路通过主芯片直流转换输出引脚输出1.2v给mcu core供电。

11.作为优选,所述第二时钟电路包括电阻r56、电阻r60、电容c33、第二晶振x2、电阻r58、电阻r59和电阻r61,所述电阻r56与第二晶振x2的输入引脚相连,所述电阻r60的一端与第二晶振x2的输入引脚相连,所述电阻r60的另一端接地,所述第二晶振x2的输入引脚与电容c33的一端相连,所述电容c33的另一端接地,所述第二晶振x2的输出引脚与电阻r58的一端相连,所述电阻r58的另一端与电阻r61的一端相连,电阻r61的另一端接地,所述电阻r59的一端与电阻r58相连,所述电阻r59的另一端与主芯片上的时钟输出引脚相连。第二时钟电路为有源晶体电路,有源晶体电路,3.3v输入端预留c33,用来调整输入电源纹波和噪声;输出端预留电阻r58、r59、r61用来调整有源晶体电路输出幅值。

12.作为优选,所述外部存储器电路包括电阻r47、电阻r48、存储器芯片u6、电阻r49和电容c26,所述电阻r48的一端与电源输入端d3v3相连,所述电阻r48的另一端与存储器芯片u6的片选引脚相连,所述电阻r47的一端与电源输入端d3v3相连,所述电阻r47的另一端与存储器芯片u6的写入数据保护引脚相连,所述存储器芯片u6的输出引脚与主芯片的存储器输入引脚相连,所述存储器芯片u6的输入引脚与主芯片的存储器输出引脚相连,所述存储器芯片u6的外接电路引脚与电源输入端d3v3相连,所述存储器芯片u6的保持状态引脚与电阻r49的一端相连,所述电阻r49的另一端与电源输入端d3v3相连,所述电容c26的一端与电阻r49的一端相连,所述电容c26的另一端接地,所述存储器芯片u6的时钟引脚与第二时钟电路相连。本实用新型方案内部预留flash,扩展存储容量为512kb,可用于数据缓存或升级是数据备份使用。

13.作为优选,所述主芯片具体为vc5800。

14.作为优选,所述以太网芯片u5采用ip101gri芯片。

15.因此,本实用新型具有如下的有益效果:

16.1、本实用新型方案的硬件功能实现数据从uart到以太网的转换,为wi-sun br提供标准的以太网输入输出接口,另外本实用新型方案是一款支持wi-sun协议的硬件,也就是说能够提供给用户一个支持标准的、规范的、不绑定的能够实现大规模组网的一种无线组网方案,解决物联网行业的几个问题如标准化协议,开放不绑定,实现大规模组网应用,低功耗远距离方便进行各种物联网设备的改造,减低改造成本;

17.2、采用与wi-sun 系统芯片厂商濎通芯vc7300bu相同厂商的vc5800和phy ic实现该功能,适配性和兼容性会更好。

附图说明

18.图1是本实用新型整体结构示意图;

19.图2是本实用新型整体原理图;

20.图3是本实用新型以太网phy电路原理图;

21.图4是本实用新型第一电源电路原理图;

22.图5是本实用新型第二电源电路原理图;

23.图6是本实用新型第一时钟电路原理图;

24.图7是本实用新型第二时钟电路原理图;

25.图8是本实用新型外部存储器原理图图。

具体实施方式

26.实施例一

27.本实施例提出一种支持wi-sun协议的uart-以太网转换模组。参考图1和图2,包括以太网phy电路、主芯片、第一电源电路、第二电源电路、第一时钟电路、第二时钟电路和外部存储器电路,所述以太网phy电路分别连接有第一电源电路、第一时钟电路和主芯片,所述主芯片分别连接有第一电源电路、第二电源电路、第二时钟电路和外部存储器电路,所述第二时钟电路与外部存储器相连。本实用新型基于ieee802.15.4g,ieee802.1x的规范,为wi-sun br提供标准以太网输出接口,保证了通讯速率,以及数据交互格式为标准以太网ipv6,数据通过以太网传输,用户可借助现有网络传输数据,同时解决了传输距离以及传输路径的问题。

28.参考图3,所述以太网phy电路包括以太网芯片u5、电阻r29、电阻r33、电阻r35、电阻r38、电容c11、电容c13、电容c20、电容c21、电阻r42、电阻r50、电阻r51、电阻r39、电容c12、电容c19和电阻r40,所述以太网芯片u5的测试启用引脚与电阻r35的一端相连,所述电阻r35的另一端与电阻r33的一端相连,所述电阻r33的另一端与以太网芯片u5的管理数据接口引脚相连,所述电阻r29的一端与3.3v使能端相连,所述3.3v使能端还分别与电阻r33和电阻r35相连,所述电阻r29的另一端与以太网芯片u5的多路复用引脚相连,所述电阻r38的一端与以太网芯片u5的带隙电路电阻器引脚相连,所述电阻r38的另一端接地,所述以太网芯片u5的调节器电源输出引脚与电容c11的一端相连,所述电容c11的另一端接地,所述电容c13与电容c11并联,所述以太网芯片u5的3.3v模拟电源输入引脚与电阻r42的一端相连,所述电阻r42的另一端与使能端相连,所述电容c20的一端与以太网芯片u5的3.3v模拟电源输入引脚相连,所述电容c20的另一端接地,所述电容c21的一端与以太网芯片u5的3.3v模拟电源输入引脚相连,所述电容c21的另一端接地,所述电阻r50的一端与以太网芯片u5的传输错误或光纤判断引脚相连,所述电阻r50的另一端接地,所述电阻r51的一端与以太网芯片u5的rmii引脚相连,所述电阻r51的另一端与3.3v电压端相连,所述电阻r39的一端与以太网芯片u5的接受时钟引脚相连,所述电阻r39的另一端与电容c12的一端相连,所述电容c12的另一端接地,所述电阻r40的一端与以太网芯片u5的数字电源输入引脚相连,所述电阻r40的另一端与3.3v使能端相连,所述电容c19的一端与以太网芯片u5的数字电源输入引脚相连,所述电容c19的另一端接地。所述以太网芯片u5采用ip101gri,ip101gri与mcu之间通过rmii接口实现数据的交互,并负责数据从数字到模拟的转换,并将模拟数据通过tdp和tdn以差分的形似发送出去。同时ip101gri也负责将通过rdp和rdn接收到的模拟数据转换成数字数据通过rmii接口发送给mcu。以太网phy电路采用ip101gri芯片。

29.参考图4和图5,所述第一电源电路包括电容c1、电阻r1、电源芯片u1、电容c2、电容c3和电感b1,所述电容c1的一端与电路输入端vdd5.0相连,所述电容c1的另一端接地,所述

电阻r1的一端与输入电源vdd5.0相连,所述电阻r1的另一端与电源芯片u1的使能引脚相连,所述电源芯片u1的输入引脚与输入电源vdd5.0相连,所述电源芯片u1的反馈引脚与电容c3的一端相连,所述电容c3的另一端接地,所述电源芯片u1的输出引脚与电容c2的一端相连,所述电容c2的另一端接地,所述电感b1的一端与电源芯片u1的输出引脚相连,所述电感b1的另一端与电路输出端vdd33相连。所述第二电源电路包括电感l1、电阻r23和电容c7,所述电感l1的一端与主芯片直流转换输出引脚相连,所述电感l1的另一端与直流1.2v电压端d1v2相连,所述电容c7的一端与电源电路输出端d1v2相连,所述电容c7的另一端与电阻r23相连,所述电容c7的另一端还与主芯片低压供电引脚相连,所述电阻r23两端接地。供vc5800、ip101gri、有源晶体工作电源电路,考虑输出电流要大于等于300ma范围,这里选择输出电流范围是dc 3.3v 500ma的ldo。为了保证芯片输入电源上的噪声尽可能的小,需要在电源芯片u1上并联一个对地1μf旁路电容;使能引脚是芯片关闭控制引脚,低电平关闭芯片、高电平使能芯片,因为输出的3.3v需要提供给主芯片,该ldo不能处于关闭状态,故通过10k电阻r1上拉至输入电压;输出引脚是芯片电压输出端,为了更好的抑制噪声和提高输出电压稳定性,输出端并联一个1uf或者更大的滤波电容c3。所述第二电源电路包括电感l1、电阻r23和电容c7,所述电感l1的一端与主芯片直流转换输出引脚相连,所述电感l1的另一端与直流1.2v电压端d1v2相连,所述电容c7的一端与电源电路输出端d1v2相连,所述电容c7的另一端与电阻r23相连,所述电容c7的另一端还与主芯片低压供电引脚相连,所述电阻r23两端接地。第二电源电路通过主芯片直流转换输出引脚输出1.2v给mcu core供电,通过连接主芯片直流转换输出引脚和低压供电引脚,保证输出电流持续稳定,且纹波和噪声尽可能小,外围过流电感l1选用6.8uh可以通过1a电感和滤波电容c7选用10uf,保证输出电流品质。

30.参考图6和图7,所述第一时钟电路包括第一晶振x1、电容c30和电容c31,所述第一晶振x1的输入引脚与电容c31的一端相连,所述电容c31的另一端分别与第一晶振x1的第二接地引脚相连,所述第一晶振x1的第二接地引脚接地,所述第一晶振x1的输出引脚与电容c30的一端相连,所述电容c30的另一端与第一晶振x1的第一接地引脚相连,所述第一晶振x1的第一接地引脚接地。第一时钟电路为无源晶振电路,c30、c31是晶振负载的电容,因为x1为phy内部时钟提供基准时钟源,以太网输入/输出为10m/100m自适应,为了保证数据速率同步采用了高精度晶体。所述第二时钟电路包括电阻r56、电阻r60、电容c33、第二晶振x2、电阻r58、电阻r59和电阻r61,所述电阻r56与第二晶振x2的输入引脚相连,所述电阻r60的一端与第二晶振x2的输入引脚相连,所述电阻r60的另一端接地,所述第二晶振x2的输入引脚与电容c33的一端相连,所述电容c33的另一端接地,所述第二晶振x2的输出引脚与电阻r58的一端相连,所述电阻r58的另一端与电阻r61的一端相连,电阻r61的另一端接地,所述电阻r59的一端与电阻r58相连,所述电阻r59的另一端与主芯片上的时钟输出引脚相连。第二时钟电路为有源晶体电路,有源晶体电路,3.3v输入端预留c33,用来调整输入电源纹波和噪声;输出端预留电阻r58、r59、r61用来调整有源晶体电路输出幅值。

31.参考图8,所述外部存储器电路包括电阻r47、电阻r48、存储器芯片u6、电阻r49和电容c26,所述电阻r48的一端与电源输入端d3v3相连,所述电阻r48的另一端与存储器芯片u6的片选引脚相连,所述电阻r47的一端与电源输入端d3v3相连,所述电阻r47的另一端与存储器芯片u6的写入数据保护引脚相连,所述存储器芯片u6的输出引脚与主芯片的存储器

输入引脚相连,所述存储器芯片u6的输入引脚与主芯片的存储器输出引脚相连,所述存储器芯片u6的外接电路引脚与电源输入端d3v3相连,所述存储器芯片u6的保持状态引脚与电阻r49的一端相连,所述电阻r49的另一端与电源输入端d3v3相连,所述电容c26的一端与电阻r49的一端相连,所述电容c26的另一端接地,所述存储器芯片u6的时钟引脚与第二时钟电路相连。本实用新型方案内部预留flash,扩展存储容量为512kb,可用于数据缓存或升级是数据备份使用。

32.本实用新型基于ieee802.15.4g,ieee802.1x的规范,为wi-sun br提供标准以太网输出接口,保证了通讯速率,以及数据交互格式为标准以太网ipv6,数据通过以太网传输,用户可借助现有网络传输数据,同时解决了传输距离以及传输路径的问题。本实用新型的主芯片具体采用濎通芯的vc5800,vc5800基于arm cortex m4 mcu,内建dc buck,内核工作电压1.2v;支持rmii接口以太网数据交互,提供uart,以及有源晶体输入等。vc5800实现从uart到ipv6的数据转换,并通过rmii接口,将数据并行发送给以太网芯片。本实用新型方案的硬件功能实现数据从uart到以太网的转换,为wi-sun br提供标准的以太网输入输出接口,另外本实用新型方案是一款支持wi-sun协议的硬件,也就是说能够提供给用户一个支持标准的、规范的、不绑定的能够实现大规模组网的一种无线组网方案,解决物联网行业的几个问题如标准化协议,开放不绑定,实现大规模组网应用,低功耗远距离方便进行各种物联网设备的改造,减低改造成本。

33.在保证支持wi-sun br具有以太网输出功能的情况下,还能通过其它具有uart输入以太网输出的mcu和以太网芯片来实现,实施方式与本方案实施方式相同,但是其兼容性不如本方案稳定可靠,速率也无法与rf芯片适配。

34.以上所述,仅为本实用新型的具体实施方式,但本实用新型的保护范围并不局限于此,任何不经过创造性劳动想到的变化或替换,都应涵盖在本实用新型保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1