一种lora无线模块的制作方法

1.本实用新型涉及无线通信领域,特别是涉及一种lora无线模块。

背景技术:

2.在万物互联的物联网时代,无线通信技术变得越来越重要,给人们的生活带来的极大的便利。人们接触较多的是高速无线通信技术,如4g、wifi,这类无线通信技术具有高速率、低时延、传输量大等特点。同样的,还有很多应用场景需要低速率无线通信技术。如蓝牙、zigbee、fsk、nbiot、lora,这类无线通信技术具有低速率、传输量小、功耗低等特点。针对于远距离、低功耗应用而言,蓝牙、zigbee技术传输距离较近,一般适用于室内应用;fsk、ook技术虽然传输距离远,但在复杂的环境下较难达到理想的传输效果,抗干扰性不足;nbiot技术虽传输距离远、有较好的抗干扰性,但需要建立在运营商的基础上;lora技术具有传输距离远、抗干扰性强、功耗低等特点,并且无需建立在运营商的基础之上,对于大部分远距离、低功耗应用而言,是一种很好的选择。然而目前的lorawan无线射频模块一般是基于semtech公司sx1278或sx1276射频芯片开发,虽然距离可以达到公里级别,但是其功耗也比较大,发射功率为15dbm时,电流达60ma,处于接收状态时其电流达12ma。目前物联网行业的应用大多数产品都不是市电供电,而是电池或者太阳能方式等供电,这些场景对模块的功耗要求特别高。由于芯片大小,电路设计,器件选择等原因,现在市面上的lora射频模块一般采用mcu+lora射频芯片的组合方式,算上器件成本、交期等考虑因素,会使得模块的体积大,集成度低。

3.例如,一种在中国专利文献上公开的“一种基于lora无线模块的can通讯电路”,其公告号cn210327612u,包括光耦u4、光耦u3、can芯片u5和电感l1,所述光耦u4的1脚与4脚不接,2脚与滤波电容c10的下端连接,3脚与限流电阻r13的右端连接,5脚接can信号地gnd_can1,6脚接can芯片u5的1脚,所述6n137光耦u3的1脚与4脚不接,2脚接隔离电源vcc5v can1,3脚接限流电阻r16左端。该专利基于lora无线模块的can通讯电路能更灵活的实现can通讯的传输,相比无线网络传输成本更低,在信号实时性和传输速率上依旧高效。然而由于芯片大小,电路设计,器件选择等原因,该专利芯片的集成度低,模块体积大,且功耗较大,效率较低,无法满足需求。

技术实现要素:

4.本实用新型针对现阶段基于sx1278或sx1276射频芯片的lorawan无线射频模块功耗大、体积大、集成度低且成本较高的问题;提供了一种lora无线模块;该无线模块使用集成了mcu+lora功能的stm32wle5jb型号的单片机作为主芯片,提高了模块的集成度,简化了芯片之间的引脚连接设计,优化了电路布局,降低了设计成本,同时在射频收发电路采用了发射和接收链路通过高频开关隔离的方式,提高电路灵敏度和功率,从而提升了无线射频模块的工作效率。

5.本实用新型的上述技术问题主要是通过下述技术方案得以解决的:

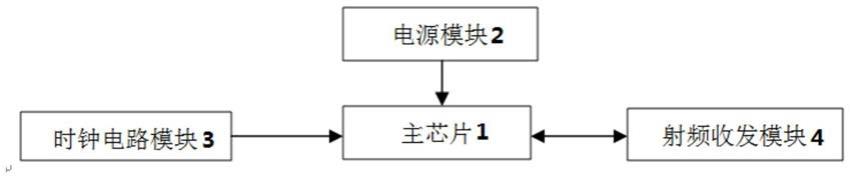

6.一种lora无线模块,所述无线模块包括主芯片、电源模块、时钟电路模块和射频收发模块;电源模块输出端连接主芯片输入端,时钟电路模块输出端连接主芯片输入端,射频收发模块与主芯片交互连接;所述主芯片集成了mcu和lora的功能;所述电源模块包括电源内部电路和电源外部电路;所述射频收发模块包括发射链路、接收链路和高频开关,发射链路和接收链路通过高频开关隔离。使用集成了mcu+lora功能的stm32wle5jb型号的单片机作为主芯片,提高了模块的集成度,简化了芯片之间的引脚连接设计,优化了电路布局,降低了设计成本,同时在射频收发电路采用了发射和接收链路通过高频开关隔离的方式,提高电路灵敏度和功率,从而提升了无线射频模块的工作效率。

7.作为优选,所述射频收发模块包括射频收发电路、射频发送电路、高频开关、射频接收电路、无线传输电路,射频收发电路输出端连接射频发送电路的输入端,射频发送电路的输出端连接高频开关的输入端,高频开关的输出端连接射频接收电路的输入端,射频接收电路的输出端连接射频收发电路,高频开关与无线传输电路交互连通。本射频回路原则是以效率为优先,尽可能平衡功率与电流参数,让模块的整体功耗尽可能降低,采用了发射和接收链路通过高频开关隔离的方式,减小两者相互影响,进而在不增加电流的基础上提高功率和灵敏度,从而提升效率。

8.作为优选,所述发射链路的电路包括直流电源vcc,双向tvs管,电感l10,直流射频电源vcc_rf;双向tvs管一端接地,双向tvs管的另一端接通直流电源vcc;电感l10一端接通直流电源vcc,电感l10另一端连接射频电源vcc_rf。tvs管用于吸收外部静电,减少对内部器件的损坏。

9.作为优选,所述电源外部电路使用磁珠吸附连接模块上的不同电源;从而达到抑制信号线、电源线上的高频噪声和尖峰干扰的效果。

10.作为优选,所述时钟电路模块包括射频时钟电路和mcu时钟电路;所述射频时钟电路包括电阻r9,电阻r8,晶振x2,电容c21,电容c22和电容c23;单片机xtb引脚连接电阻r9第一端,电阻r9第二端连接电容c21第一端,电容c21第二端接地,电阻r9的第二端与晶振x2的第一端连接,晶振x2的第二端与电容c22第一端连接,电容c22的第一端与电容c23第一端连接,电容c22的第二端接地,电容c23的第二端接地,电容c23的第一端与电阻r8的第一端连接,电阻r8的第二端连接主芯片的xta引脚。所述射频时钟电路采用32mhz无源晶振,常温下频偏10ppm,-40℃到85℃的频偏为

±

10ppm,该参数完全可以满足射频模块全温度范围下正常通信的需求;所述mcu时钟电路采用32.768hz的无源晶振,该无源晶振主要用来给mcu的低功耗串口lpuart1提供时钟,当mcu处于超低功耗stop状态时,无源晶振可正常工作;在stop状态下,若lpuart1接收到射频芯片的数据,则能唤醒mcu接收数据。

11.作为优选,所述射频时钟电路的无源晶振与主芯片间设置间隔距离,无源晶振与主芯片二者中心点间距离间隔9.4mm。主芯片使用低速率进行大数据包通信时,会产生较大的热量;无源晶振对温度变化敏感,因此在模块有限的空间范围内,不影响器件布局的前期下,尽量拉大射频无源晶振与主芯片之间的距离,减少主芯片发热带来的影响。

12.作为优选,所述无源晶振四周设置无敷铜空间,防止主芯片短时间产生的巨大热量通过敷铜传导至晶振,避免无源晶振受温度影响导致频偏变化。

13.作为优选,所述主芯片每个电源引脚均设置有对应的100nf去耦电容,去耦电容用作滤波,可以提高电源的稳定性。

14.本实用新型的上述技术问题主要是通过下述技术方案得以解决的:

15.本实用新型的有益效果是:

16.1.本方案采用的主芯片为stm32wle5jb,该芯片集成了mcu+lora功能,使用该芯片能同时实现mcu芯片+lora射频芯片的功能,极大的提高了模块的集成度,简化了芯片之间的引脚连接设计,优化了电路布局,提升了无线模块的整体效率。

17.2.在射频收发电路尽可能平衡功率与电流参数,降低模块整体功耗,同时采用了发射和接收链路通过高频开关隔离的方式,减小两者相互影响,进而在不增加电流的基础上提高功率和灵敏度,从而提升效率。

附图说明

18.图1为本实用新型的硬件模块连接图;

19.图2为本实用新型的射频电源电路发射链路末端电路图;

20.图3为本实用新型的射频时钟电路图;

21.图4为本实用新型射频收发电路流程框图;

22.图5为本实用新型的射频收发回路电路图。

23.图中:

24.1-主芯片;

25.2-电源模块;

26.3-时钟电路模块;

27.4-射频收发模块;41-射频收发电路;42-射频发送电路;43-高频开关;44-射频接收电路;45-无线传输电路。

具体实施方式

28.应理解,实施例仅用于说明本实用新型而不用于限制本实用新型的范围。此外应理解,在阅读了本实用新型讲授的内容之后,本领域技术人员可以对本实用新型作各种改动或修改,这些等价形式同样落于本技术所附权利要求书所限定的范围。

29.下面通过实施例,并结合附图,对本实用新型的技术方案作进一步具体的说明。

30.一种lora无线模块,所述无线模块包括主芯片1、电源模块2、时钟电路模块3和射频收发模块4;电源模块2输出端连接主芯片1输入端,时钟电路模块3输出端连接主芯片1输入端,射频收发模块4与主芯片1交互连接;所述主芯片1集成了mcu和lora的功能;所述电源模块2包括电源内部电路和电源外部电路;所述射频收发模块4包括发射链路、接收链路和高频开关,发射链路和接收链路通过高频开关隔离。

31.所述主芯片1采用stm32wle5jb单片机,该单片机集成了mcu+lora功能,而且内部集成了lora射频芯片,具有高达22dbm的发射功率和0.7ua的休眠功耗,提升了芯片的整体效率和整体水平,简化了芯片的引脚连接,提高了该无线模块的集成度,所述主芯片每个电源引脚均设置有对应的100nf去耦电容,去耦电容用作滤波。

32.所述电源模块2分为电源内部电路和电源外部电路;所述电源内部电路采用dc-dc和ldo协同的方式供电,芯片内部的数字处理部分采用ldo供电,在发射过程等需要大电流的状态下主要使用dc-dc供电,芯片内部的pa系统采用dc-dc供电。所述电源外部电路采用

一颗磁珠连接模块上不同电源,来抑制信号线、电源线上的高频噪声和尖峰干扰。在15dbm功率下,发送电流可以降低到34ma,接收电流从原来12ma降低到7ma;相比于sx127x芯片,在相同功率下,功耗降低约43%,功耗效率得到提高。

33.所述射频收发模块4包括射频收发电路41、射频发送电路42、高频开关43、射频接收电路44、无线传输电路45,射频收发电路41将信号传递给射频发送电路42,射频发送电路42连接高频开关43,高频开关43连接射频接收电路44,射频接收电路44连通射频收发电路41。所述射频收发模块4的发射链路和接收链路通过高频开关43隔离;所述发射链路末端设置了一颗tvs管,用于吸收外部静电;所述发射链路电路包括直流电源vcc,tvs管,电感l10,直流射频电源vcc_rf;tvs管一端接地,tvs管的另一端接通直流电源vcc;电感l10一端接通直流电源vcc,电感l10另一端连接射频电源vcc_rf。射频回路原则是以效率为优先,尽可能平衡功率与电流参数,从而减小功率,采用了发射和接收链路通过高频开关隔离的方式,减小发射链路和接收链路对彼此的影响。

34.所述时钟电路模块3包括射频时钟电路和mcu时钟电路;所述射频时钟电路采用32mhz无源晶振,常温下频偏10ppm,-40℃到85℃的频偏为

±

10ppm,该参数完全可以满足射频模块全温度范围下正常通信的需求,该晶振的x1、x2引脚连接分别到主芯片的xta和xtb引脚,这两个引脚内部自带可通过软件配置的匹配电容,使用上更加灵活,同时可减少外围元器件数量;所述mcu时钟电路采用32.768hz的无源晶振,该无源晶振主要用来给mcu的低功耗串口lpuart1提供时钟,当mcu处于超低功耗stop状态时,无源晶振可正常工作;在stop状态下,若lpuart1接收到射频芯片的数据,则能唤醒mcu接收数据。

35.射频时钟电路的射频芯片使用低速率进行大数据包通信时,会产生较大的热量;因为无源晶振对温度变化敏感,因此设计时考虑在模块有限的空间范围内,不影响器件布局的前期下,尽量拉大射频无源晶振与主芯片之间的距离,减少主芯片发热带来的影响,晶振与主芯片二者中心点的距离为9.4 mm;同时围绕晶振四周,开辟一块无敷铜空间。该方式避免了主芯片短时间产生的巨大热量通过敷铜传导至晶振,避免晶振受温度影响导致频偏变化。

36.本实用新型一颗主芯片1实现的功能与2颗芯片(mcu+lora)实现的功能一致,在电路集成度方面高,有利于降低成本和模块体积。同时本方案的整体设计以功耗效率为优先。例如:sx127x lora模块在15dbm发射时电流大约60ma,其功耗效率为25%。本方案在发射15dbm时发射电流为34ma,其功耗效率为44%。两者功耗效率进行对比,本方案的功耗效率提升较之前接近76%,站在客户的角度,使用1年的电池可以延长到使用1.8年,成本将会得到大大降低。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1