一种适用于DSP处理平台的数据链系统的帧结构及通信方法与流程

一种适用于dsp处理平台的数据链系统的帧结构及通信方法

技术领域

1.本发明属于通信系统设计领域,具体涉及一种适用于dsp处理平台的数据链系统的帧结构及通信方法。

背景技术:

2.数据链系统一般通过时分多址和频分多址方案实现网络中多个节点之间的时频资源划分。时分多址通过将时间划分成不同级别的时间单元,例如周期性的帧,每个帧划分多个时隙,每个时隙可进一步划分为子时隙,每个用户或者节点占用一个或多个时隙,实现不同用户或节点间的时域资源共享和通信;频分多址则是通过跳频技术实现不同用户或节点占据不同的频带,实现多个用户或节点频域资源共享和通信。时分多址和频分多址可以有效提高信道的利用率,实现较高的保密性和较大容量的数据传输。

3.数据链的帧结构中一般包含同步字段,用于实现对接收信号的正确捕获。现有数据链的帧头设计一般要求接收机需要采用滑动相关等捕获算法,该方法适用于采用fpga的实现方式。对于信号带宽要求较高的数据链系统,该设计不适用于采用dsp处理平台的接收系统设计中。因此,目前急需一种能够适用于dsp处理平台的数据链系统的帧结构。

技术实现要素:

4.本发明的目的在于提供一种适用于dsp处理平台的数据链系统的帧结构及通信方法,用以解决现有数据链的帧结构无法适用于dsp处理平台的数据链系统,无法满足高信号带宽的数据链系统的要求的问题。

5.为实现上述目的,本发明的技术方案为:

6.一种适用于dsp处理平台的数据链系统的帧结构,包括若干时隙,每个时隙包括1个同步子时隙、1个信令子时隙以及若干数据子时隙,所述同步子时隙用于发送用于同步的调制符号序列,所述信令子时隙发送调制阶数、数据长度、编码码率等相关的信令消息,所述数据子时隙发送用户待传输的数据信息。

7.进一步地,作为优选技术方案,所述同步子时隙包括三段相同的同步序列。

8.进一步地,作为优选技术方案,所述同步子时隙由三段相同的同步序列级联构成,每段同步序列采用伪随机序列产生,用于实现快速信号捕获、频偏估计及确定同步初始位置。

9.进一步地,作为优选技术方案,所述数据子时隙包括数据段和导频段,所述数据段用于携带要传输的信息,所述导频段用于实时估计和跟踪信道信息,所述数据子时隙的个数根据系统中节点通信速率进行配置。

10.进一步地,作为优选技术方案,所述数据子时隙还包括用于抵抗多径延时的循环前缀、循环后缀,所述循环前缀、所述循环后缀的长度可灵活配置。

11.进一步地,作为优选技术方案,所述循环前缀设置于所述导频段内,用于消除信道多径引入的符号间干扰,所述循环后缀设置于所述导频段与所述数据段之间。

12.进一步地,作为优选技术方案,所述时隙之间设有保护间隔,用于确保网络内远近节点在一个时隙内都能接收到完整的时隙数据,且保护间隔的长度根据实际应用中节点之间的距离进行配置。

13.进一步地,作为优选技术方案,所述同步子时隙、所述信令子时隙以及所述数据子时隙均设有子时隙头和子时隙尾保护段,用于支持跳频切换时间。

14.一种适用于dsp处理平台的数据链系统的帧结构的通信方法,包括如下步骤:

15.编码:对传输信号进行编码;

16.加扰:扰码序列产生可以跟节点号关联,实现编码序列和扰码序列的加扰;

17.交织:实现多个子时隙数据之间的映射,当编码后的比特不是交织块的整数倍,需要对序列进行填充,使填充后的比特数为交织块的整数倍;

18.调制:对交织后的信号进行调制;系统可支持bpsk、qpsk、gmsk等多种调制方式,数据信息、导频信息、同步信息采样相同的调制方式;

19.组帧:实现同步子时隙和多个数据子时隙级联组成帧的过程;

20.上采样:根据系统配置,对组帧后的数据进行变采样率上采样;

21.上变频:将上采样后的变频至相应频率;

22.下变频:将接收信号下变频到基带处理;

23.信号捕获:利用同步序列与本地信号的相关处理实现信号的捕获,并确定同步起始位置的过程;

24.信道估计:利用本地导频信号对接收信号处理,恢复出信道响应的过程;

25.匹配滤波:利用估计的信道响应对接收信号进行解卷积过程,消除信道对信号的影响;

26.精同步:利用本地导频信号对接收信号进行处理,确定同步起始位置最佳采样点的过程;

27.解调:利用精同步后的信号,抽取对应数据子时隙数据,计算输出硬判决比特或者比特对数似然比的过程;

28.解交织:从解调输出恢复交织前的原始发送信息顺序的过程;

29.解扰:利用扰码对解调对数似然比进行处理,恢复原始比特极性的过程;

30.译码:通过译码算法,从解调对数似然比恢复出发送比特序列的过程。

31.进一步地,作为优选技术方案,所述组帧包括数据子时隙中导频的产生、导频段添加cp、导频段和信息段级联完成数据子时隙的调制过程,包括同步子时隙数据的调制过程,包括同步子时隙和数据子时隙的级联过程。

32.本发明相对于现有技术,具有如下有益效果:

33.(1)本发明通过将同步子时隙设计为三段相同的序列并通过级联构成,能够快速实现信号捕获、频偏估计及确定同步初始位置,同时,由于采用了这样的帧结构设计,接收机可以采用大步进调整的相关方式进行信号捕获,从而避免了逐点滑动相关的捕获方式对处理器实时处理能力的高要求,且复杂度低,能够极大地满足dsp处理平台的接收系统的要求。

34.(2)本发明通过在数据子时隙中设计独立的导频段,用于实时估计和跟踪信道估计响应,同时设计长度可变的循环前缀和循环后缀,一来能够在不同应用场景下更好地估

计和跟踪信道信息,二来还能消除信道多径引入的符号间干扰。

35.(3)本发明通过设计子时隙头和子时隙尾,可支持不同跳频速率的需求和切换。

36.(4)本发明通过在时隙之间设有保护间隔,能够在不同应用场景下确保远近节点都能接收到完整时隙信息。

37.(5)本发明中,各数据段长度采用参数化设计,更灵活地支持不同带宽、不同传输速率、不同跳频速率、不同传输效率的需求。

附图说明

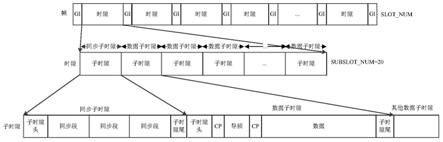

38.图1为本发明的整体结构示意图;

39.图2为本发明的同步子时隙结构示意图;

40.图3为本发明的数据子时隙结构示意图;

41.图4为数据链系统的收发流程图。

具体实施方式

42.下面结合实施例及附图,对本发明作进一步的详细说明,但本发明的实施方式不限于此。

43.实施例1

44.如图1、图2所示,本实施例所示的一种适用于dsp处理平台的数据链系统的帧结构,包括若干时隙,每个时隙包括1个同步子时隙、1个信令子时隙以及若干数据子时隙,同步子时隙用于发送用于同步的调制符号序列,信令子时隙发送调制阶数、数据长度、编码码率等相关的信令消息,数据子时隙发送用户待传输的数据信息。

45.时隙是帧结构中的基本通信配置单元,不同的通信节点可以分配一个或多个时隙,且时隙个数根据系统中节点个数进行灵活配置,每一个时隙包含多个子时隙,子时隙分为多种类型,包括同步子时隙、信令子时隙、数据子时隙等,同步子时隙发送用于同步的调制符号序列,信令子时隙发送调制阶数、数据长度、编码码率等相关的信令消息,数据子时隙发送用户待传输的数据信息。

46.优选的,本实施例的同步子时隙包括三段相同的同步序列,也叫同步段,三段相同的同步序列级联构成,每段同步序列采用伪随机序列产生,用于实现快速信号捕获、频偏估计及确定同步初始位置。

47.本实施例通过采用上述设计的帧结构,即将同步子时隙设计为三段相同的序列并通过级联构成,能够快速实现信号捕获、频偏估计及确定同步初始位置,同时,由于采用了这样的帧结构设计,接收机可以采用大步进调整的相关方式进行信号捕获,从而避免了逐点滑动相关的捕获方式对处理器实时处理能力的高要求,且复杂度低,能够极大地满足dsp处理平台的接收系统的要求。另外,可以通过适当增加同步段长度,提高频率估计的精度。本实施例中,同步子时隙的长度跟系统带宽、符号速率有关。

48.实施例2

49.如图3所示,本实施例在实施例1的基础上,将数据子时隙设计为数据段和导频段,数据段用于携带要传输的信息,导频段用于实时估计和跟踪信道信息,数据子时隙的个数根据系统中节点通信速率进行配置,数据子时隙的长度跟系统带宽、符号率等有关。

50.优选的,在数据子时隙设计用于抵抗多径延时的循环前缀、循环后缀(简称cp),循环前缀、循环后缀的长度可灵活配置。

51.进一步地,本实施例的循环前缀设置于导频段内,用于消除信道多径引入的符号间干扰,循环后缀设置于导频段与数据段之间。

52.实施例3

53.本实施例在实施例2的基础上,在时隙之间设有保护间隔,用于确保网络内远近节点在一个时隙内都能接收到完整的时隙数据,且保护间隔的长度可根据实际应用中节点之间的距离进行配置。

54.优选的,为了更好地实现跳频切换,满足不同的跳频速率需求,本实施例在同步子时隙、信令子时隙以及数据子时隙均设有子时隙头和子时隙尾保护段(简称gi),用于支持跳频切换时间。

55.如图4所示,下面给出一种数据链系统的通信过程说明,以更好地理解本发明。

56.数据链系统发射端包括传输的信息比特编码、加扰、交织、调制、组帧、上采样等过程,具体如下:

57.编码:对传输信号进行编码,可选择的编码方案有turbo编码或ldpc编码;

58.加扰:扰码序列产生可以跟节点号关联,实现编码序列和扰码序列的加扰;

59.交织:实现多个子时隙数据之间的映射,当编码后的比特不是交织块的整数倍,需要对序列进行填充,使填充后的比特数为交织块的整数倍。交织按交织块进行;

60.调制:对交织后的信号进行调制;系统可支持bpsk、qpsk、gmsk等多种调制方式。数据信息、导频信息、同步信息采样相同的调制方式;

61.组帧:实现同步子时隙和多个数据子时隙级联组成帧的过程,组帧包括数据子时隙中导频的产生、导频段添加cp、导频段和信息段级联完成数据子时隙的调制过程,包括同步子时隙数据的调制过程,包括同步子时隙和数据子时隙的级联过程;

62.上采样:根据系统配置,对组帧后的数据进行变采样率上采样;

63.上变频:将上采样后的变频至相应频率。

64.接收端经过下变频、下采样、信号捕获、频偏估计、信道估计、匹配滤波、精同步、解调、解交织、解扰、译码恢复出发送信息,具体如下:

65.下变频:将接收信号下变频到基带处理;

66.信号捕获:利用同步序列与本地信号的相关处理实现信号的捕获,并确定同步起始位置的过程;

67.信道估计:利用本地导频信号对接收信号处理,恢复出信道响应的过程;

68.匹配滤波:利用估计的信道响应对接收信号进行解卷积过程,消除信道对信号的影响;

69.精同步:利用本地导频信号对接收信号进行处理,确定同步起始位置最佳采样点的过程;

70.解调:利用精同步后的信号,抽取对应数据子时隙数据,计算输出硬判决比特或者比特对数似然比的过程;

71.解交织:从解调输出恢复交织前的原始发送信息顺序的过程;

72.解扰:利用扰码对解调对数似然比进行处理,恢复原始比特极性的过程;

73.译码:通过译码算法,从解调对数似然比恢复出发送比特序列的过程。

74.上述数据链系统采用turbo编码和gmsk调制。

75.虽然,上文中已经用一般性说明及具体实施例对本发明作了详尽的描述,但在本发明基础上,可以对之作一些修改或改进,这对本领域技术人员而言是显而易见的。因此,在不偏离本发明精神的基础上所做的这些修改或改进,均属于本发明要求保护的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1