减少分组时延的变化的物理层收发器的制作方法

减少分组时延的变化的物理层收发器

1.相关申请的交叉引用

2.本公开要求于2021年3月22日提交的共同未决、共同转让的美国临时专利申请号63/164,351的权益,该申请通过整体引用并入本文。

技术领域

3.本公开涉及一种其中减少了分组时延的变化的以太网物理层收发器。更具体地,本公开涉及一种以太网物理层收发器,其中可以将分组时延校准到已知值,从而减少时延变化并增强计算时延的能力。

背景技术:

4.本文提供的背景描述是为了一般地呈现本公开的上下文。本发明人的工作,就本背景部分中描述的工作以及在提交时可能不符合现有技术条件的描述方面而言,既不明确也不暗示承认为本公开主题的现有技术。

5.以太网物理层收发器(phy)包括连接到本地“主机”设备的物理编码子层(pcs)和连接到以太网信道的物理介质连接(pma)层。phy的这两个部分构成了以不同时钟速率操作的两个独立时钟域。例如,对于10gb以太网(10gbase-t),pcs时钟以312.5mhz操作,而pma时钟以800mhz操作。因为这两个时钟速率不是彼此的倍数,所以即使这两个时钟可能从一个公共时钟源中导出,这两个时钟的边沿也只是非常偶尔地重合。此外,两个不同时钟的边沿之间的间隔在这些场合之间也不断变化。在一种实现中,pcs和pma逻辑可以分别以312.5mhz和800mhz时钟的分频时钟速率运行的并行数据路径来操作。例如,pcs可以被设计为以两个并行数据路径来操作,每个数据路径的时钟速率为156.25mhz。

6.两个phy之间的以太网链路的训练包括建立分组穿越链路所经历的时延,这被反映在分组被接收链路伙伴phy接收时放置在分组上的时间戳与分组被源发链路伙伴phy传输时放置在分组上的时间戳之间的差异中。时延(如果已知的话)可以通过调整时间戳来计算。但是,由于分组起源于一个phy的312.5mhz pcs时域中,并最终落在另一个phy的312.5mhz pcs时域中,因此由于上面讨论的原因,时延可能会因跨时域边界的时延变化而发生变化。由于这种时延变化,可能难以确定所需的时间戳调整。此外,即使时延变化可以被确定,如果其中一个或两个phy被复位,则时延变化也可能会改变。因此,很难计算跨时域边界的分组时延,因为时延变化使得很难知道所需的时延校正是什么。

技术实现要素:

7.根据本公开主题的实现,一种减少物理层收发器的时钟域之间的数据传送中的时延变化的影响的方法,该物理层收发器包括具有在第一时钟域中的第一时钟的物理编码子层电路系统、和具有在第二时钟域中的第二时钟的物理介质连接电路系统,包括:在链路的初始训练期间,确定从第一时钟域到第二时钟域的传输方向上的传输时延值;在链路的初始训练期间,与确定传输时延值分开地确定从第二时钟域到第一时钟域的接收方向上的接

收时延值;并且使用传输时延值和接收时延值,来计算在初始训练之后直到后续训练之前、在第一时钟域和第二时钟域之间的数据传送中的时延。

8.在这种方法的第一实现中,确定在传输方向上的传输时延值可以包括:同时复位第一时钟和第二时钟,并且以第一时钟和第二时钟之一的预定周期开始将数据从第一时钟域传送到第二时钟域。

9.根据该第一实现的第一方面,以第一时钟和第二时钟之一的预定周期开始将数据从第一时钟域传送到第二时钟域可以包括:以第二时钟的预定周期开始将数据从第一时钟域传送到第二时钟域。

10.在这种方法的第二实现中,确定接收方向上的接收时延值可以包括:在检测到接收数据帧的同时复位第一时钟。

11.根据该第二实现的第一方面,检测到接收数据帧可以包括帧开始信号的恢复。

12.在这种方法的第三实现中,确定在接收方向上的接收时延值可以包括:检测接收数据帧的开始,识别从第一时钟和第二时钟的最近同时复位、到接收数据帧的开始已经经过的第一时钟的单位间隔数目,并检索与单位间隔数目相对应的已存储的时延值作为接收时延值。

13.根据该第三实现的第一方面,检索可以包括使用该数目作为索引从查找表中检索接收时延值。

14.该第一方面的第一实例可以还包括:在检测之前,在校准操作中建立查找表。

15.在该第一实例的第一变型中,校准操作可以包括:当在第一时钟的多个单位间隔中的每个单位间隔中接收到数据帧时,分开测量接收时延。

16.在该第一实例的第二变型中,校准操作可以包括:模拟在第一时钟的多个单位间隔中的每个单位间隔中的数据帧的接收,以及模拟对多个单位间隔中的每个单位间隔中的接收时延的测量。

17.在这种方法的第四种实现中,确定在传输方向上的传输时延值可以包括:在第一时钟和第二时钟对准处建立同步脉冲,以及将传输帧边界与同步脉冲对准以固定传输时延值。

18.在这种方法的第五实现中,确定在接收方向上的接收时延值可以包括:在第一时钟和第二时钟对准处建立同步脉冲,并且计数从同步脉冲到接收帧边界的时间间隔数目作为传输时延值。

19.在这种方法的第六实现中,使用传输时延值和接收时延值来计算在第一时钟域和第二时钟域之间的数据传送中的时延可以包括:调整在第一时钟域和第二时钟域之间传送的数据分组的时间戳。

20.根据本公开主题的实现,一种物理层收发器,包括:物理编码子层电路系统和物理介质连接电路系统,该物理编码子层电路系统被配置用于在主机设备和物理介质连接电路系统之间传送数据,并且该物理介质连接电路系统被配置用于在物理编码子层电路系统和信道介质之间传送数据;以及时钟和控制电路系统,其被配置为向物理编码子层电路系统和物理介质连接电路系统提供时钟标准,该时钟标准被转换为用于物理编码子层电路系统的第一时钟域的第一时钟、和用于物理介质连接电路系统的第二时钟域的第二时钟,该时钟和控制电路系统还被配置为通过以下方式减少第一时钟域和所述第二时钟域之间的数

据传送中的时延变化的影响:在链路的初始训练期间,确定从第一时钟域到第二时钟域的传输方向上的传输时延值;在链路的初始训练期间,确定从第二时钟域到第一时钟域的接收方向上的接收时延值;并且使用传输时延值和接收时延值来计算在所述初始训练之后直到后续训练之前在第一时钟域和第二时钟域之间的数据传送中的时延。

21.在这种物理层收发器的第一实现中,时钟和控制电路系统可以被配置为通过同时复位第一时钟和第二时钟来确定传输方向上的传输时延值,并以第一时钟和第二时钟之一的预定周期开始将数据从第一时钟域传送到第二时钟域。

22.根据该第一实现的第一方面,时钟和控制电路系统可以被配置为:通过以第二时钟的预定周期开始将数据从第一时钟域传送到第二时钟域,来以第一时钟和第二时钟之一的预定周期开始将数据从第一时钟域传送到第二时钟域。

23.在这种物理层收发器的第二实现中,时钟和控制电路系统可以被配置为:通过在检测到接收数据帧的同时复位第一时钟来确定接收方向上的接收时延值。

24.根据该第二实现的第一方面,时钟和控制电路系统还可以包括时钟数据恢复电路系统,该时钟数据恢复电路系统被配置为在检测到接收数据帧时恢复帧开始信号。

25.在这种物理层收发器的第三实现中,时钟和控制电路系统可以被配置为通过以下方式确定在接收方向上的接收时延值:检测接收数据帧的开始,识别从第一时钟和第二时钟的最近同时复位、到接收数据帧的开始已经经过的第一时钟的单位间隔数目,并且检索与单位间隔数目相对应的已存储的时延值作为接收时延值。

26.根据该第三实现的第一方面,时钟和控制电路系统可以被配置为使用该数目作为索引从查找表中检索接收时延值。

27.根据该第三实现的第二方面,时钟和控制电路系统可以被配置为在校准操作中建立查找表。

28.在该第二方面的第一实例中,时钟和控制电路系统可以被配置为通过以下方式建立查找表:测量在第一时钟的多个单位间隔中的每个单位间隔中接收到数据帧时的接收时延,并且在查找表中存储多个单位间隔中的每个单位间隔的所测量的接收时延。

29.在该第二方面的第二实例中,时钟和控制电路系统可以被配置为通过以下方式建立查找表:模拟在第一时钟的多个单位间隔的每个单位间隔中的数据帧的接收,模拟针对多个单位间隔中的每个单位间隔的接收时延的测量,并且在查找表中存储针对多个单位间隔中的每个单位间隔的模拟的所测量的接收时延。

30.在这样的物理层收发器的第四实现中,时钟和控制电路系统可以被配置为通过以下方式确定传输方向上的传输时延值:在第一时钟和第二时钟对准处建立同步脉冲,并且将传输帧边界与同步脉冲对准以固定传输时延值。

31.在这种物理层收发器的第五实现中,时钟和控制电路系统可以被配置为:通过以下方式确定接收方向上的接收时延值:在第一时钟和第二时钟对准处建立同步脉冲,并且计数从同步脉冲到接收帧边界的时间间隔数目作为传输时延值。

32.在这种物理层收发器的第六实现中,时钟和控制电路系统可以被配置为:通过使用传输时延值和接收时延值来调整在初始训练之后直到后续训练之前在第一时钟域和第二时钟域之间传送的数据分组的时间戳,计算第一时钟域和第二时钟域之间的数据传送中的时延,以减少在第一时钟域和第二时钟域之间的数据传送中的时延变化的影响。

附图说明

33.在结合附图考虑以下详细描述后,本公开的另外的特征、其性质和各种优点将是显而易见的,其中相同的附图标记自始至终指代相同的部分,并且其中:

34.图1是根据本公开主题的实现的物理层收发器的简化框图;

35.图2图示了在跨时钟域边界的数据帧的出口或传输期间时延变化如何被引入;

36.图3图示了在跨时钟域边界的数据帧的入口或接收期间时延变化如何被引入;

37.图4是图示了根据本公开主题的第一实现的定时图;

38.图5是图示了根据本公开主题的第二实现的定时图;和

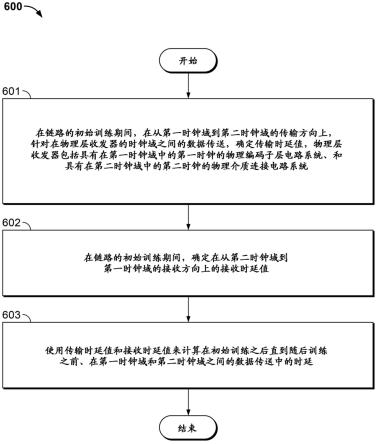

39.图6是图示了根据本公开主题的实现的方法的流程图。

具体实施方式

40.如上面所指出,两个phy之间的以太网链路的训练包括建立分组穿越链路所经历的时延,这被反映在当分组被接收链路伙伴phy接收时放置在分组上的时间戳、与分组被源发链路伙伴phy传输时放置在分组上的时间戳之间的差异中。但是,由于分组起源于一个phy的312.5mhz pcs时域中,并最终落在另一个phy的312.5mhz pcs时域中,因此由于上面讨论的原因,时延可能会因跨时域边界的时延变化而发生变化。此外,即使时延变化可以被确定,并且因此时延可以被确定,如果其中一个或两个phy被复位,则时延变化可能会改变。由于分组时延变化,因此很难计算分组时延。

41.根据本公开的主题的实现,可以通过分别处理传输时延和接收时延来计算分组时延变化。

42.在传输方向上,pcs 312.5mhz时钟和pma 800mhz时钟都在本地phy的控制下,并锁定在一起。有多种方法来生成被锁定在一起的312.5mhz和800mhz时钟。例如,可以使用更高频率(例如3.2ghz)的主时钟源,并且所生成的时钟输出可以用时钟分频器或状态机逻辑来进行分频,以提供312.5mhz和800mhz的平均时钟频率。在这种情况下,312.5mhz时钟和800mhz时钟之间的时钟边沿关系在固定数目的时钟周期之后重复。特别地,预计这两个时钟将在800mhz时钟的每256个周期对准一次。800mhz时钟的每256个周期可以生成一次同步脉冲(“sync_pulse”)。因此,如果传输数据帧边界的位置被建立并与该同步脉冲对准,则只要sync_pulse和传输数据帧边界的对准被重新建立,时域边界交叉对传输分组时延的贡献就将保持不变——即使在断电/通电周期或硬件复位周期。然而,虽然对时延的贡献是恒定的,但是它可能不是0,而是可能高达0.3125ns,因为312.5mhz pcs时钟的不规则性。然而,本地时域边界交叉对传输数据时延的贡献可能是已知的,从而减少了时延变化。

43.确定接收方向上的时延更复杂,因为时延变化可能受到本地phy以及远程链路伙伴phy两者的影响。例如,接收方向上的时延变化可以包括诸如本地phy的800mhz时钟和远程链路伙伴phy的800mhz时钟之间的相位差(其在某些实现中可能高达1.25ns)之类的分量,以及远程链路伙伴phy和本地phy中的时钟域交叉的影响(对于具有312.5mhz时钟的单个数据路径pcs,其在每个phy处贡献高达3.2ns的时延)。对于具有312.5mhz时钟的单个数据路径pcs,总时延变化可以高达3.2+3.2+1.25+0.3125=7.96ns。在具有2x数据路径pcs的其他实现中,总时延变化可以高达6.4+6.4+1.25+0.3125=14.36ns。

44.根据第一实现,在传输侧,通过总是在312.5mhz pcs时钟和800mhz pma时钟具有

恒定的固定相位关系(例如,上述sync_pulse位置)的点处释放复位或重启硬件,并且由于lpdc帧总是在硬件被重启之后的800mhz pma时钟的第一周期开始,因此可以在时域边界交叉处建立恒定的固定时延。在接收侧,根据第一实现,在检测到接收到的ldpc帧的开始时重启312.5mhz pcs时钟生成逻辑。312.5mhz pcs时钟的这个重启将确保pcs时钟和pma时钟具有恒定的固定相位关系。在这种对准之后,从pma时钟域中的ldpc帧的开始到pcs时钟域中的数据的开始的时钟域交叉时延然后固定在链路连接的每次复位上。

45.根据第二实现,在接收侧,对于pma时钟的每个单位间隔(例如,800mhz pma时钟的256个单位间隔,持续时间为320ns的ldpc帧),经由实际测量或经由模拟来收集时延值,并且这些时延值被存储在例如查找表中。当检测到针对接收帧的帧开始(sof)或“rx blip”信号时,“rx blip”和下一个sync_pulse之间的间隔被识别并被用作检索已存储的时延值的索引,其被用作从那个点到下一个时钟复位事件的时延值。这个时延值可以被用于补偿,也可以通过固定时间戳调整来进行校准。

46.因此,由于减少或消除了时延变化,因此减少或消除了每次新帧到达时对确定时延的需要,并且先前确定的时延值可以被用于时延补偿(例如,使用时间戳调整)。

47.可以通过参考图1-图6更好地理解本公开的主题。

48.图1是在其中可以实现本公开的主题的phy 100的简化框图。phy 100包括在111处与本地“主机”设备(未示出)通信的物理编码子层(pcs)电路系统模块101,以及在112处与有线信道介质(例如,以太网电缆;未示出)通信的物理介质连接电路系统模块102。

49.pcs电路系统模块101至少包括控制电路系统121、编码/解码电路系统131和协议逻辑电路系统141,它们对在主机设备和pma电路系统模块102之间双向流动的数据进行操作。

50.pma电路系统模块102包括接收路径122、传输路径132和时钟/控制块142。时钟/控制块142至少包括控制电路系统143和时钟源144。时钟源144,例如可以作为锁相环(pll),可以为整个phy 100提供主时钟,该主时钟可以在pcs电路系统模块101和pma电路系统模块102中的每一个中被直接使用或被分频(例如,以提供800mhz和312.5mhz时钟,如上所述)。

51.传输路径132可以相对直截了当,具有滤波器,诸如前馈均衡器(ffe)133和数模转换器134,以将所传输的信号驱动到信道介质上。

52.接收路径122至少包括采样器123、模数转换器124和均衡器125,其输出并行馈送数字定时环路(dtl)单元126和数据决策单元127,其可以包括滤波器,诸如例如在这个特定实现中为决策反馈均衡器(dfe)。接收路径122由来自锁相环(pll)144的800mhz时钟来提供时钟。dtl单元126将定时信息提供回pll 144以用于时钟数据恢复,并允许采样保持被锁定。

53.图2示出了在传输路径132中的跨时钟域边界200的低密度奇偶校验码(ldpc)帧的数据的出口或传输期间时延变化如何被引入。在附图中,312.5mhz时钟域被识别为“clk312”,而800mhz时钟域被识别为“clk800”。64位数据201(例如,使用ieee 802.3标准中描述的64b/65b编码202)被编码成65位块。65位块的这些连续流被“成帧”成50个65位块203,占用156.25mhz时钟(312.5mhz时钟除以2)的50个单位间隔,在总持续时间为320ns上延伸。数据经由成帧器/编码器块204跨过边界200而被计时输出(clock out),该块204包括fifo缓冲器和桶形移位器(均被示出)以及辅助位和奇偶校验位插入逻辑(均未示出)。成帧

器/编码器204从50个65b块重构占用200mhz时钟(800mhz时钟除以4)的64个单位间隔的ldpc帧,在总持续时间为320ns上延伸。当数据经由成帧器/编码器204的fifo缓冲器跨过边界200时,它根据312.5mhz时钟被计时输入(clock in)到fifo缓冲器中,但是根据800mhz时钟从fifo缓冲器中被计时输出,其边沿与312.5mhz时钟的边沿具有变化的关系,如上面所指出。时钟边沿关系在成帧器/编码器204中被确定,它还定义了50个65b块的帧开始(sof)。结果,除非根据本发明的主题的实现进行校正,否则取决于两个时钟的边沿的相对位置,不同的数据块将在成帧器/编码器204的fifo内花费不同的持续时间之后离开成帧器/编码器204的fifo,从而导致时延变化并引起数据中的中断。

54.类似地,在接收路径122中的入口或接收侧,如图3中所示,从传入数据流中形成320ns ldpc帧301,其占用200mhz时钟(800mhz时钟除以4)的64个单位间隔,sof检测可以是rx blip。该ldpc帧经由解帧器/解码器302的fifo缓冲器跨过边界200而被计时输入,并被重构为50个65位块303,占用156mhz时钟(312.5mhz时钟除以2)的50个单位间隔,在总持续时间为320ns上延伸。65位数据(例如,使用64b/65b解码304)被解码成64位数据305。当数据经由解帧器/解码器302的fifo缓冲器跨过边界200时,它根据800mhz时钟被计时输入到解帧器/解码器302的fifo缓冲器中,但是根据312.5mhz时钟从解帧器/解码器302的fifo缓冲器中被计时输出,其边沿与800mhz时钟的边沿具有变化的关系,如上面所指出。与出口路径的情况一样,从连续传入数据流中形成lpdc帧,以及两个时钟的时钟边沿关系在解帧器/解码器302中被确定。结果,除非根据本公开的主题的实现进行校正,否则取决于两个时钟的边沿的相对位置,不同的数据块将在解帧器/解码器302的fifo缓冲器内花费不同的持续时间之后离开解帧器/解码器302的fifo缓冲器,从而导致时延变化并引起数据中的中断。

55.根据本公开的主题的实现,通过将传输(出口)方向中的时延变化的贡献与接收(入口)方向上的时延变化的贡献区别对待,可以在每次链路被训练时——例如在上电时或在硬件复位之后——计算时延变化。

56.在传输(出口)方向上,312.5mhz时钟和800mhz时钟都在传输phy本地。因此,对于3.2ghz的主时钟,如果两个时钟同时被复位,则它们的边沿将被对准并且总是在大约320ns之后重新对准(312.5mhz时钟的100个单位间隔和800mhz时钟的256个单位间隔)。因此,可以通过同时复位两个时钟来在传输端最小化对时延变化的贡献,但是在一些实现中,312.5mhz时钟中的不规则性可能会导致来自传输端的高达0.3125ns的时延变化的贡献。然而,即使存在时延,时延量也是已知的,没有变化。

57.接收(入口)方向更复杂。接收器pma模块与远程传输器pma模块位于同一时钟域中——即信道的时钟域——因此两个pma时钟在一个单位间隔内被对准(即,在800mhz时在1.25ns内)。但是,远程传输器pcs模块处的312.5mhz时钟与接收器pcs模块的312.5mhz时钟跨过两个时钟域边界,这可能会引起大约6.4ns的时延。具体来说,对于具有2x数据路径的pcs实现,所产生的时延变化可能高达上述156.25mhz时钟(312.5mhz时钟除以2)的一个单位间隔,即,对于每个边界交叉,大约6.4ns,对于总的可能时延变化为12.8ns。

58.在传输方向上的第一实现中,通过总是在312.5mhz pcs时钟和800mhz pma时钟(或sync_pulse)的恒定的固定相位关系点处释放复位或重启成帧器/编码器204,并且由于ldpc帧总是在时钟开始之后的800mhz pma时钟的第一周期开始,因此在50个65b块的第一数据到ldpc帧的sof的时域边界交叉处建立恒定的固定时延。在接收方向上,检测到接收到

的ldpc帧的开始被用作触发器以复位312.5mhz pcs时钟,同时保持800mhz pma时钟运行。ldpc帧同步信号或“帧开始(sof)”或“blip信号”可以例如在链路训练期间从接收到的信号中恢复,例如通过pcs 101中的协议逻辑电路系统141。由于这两个时钟与blip信号的对准而被确定的时延贡献保持不变。在随后的复位事件或断电/上电周期中,可以重复此复位操作以允许时延贡献被确定和固定,消除时延变化。

59.在接收方向上的第二实现中,针对800mhz pma时钟的每个单位间隔,通过测量或通过模拟来确定时延值。即,对于检测到的每个blip信号,(通过测量“rx blip”和同步脉冲之间的800mhz pma时钟间隔的数目)测量来自312.5mhz pcs时钟和800mhz pma时钟最近对准的时延。在初始blip信号检测上进行该确定。在ldpc帧的持续时间内,为800mhz pma时钟的每个单位间隔确定时延值,即256个单位间隔。256个时延值被存储在例如查找表中,并且在运行时间期间,在检测blip信号时,识别256个可能性中的当前单位间隔,并从查找表中检索对应的时延值,从而通过将此时延变化信息提供给时间戳逻辑以相应地调整时间戳值来消除时延中的变化。

60.图4是图示了在传输和接收方向上的组合的第一实现的定时图。800mhz pma时钟401在410和420处与312.5mhz pcs时钟402对准,它们分别与分别基于接收到的ldpc帧412、422的相应ldpc帧blip信号411、421对准。在传输侧,pcs时钟域中的50个65b编码数据块403在每个时钟对准点之前所测量的固定时钟域交叉延迟(即,时延)的时间处被传输到成帧器/编码器204的fifo缓冲器中,以使得在所确定的交叉延迟404之后,所产生的传输ldpc帧422在时钟对准点420处开始。在接收侧,从那时开始,通过解帧器/解码器302的fifo缓冲器,从pma时钟域到pcs时钟域,每个接收到的ldpc帧根据定义开始于blip信号411、421并传播,以使得每个所产生的50个接收到的65b编码数据块组在从相应的时钟对准点420推延了所确定的交叉延迟405的时间处开始。

61.图5是图示了在接收方向上的第二实现的定时图。基于phy 100的加电,800mhz pma时钟501在510和520处与312.5mhz pcs时钟502对准。这固定了出口时延(未示出)的值,其类似于图4的出口时延404。传输侧的值的确定类似于第一实现(上面讨论过)。在接收侧,接收ldpc帧530和540,并且分别基于接收到的ldpc帧530、540来恢复对应的相应ldpc帧blip信号511、521。当blip信号511、521被恢复时,识别800mhz pma时钟501的256个周期中的对应周期(n=0,...,255)(在这种情况下,它是第四周期n=3)。(算出值n的一种方法是计数511、521的blip信号和上述sync_pulse之间的时钟间隔的数目。)从上述查找表中检索第n个延迟值,该表之前通过模拟或测量来填充,并且检索到的值在下一次复位之前被用作时间戳逻辑中的接收时延调整。传输和接收时延值在训练期间仅被确定一次,并在下一次复位之前被使用,并且因此没有时延变化。

62.一旦在每个方向上的时延值已被确定,并且已知具有很少变化或没有变化,则在跨时钟域边界传送数据时可以考虑它们(例如通过控制电路系统143)。如果时延已知,那么可能导致抖动或其他伪影的基于边界的任一侧上的时钟未对准的数据未对准可以被纠正(例如,通过调整数据分组上的时间戳)。

63.结合10gbps链路速度描述了上述实现。然而,在其他链路速度下的其他实现也是可能的,并且各种时钟速度值和时延值线性地缩放。因此,对于5gbps链路,pma时钟速度为400mhz,pcs时钟速度为156.25mhz,并且单位间隔和时延持续时间相应地缩放。即,帧持续

时间将为640ns,因为数据量相同但是所有时钟都以一半的速度运行,这也意味着时延量和任何时延变化都加倍。

64.根据本公开主题的实现的方法600在图6中被图示。方法600开始于601,其中,在链路的初始训练期间,在从第一时钟域到第二时钟域的传输方向上,针对在包括具有在第一时钟域中的第一时钟的物理编码子层电路系统和具有在第二时钟域中的第二时钟的物理介质连接电路系统的物理层收发器的时钟域之间的数据传送,确定传输时延值。

65.在602处,在链路的初始训练期间,在从第二时钟域到第一时钟域的接收方向上确定接收时延值。

66.在603处,当新的传输和接收时延值被确定时,传输时延值和接收时延值被用来计算在初始训练之后直到随后训练之前在第一时钟域和第二时钟域之间的数据传送中的时延(例如,通过在分组跨过时钟域边界时调整它们的时间戳,以计算所确定的接收时延值和/或传输时延值)。然后方法600结束。

67.因此,可以看出,通过将分组时延分别校准到传输和接收方向上的已知值,以太网物理层收发器中的减少的分组时延变化已被提供。

68.如本文和所附权利要求中使用的,构造“a和b之一”应该意指“a或b”。

69.需要注意的是,上述只是说明了本发明的原理,并且本发明可以通过所描述的实施例以外的方式来实践,这些实施例是为了说明而不是限制的目的而被呈现,并且本发明仅受以下权利要求的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1