一种信道编译码方法及装置与流程

本技术实施例涉及通信领域,尤其涉及一种信道编译码方法及装置。

背景技术:

1、目前,神经网络可以用于信道编译码。例如,采用卷积神经网络(convolutionalneural networks,cnn)或者循环神经网络(recurrent neural network,rnn)设计信道编译码。具体做法为:采用神经网络中已有的结构(例如,cnn或者rnn)分别作为编码(encoder)网络和译码(decoder)网络,实现信道编译码的功能。

2、以rnn为例,采用rnn的编译码的神经网络自编码器结构包括编码端和译码端,其中,编码端将待发送的比特序列作为rnn的时间步的输入,得到编码后的比特;译码端,也采用rnn结构,将接收到的信息输入rnn后恢复出比特序列。

3、其中,cnn或者rnn只能学习到编译码的局部结构,性能增益有限,而长短期记忆网络(long short-term memory networks,lstm)或者门控循环单元(gate recurrent unit,gru)等现代循环神经网络可以捕获比特序列中的长短期依赖关系,但是在编码过程中维太大,例如,在比特序列长度为k个比特时,维度为2的k次方,梯度链较长,因而梯度链的传输需要更多的时间步,可能导致梯度爆炸和梯度消失等问题。

技术实现思路

1、本技术提供一种信道编译码方法及装置,用以优化采用神经网络进行信道编译码的模型。

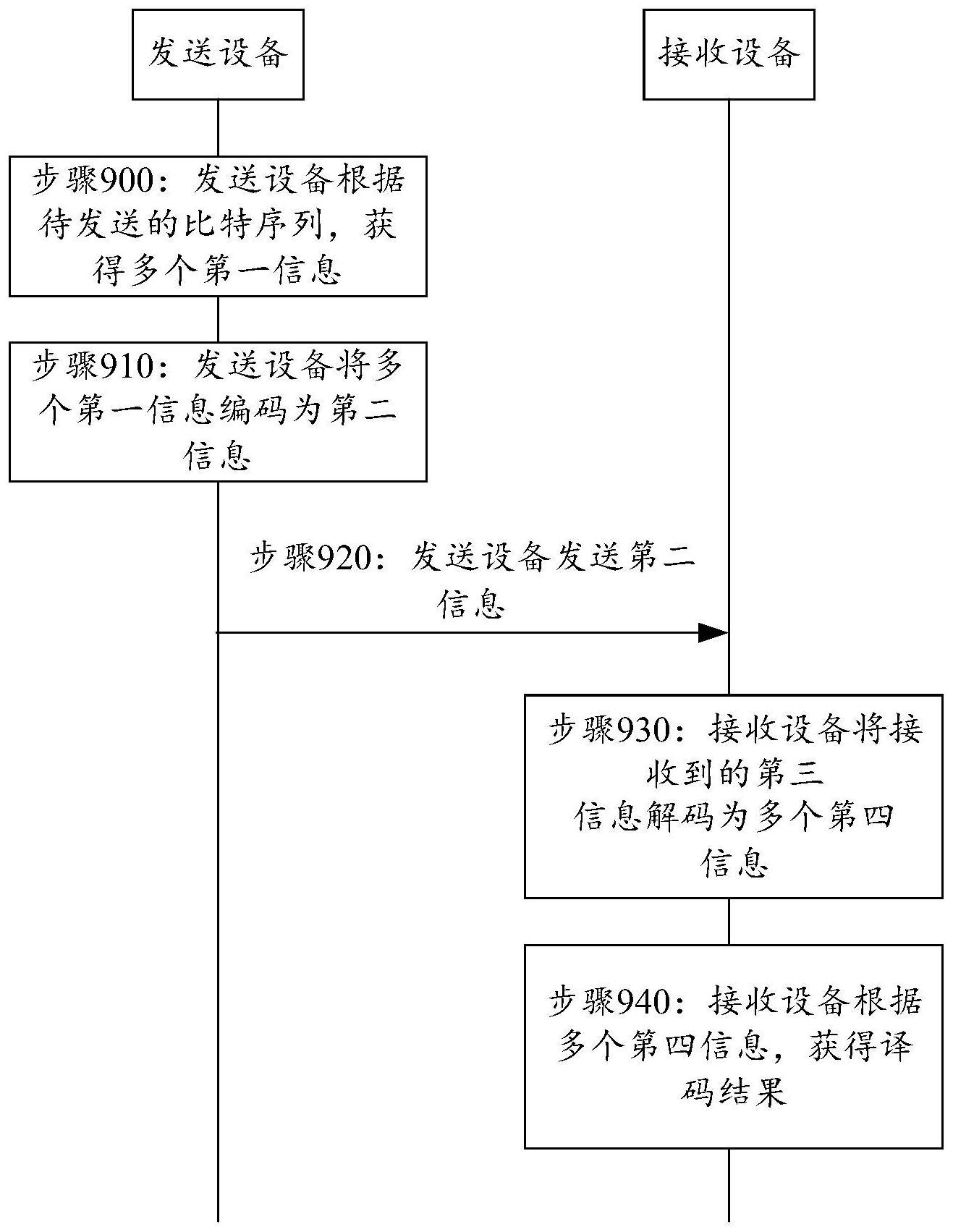

2、第一方面,本技术提供一种信道编译码方法,示例性地,该方法的执行主体为编码设备或发送设备或具有编码功能的装置,例如,芯片。该方法包括:根据待发送的比特序列,获得多个第一信息,其中,每个第一信息包括多维时间步特征,所述多维时间步特征是根据所述比特序列中的多个比特确定的,第i个第一信息包括的多维时间步特征所对应的多个比特与第i+1个第一信息包括的多维时间步特征所对应的多个比特部分相同,i为正整数;将所述多个第一信息编码为第二信息;发送所述第二信息。

3、采用上述方法,由于第i个第一信息包括的多维时间步特征所对应的多个比特与第i+1个第一信息包括的多维时间步特征所对应的多个比特部分相同,根据待发送的比特序列获得多个第一信息可以实现获得比特序列中各个比特的局部依赖关系,通过将多个第一信息编码为第二信息可以获得比特序列中各个比特的全部依赖关系。因此可以减轻了编码负担,不容易导致梯度爆炸和梯度消失等问题,且可以提升中长序列的编码性能,降低编码模型的训练难度。

4、在一种可能的设计中,在根据待发送的比特序列,获得多个第一信息时,将待发送的比特序列按照预设步长和预设分组大小,执行时间步特征提取操作,获得多个第一信息,其中,所述时间步提取操作通过神经网络运算实现。

5、示例性地,发送设备可以根据预设步长和预设分组大小,将待发送的比特序列确定为多个比特组,每个比特组包括的预设分组大小个比特,相邻比特组中包括部分相同的比特。进一步地,发送设备对每个比特组包括的比特执行时间步特征提取操作,获得相应的多维时间步特征,作为每个比特组对应的第一信息。

6、采用上述设计,对待发送的比特序列按照预设步长和预设分组大小进行分组,通过神经网络运算执行时间步特征提取操作,由于相邻比特组中包括部分相同的比特,可以实现获得待发送的比特序列中各个比特的局部依赖关系。

7、在一种可能的设计中,所述比特序列包括k个比特,k为正整数;在根据待发送的比特序列,获得多个第一信息时,将所述k个比特补充s个比特,获得k+s个比特,其中,s为正整数,将获得的k+s个比特按照预设步长和预设分组大小,执行时间步特征提取操作,获得多个第一信息,其中,所述时间步提取操作通过神经网络运算实现。

8、采用上述设计,对待发送的比特序列,补充部分比特,按照预设步长和预设分组大小进行分组,通过神经网络运算执行时间步特征提取操作,由于相邻比特组中包括部分相同的比特,可以实现获得补充后的比特序列中各个比特的局部依赖关系。

9、在一种可能的设计中,所述神经网络为卷积神经网络或全连接神经网络。可以理解的是,这里的神经网络还可以为其他类型的神经网络。

10、在一种可能的设计中,所述第一信息的数量为k;在将所述k个比特补充s个比特,获得k+s个比特时,将所述k个比特的首部和尾部各补充p个比特,获得k+2p个比特,其中,s=2p,p为正整数,首部补充的p个比特为第一预设序列,尾部补充的p个比特为第二预设序列;在将获得的k+s个比特按照预设步长和预设分组大小,执行时间步特征提取操作,获得多个第一信息时,将所述k+2p个比特按照步长为1和卷积核大小为2p+1,通过卷积神经网络获得k个第一信息。

11、其中,步长为1和滑窗大小为2p+1可以实现获得与待发送的比特序列的比特数量相同的第一信息。

12、在一种可能的设计中,所述第一信息的数量为k;在将所述k个比特补充s个比特,获得k+s个比特时,将所述k个比特的首部和尾部各补充p个比特,获得k+2p个比特,其中,s=2p,p为正整数,首部补充的p个比特为第一预设序列,尾部补充的p个比特为第二预设序列;在将获得的k+s个比特按照预设步长和预设分组大小,执行时间步特征提取操作,获得多个第一信息时,将所述k+2p个比特按照步长为1和滑窗大小为2p+1确定k个滑窗,根据所述k个滑窗,通过全连接神经网络获得k个第一信息。

13、在一种可能的设计中,所述全连接神经网络用于根据每个滑窗包括的2p+1个比特输出相应的多维时间步特征。

14、在一种可能的设计中,所述第一预设比特序列为全0序列,或者全1序列;所述第二预设比特序列为全0序列,或者全1序列。

15、第二方面,本技术提供一种信道编译码方法,示例性地,该方法的执行主体为译码设备或接收设备或具有译码功能的装置,例如,芯片。该方法包括:接收第三信息;将所述第三信息解码为多个第四信息,其中,每个第四信息包括多维时间步特征;根据所述多个第四信息,获得译码结果;每个第四信息包括的多维时间步特征对应所述译码结果中的多个比特,第i个第四信息包括的多维时间步特征所对应的多个比特与第i+1个第四信息包括的多维时间步特征所对应的多个比特部分相同,i为正整数。

16、采用上述方法,由于第i个第四信息包括的多维时间步特征所对应的多个比特与第i+1个第四信息包括的多维时间步特征所对应的多个比特部分相同,将接收到的第三信息解码为多个第四信息,根据多个第四信息,获得比特序列,能够提升译码成功率。

17、在一种可能的设计中,在根据所述多个第四信息,获得译码结果时,根据所述多个第四信息,按照预设步长和预设分组大小,获得所述译码结果。

18、在一种可能的设计中,在根据所述多个第四信息,按照预设步长和预设分组大小,获得所述译码结果时,根据所述多个第四信息,按照预设步长和预设分组大小,通过卷积神经网络获得译码结果。

19、在一种可能的设计中,在根据所述多个第四信息,按照预设步长和预设分组大小,获得所述译码结果时,根据所述多个第四信息,按照预设步长和预设分组大小,通过全连接神经网络获得译码结果。

20、在一种可能的设计中,所述第四信息的数量为k,所述译码结果包括k个比特,k为正整数。

21、第三方面,本技术提供一种信道译码方法,示例性地,该方法的执行主体为译码设备或接收设备或具有译码功能的装置,例如,芯片。该方法包括:接收信息1,根据所述信息1与多个噪声信号确定多个信息2,其中,所述多个噪声信号是根据信噪比确定的,根据所述多个信息2确定所述多个信息2分别对应的译码结果,根据所述多个信息2分别对应的译码结果确定所述信息1对应的比特序列。

22、采用上述设计,由于译码神经网络是通过带噪训练获得的,在较宽的信噪比区间下均有较好的性能,根据多个噪声信号分别对应的信息2可以通过译码神经网络获得多个噪声信号分别对应的译码结果,进而可以通过挑选正确码字提升误块率性能。

23、在一种可能的设计中,在接收信息1时,获取所述信噪比,根据所述信噪比确定所述多个噪声信号。

24、采用上述设计,通过接收信息1时获取信噪比,可以实现实时获得多个噪声信号。

25、在一种可能的设计中,在根据所述信息1与多个噪声信号确定多个信息2时,根据所述信息1与所述多个噪声信号中的每个噪声信号线性组合,获得相应的信息2。

26、在一种可能的设计中,在根据所述多个信息2确定所述多个信息2分别对应的译码结果时,通过译码神经网络对所述多个信息2进行译码,获得所述多个信息2分别对应的译码结果。

27、第四方面,一种信道编译码装置,该装置包括:处理单元,用于根据待发送的比特序列,获得多个第一信息,其中,每个第一信息包括多维时间步特征,所述多维时间步特征是根据所述比特序列中的多个比特确定的,第i个第一信息包括的多维时间步特征所对应的多个比特与第i+1个第一信息包括的多维时间步特征所对应的多个比特部分相同,i为正整数;将所述多个第一信息编码为第二信息;收发单元,用于发送所述第二信息。

28、在一种可能的设计中,所述处理单元,用于在根据待发送的比特序列,获得多个第一信息时,将待发送的比特序列按照预设步长和预设分组大小,执行时间步特征提取操作,获得多个第一信息,其中,所述时间步提取操作通过神经网络运算实现。

29、在一种可能的设计中,所述比特序列包括k个比特,k为正整数;所述处理单元,用于在根据待发送的比特序列,获得多个第一信息时,将所述k个比特补充s个比特,获得k+s个比特,其中,s为正整数;将获得的k+s个比特按照预设步长和预设分组大小,执行时间步特征提取操作,获得多个第一信息,其中,所述时间步提取操作通过神经网络运算实现。

30、在一种可能的设计中,所述神经网络为卷积神经网络或全连接神经网络。

31、在一种可能的设计中,所述第一信息的数量为k;所述处理单元,用于在将所述k个比特补充s个比特,获得k+s个比特时,将所述k个比特的首部和尾部各补充p个比特,获得k+2p个比特,其中,s=2p,p为正整数,首部补充的p个比特为第一预设序列,尾部补充的p个比特为第二预设序列;所述处理单元,用于在将获得的k+s个比特按照预设步长和预设分组大小,执行时间步特征提取操作,获得多个第一信息时,将所述k+2p个比特按照步长为1和卷积核大小为2p+1,通过卷积神经网络获得k个第一信息。

32、在一种可能的设计中,所述第一信息的数量为k;所述处理单元,用于在将所述k个比特补充s个比特,获得k+s个比特时,将所述k个比特的首部和尾部各补充p个比特,获得k+2p个比特,其中,s=2p,p为正整数,首部补充的p个比特为第一预设序列,尾部补充的p个比特为第二预设序列;所述处理单元,用于在将获得的k+s个比特按照预设步长和预设分组大小,执行时间步特征提取操作,获得多个第一信息时,将所述k+2p个比特按照步长为1和滑窗大小为2p+1确定k个滑窗;根据所述k个滑窗,通过全连接神经网络获得k个第一信息。

33、在一种可能的设计中,所述全连接神经网络用于根据每个滑窗包括的2p+1个比特输出相应的多维时间步特征。

34、在一种可能的设计中,所述第一预设比特序列为全0序列,或者全1序列;所述第二预设比特序列为全0序列,或者全1序列。

35、第五方面,本技术提供一种信道译码装置,该装置包括:收发单元,用于接收第三信息;处理单元,用于将所述第三信息解码为多个第四信息,其中,每个第四信息包括多维时间步特征;根据所述多个第四信息,获得译码结果;每个第四信息包括的多维时间步特征对应所述译码结果中的多个比特,第i个第四信息包括的多维时间步特征所对应的多个比特与第i+1个第四信息包括的多维时间步特征所对应的多个比特部分相同,i为正整数。

36、在一种可能的设计中,所述处理单元,用于在根据所述多个第四信息,获得译码结果时,根据所述多个第四信息,按照预设步长和预设分组大小,获得所述译码结果。

37、在一种可能的设计中,所述处理单元,用于在根据所述多个第四信息,按照预设步长和预设分组大小,获得所述译码结果时,根据所述多个第四信息,按照预设步长和预设分组大小,通过卷积神经网络获得所述译码结果。

38、在一种可能的设计中,所述处理单元,用于在根据所述多个第四信息,按照预设步长和预设分组大小,获得所述译码结果时,根据所述多个第四信息,按照预设步长和预设分组大小,通过全连接神经网络获得所述译码结果。

39、在一种可能的设计中,所述第四信息的数量为k,所述译码结果包括k个比特,k为正整数。

40、第六方面,本技术提供一种通信装置,该装置包括:收发单元,用于接收信息1;处理单元,用于根据所述信息1与多个噪声信号确定多个信息2,其中,所述多个噪声信号是根据信噪比确定的,根据所述多个信息2确定所述多个信息2分别对应的译码结果,根据所述多个信息2分别对应的译码结果确定所述信息1对应的比特序列。

41、在一种可能的设计中,处理单元,用于在接收信息1时,获取所述信噪比,根据所述信噪比确定所述多个噪声信号。

42、在一种可能的设计中,处理单元,用于在根据所述信息1与多个噪声信号确定所述多个信息2时,根据所述信息1与所述多个噪声信号中的每个噪声信号线性组合,获得相应的信息2。

43、在一种可能的设计中,处理单元,用于在根据所述多个信息2确定所述多个信息2分别对应的译码结果时,通过译码神经网络对所述多个信息2进行译码,获得所述多个信息2分别对应的译码结果。

44、上述第四方面至第六方面的技术效果可以参考第一方面至第三方面的相应的技术效果。

45、第七方面,本技术还提供一种装置。该装置可以执行上述方法设计。该装置可以是能够执行上述方法对应的功能的芯片或电路,或者是包括该芯片或电路的设备。

46、在一种可能的实现方式中,该装置包括:处理器,用于执行计算机程序或指令,当所述计算机程序或指令被执行时,使该装置或者安装有该装置的设备执行上述任意一种可能的设计中的方法。

47、在一种可能的实现方式中,该装置还可以包括通信接口,该通信接口可以是收发器,或者,如果该装置为芯片或电路,则通信接口可以是该芯片的输入/输出接口,例如输入/输出管脚等。

48、其中,该装置还可以包括:存储器,用于存储所述计算机程序或指令;所述存储器与所述处理器耦合。

49、在一种可能的设计中,该装置包括相应的功能单元,分别用于实现以上方法中的步骤。功能可以通过硬件实现,也可以通过硬件执行相应的软件实现。硬件或软件包括一个或多个与上述功能相对应的单元。

50、第八方面,本技术提供一种计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,当所述计算机程序在装置上运行时,执行上述任意一种可能的设计中的方法。

51、第九方面,本技术提供一种计算机程序产品,所述计算机程序产品包括计算机程序,当所述计算机程序在装置上运行时,执行上述任意一种可能的设计中的方法。

- 还没有人留言评论。精彩留言会获得点赞!