全双工发射接收电路、串行电路芯片、电子设备及车辆的制作方法

1.本发明涉及电子电器技术领域,特别是涉及一种全双工发射接收电路、串行电路芯片、电子设备及车辆。

背景技术:

2.serdes(serializer-deserializer,串行器和解串器)是一种在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(比如光纤、同轴电缆等)后,在接收端高速串行信号重新转换成低速并行信号的通信技术。

3.目前,相关技术中串行器和解串器之间一般是单向通道,没有回传功能,比如hdmi(high definition multimedia interface,高清晰度多媒体接口)和lvds(low voltage differential signaling,低电压差分信号)。即便有部分协议通过增设额外的信道来回传控制信息,比如dp(display port,显示接口),但这种方式会增加成本,不利于广泛应用,具有局限性。

技术实现要素:

4.基于此,有必要针对上述缺陷或不足,提供一种全双工发射接收电路、串行电路芯片、电子设备及车辆,能够在单通道上实现全双工通信。

5.第一方面,本发明实施例提供了一种基于pam4架构的全双工发射接收电路,所述全双工发射接收电路包括发射模块、提取模块和接收模块,所述发射模块为四级脉冲放大调制架构;

6.所述发射模块的第一端与所述提取模块的第一端连接,所述发射模块的第二端与所述提取模块的第二端连接,所述提取模块的第三端与所述接收模块的第一端连接,所述提取模块的第四端与所述接收模块的第二端连接;

7.所述发射模块被配置为发射混合差分信号,所述混合差分信号包括正向高速差分信号和反向低速差分信号;

8.所述提取模块被配置为从所述混合差分信号中提取出反向低速差分信号分量,并将所述反向低速差分信号分量输出至所述接收模块。

9.可选的,在本发明一些实施例中,所述提取模块包括转换单元和计算单元;

10.所述转换单元的第一端连接所述发射模块的第一端,所述转换单元的第二端连接所述发射模块的第二端,所述转换单元的第三端分别与所述计算单元的第一端、所述计算单元的第二端和所述接收模块的第一端相连接,所述转换单元的第四端分别与所述计算单元的第三端、所述计算单元的第四端和所述接收模块的第二端相连接,所述计算单元的第五端连接所述发射模块的第三端,所述计算单元的第六端连接所述发射模块的第四端,所述计算单元的第七端连接所述发射模块的第五端,所述计算单元的第八端连接所述发射模块的第六端;

11.所述转换单元被配置为将所述混合差分信号转换为正向高速差分信号分量和所

述反向低速差分信号分量后输出至所述计算单元;

12.所述计算单元被配置为将所述正向高速差分信号分量和所述反向低速差分信号分量中的所述正向高速差分信号分量去除,得到所述反向低速差分信号分量。

13.可选的,在本发明一些实施例中,所述转换单元包括第一电阻、第二电阻、第一场效应管、第二场效应管、第一电流源、第三电阻和第四电阻;

14.所述第一电阻的第一端连接所述发射模块的第一端,所述第一电阻的第二端连接所述第一场效应管的第一端,所述第二电阻的第一端连接所述发射模块的第二端,所述第二电阻的第二端连接所述第二场效应管的第一端,所述第一场效应管的第二端分别与所述第三电阻的第一端、所述计算单元的第一端和所述计算单元的第二端相连接,所述第一场效应管的第三端连接所述第一电流源的第一端,所述第一电流源的第二端接地,所述第三电阻的第二端连接电源,所述第二场效应管的第二端分别与所述第四电阻的第一端、所述计算单元的第三端和所述计算单元的第四端相连接,所述第二场效应管的第三端连接所述第一电流源的第一端,所述第四电阻的第二端连接电源。

15.可选的,在本发明一些实施例中,所述计算单元包括第三场效应管、第四场效应管、第二电流源、第五场效应管、第六场效应管和第三电流源;

16.所述第三场效应管的第一端连接所述转换单元的第三端,所述第三场效应管的第二端连接所述发射模块的第三端,所述第三场效应管的第三端连接所述第二电流源的第一端,所述第二电流源的第二端接地,所述第四场效应管的第一端连接所述转换单元的第四端,所述第四场效应管的第二端连接所述发射模块的第四端,所述第四场效应管的第三端连接所述第二电流源的第一端,所述第五场效应管的第一端连接所述转换单元的第三端,所述第五场效应管的第二端连接所述发射模块的第五端,所述第五场效应管的第三端连接所述第三电流源的第一端,所述第三电流源的第二端接地,所述第六场效应管的第一端连接所述转换单元的第四端,所述第六场效应管的第二端连接所述发射模块的第六端,所述第六场效应管的第三端连接所述第三电流源的第一端。

17.可选的,在本发明一些实施例中,所述发射模块包括第七场效应管、第五电阻、第六电阻、第八场效应管、第九场效应管、第七电阻、第八电阻、第十场效应管、第十一场效应管、第九电阻、第十电阻、第十二场效应管、第十三场效应管、第十一电阻、第十二电阻和第十四场效应管;

18.所述第七场效应管的第一端连接电源,所述第七场效应管的第二端接入第一路子正向高速差分信号,所述第七场效应管的第三端连接所述第五电阻的第一端,所述第五电阻的第二端分别与所述第六电阻的第一端和所述发射模块的第一端相连接,所述第六电阻的第二端连接所述第八场效应管的第一端,所述第八场效应管的第二端连接所述第七场效应管的第二端,所述第八场效应管的第三端接地,所述第九场效应管的第一端连接电源,所述第九场效应管的第二端接入第二路子正向高速差分信号,所述第九场效应管的第三端连接所述第七电阻的第一端,所述第七电阻的第二端分别与所述第八电阻的第一端和所述发射模块的第一端相连接,所述第八电阻的第二端连接所述第十场效应管的第一端,所述第十场效应管的第二端连接所述第九场效应管的第二端,所述第十场效应管的第三端接地,

19.所述第十一场效应管的第一端连接电源,所述第十一场效应管的第二端接入第三路子正向高速差分信号,所述第十一场效应管的第三端连接所述第九电阻的第一端,所述

第九电阻的第二端分别与所述第十电阻的第一端和所述发射模块的第二端相连接,所述第十电阻的第二端连接所述第十二场效应管的第一端,所述第十二场效应管的第二端连接所述第十一场效应管的第二端,所述第十二场效应管的第三端接地,所述第十三场效应管的第一端连接电源,所述第十三场效应管的第二端接入第四路子正向高速差分信号,所述第十三场效应管的第三端连接所述第十一电阻的第一端,所述第十一电阻的第二端分别与所述第十二电阻的第一端和所述发射模块的第二端相连接,所述第十二电阻的第二端连接所述第十四场效应管的第一端,所述第十四场效应管的第二端连接所述第十三场效应管的第二端,所述第十四场效应管的第三端接地。

20.可选的,在本发明一些实施例中,所述第七场效应管、所述第九场效应管、所述第十一场效应管和所述第十三场效应管为pmos管,所述第八场效应管、所述第十场效应管、所述第十二场效应管和所述第十四场效应管为nmos管。

21.可选的,在本发明一些实施例中,所述接收模块包括滤波放大单元;

22.所述滤波放大单元的第一端连接所述提取模块的第三端,所述滤波放大单元的第二端连接所述提取模块的第四端;

23.所述滤波放大单元被配置为对所述反向低速差分信号分量进行滤波和放大。

24.第二方面,本发明实施例提供了一种串行电路芯片,所述串行电路芯片包括第一方面中任意一项所述的基于pam4架构的全双工发射接收电路。

25.第三方面,本发明实施例提供了一种电子设备,所述电子设备包括解串电路芯片、传输媒体以及第二方面所述的串行电路芯片,其中所述传输媒体设置在所述解串电路芯片与所述串行电路芯片之间。

26.第四方面,本发明实施例提供了一种车辆,所述车辆包括第三方面所述的电子设备。

27.从以上技术方案可以看出,本发明实施例具有以下优点:

28.本发明实施例所提供的全双工发射接收电路、串行电路芯片、电子设备及车辆,通过在四级脉冲放大调制电路架构的基础上增加提取模块和接收模块,进而该提取模块可以从发射模块发射的混合差分信号中提取出反向低速差分信号分量,并向接收模块输出,由此能够在单通道上实现全双工通信,结构简单,便于广泛应用,同时大幅降低了制造成本。

附图说明

29.通过阅读参照以下附图所作的对非限制性实施例所作的详细描述,本发明的其它特征、目的和优点将会变得更明显:

30.图1为本发明实施例提供的一种基于pam4架构的全双工发射接收电路的应用框图;

31.图2为本发明实施例提供的另一种基于pam4架构的全双工发射接收电路的应用框图;

32.图3为本发明实施例提供的一种pam4架构的示意图;

33.图4为本发明实施例提供的一种基于pam4架构的全双工发射接收电路的结构框图;

34.图5为本发明实施例提供的另一种基于pam4架构的全双工发射接收电路的结构框

图;

35.图6为本发明实施例提供的又一种基于pam4架构的全双工发射接收电路的结构框图;

36.图7为本发明实施例提供的一种基于pam4架构的全双工发射接收电路的具体示例;

37.图8为本发明实施例提供的一种串行电路芯片的结构框图;

38.图9为本发明实施例提供的一种电子设备的结构框图;

39.图10为本发明实施例提供的一种车辆的结构框图。

具体实施方式

40.为了使本技术领域的人员更好的理解本发明方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整的描述,显然,所描述的实施例仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

41.本发明的说明书和权利要求书及上述附图中的术语“第一”、“第二”、“第三”、“第四”等(如果存在)是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便描述的本发明的实施例能够以除了在这里图示或描述的那些以外的顺序实施。

42.此外,术语“包括”和“具有”以及它们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或模块的过程、方法、系统、产品或设备不必限于清楚的列出的那些步骤或模块,而是可包括没有清楚的列出的或对于这些过程、方法、产品或设备固有的其它步骤或模块。

43.为了便于更好的理解本发明,现结合图1和图2所示的应用框图进行说明。示例性的,本发明实施例提供的基于pam4(pulse amplitude modulation 4,四级脉冲放大调制)架构的全双工发射接收电路可以应用在stp(shielded twisted pair,屏蔽双绞线)传输模式或者coax(coaxial cable,同轴电缆)传输模式中,即发送端为serializer(串行器)电路,接收端为deserilalizer(解串器)电路,二者之间通过stp或者coax等传输媒体进行信号传输。其中,fc表示正向通道,fc_driver表示正向驱动,fc_receiver表示正向接收,rc表示反向通道,rc_driver表示反向驱动,rc_receiver表示反向接收,tx表示发送以及rx表示接收。

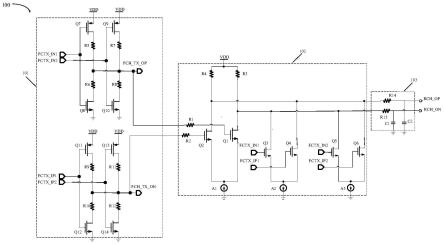

44.进一步的,如图3所示本发明实施例提供的pam4架构包括场效应管q01、电阻r01、电阻r02、场效应管q02、场效应管q03、电阻r03、电阻r04、场效应管q04、场效应管q05、电阻r05、电阻r06、场效应管q06、场效应管q07、电阻r07、电阻r08和场效应管q08。其中,场效应管q01的源极连接电源(vdd),场效应管q01的栅极通过端脚fctx_in1接入第一路子正向高速差分信号,场效应管q01的漏极连接电阻r01的第一端,电阻r01的第二端分别与电阻r02的第一端和芯片端脚fch_tx_op相连接,电阻r02的第二端连接场效应管q02的漏极,场效应管q02的栅极连接场效应管q01的栅极,场效应管q02的源极接地;场效应管q03的源极连接电源(vdd),场效应管q03的栅极通过端脚fctx_in2接入第二路子正向高速差分信号,场效应管q03的漏极连接电阻r03的第一端,电阻r03的第二端分别与电阻r04的第一端和芯片端

脚fch_tx_op相连接,电阻r04的第二端连接场效应管q04的漏极,场效应管q04的栅极连接场效应管q03的栅极,场效应管q04的源极接地。

45.而场效应管q05的源极连接电源(vdd),场效应管q05的栅极通过端脚fctx_ip1接入第三路子正向高速差分信号,场效应管q05的漏极连接电阻r05的第一端,电阻r05的第二端分别与电阻r06的第一端和芯片端脚fch_tx_on相连接,电阻r06的第二端连接场效应管q06的漏极,场效应管q06的栅极连接场效应管q05的栅极,场效应管q06的源极接地;以及,场效应管q07的源极连接电源(vdd),场效应管q07的栅极通过端脚fctx_ip2接入第四路子正向高速差分信号,场效应管q07的漏极连接电阻r07的第一端,电阻r07的第二端分别与电阻r08的第一端和芯片端脚fch_tx_on相连接,电阻r08的第二端连接场效应管q08的漏极,场效应管q08的栅极连接场效应管q07的栅极,场效应管q08的源极接地。

46.下面通过图4至图10详细地阐述本发明实施例提供的基于pam4架构的全双工发射接收电路、串行电路芯片、电子设备及车辆。

47.请参考图4,其为本发明实施例提供的一种基于pam4架构的全双工发射接收电路的结构框图,该全双工发射接收电路100包括发射模块101、提取模块102和接收模块103,该发射模块101为四级脉冲放大调制架构,比如图3所示。其中,发射模块101的第一端与提取模块102的第一端连接,发射模块101的第二端与提取模块102的第二端连接,而提取模块102的第三端与接收模块103的第一端连接,提取模块102的第四端与接收模块103的第二端连接。

48.示例性的,本发明实施例中全双工发射接收电路100首先通过发射模块101发射混合差分信号,该混合差分信号可以包括正向高速差分信号和反向低速差分信号,然后通过提取模块102从该混合差分信号中提取出反向低速差分信号分量,并将反向低速差分信号分量输出至接收模块103。因此,本发明实施例通过全双工发射接收电路100中发射模块101、提取模块102和接收模块103这三个组成模块,能够在单通道上实现全双工通信,结构简单,便于广泛应用,同时大幅降低了制造成本。

49.可选的,如图5所示,本发明一些实施例中提取模块102可以包括转换单元1021和计算单元1022,该转换单元1021配置用于将混合差分信号转换为正向高速差分信号分量和反向低速差分信号分量后输出至计算单元1022,而该计算单元1022配置用于将正向高速差分信号分量和反向低速差分信号分量中的正向高速差分信号分量去除,得到反向低速差分信号分量。其中,该转换单元1021的第一端连接发射模块101的第一端,该转换单元1021的第二端连接发射模块101的第二端,该转换单元1021的第三端分别与计算单元1022的第一端、计算单元1022的第二端和接收模块103的第一端相连接,该转换单元1021的第四端分别与计算单元1022的第三端、计算单元1022的第四端和接收模块103的第二端相连接,而该计算单元1022的第五端连接发射模块101的第三端,该计算单元1022的第六端连接发射模块101的第四端,该计算单元1022的第七端连接发射模块101的第五端,该计算单元1022的第八端连接发射模块101的第六端。

50.可选的,如图6所示,本发明一些实施例中接收模块103可以包括滤波放大单元1031,该滤波放大单元1031配置用于对反向低速差分信号分量进行滤波和放大。其中,该滤波放大单元1031的第一端连接提取模块102的第三端,该滤波放大单元1031的第二端连接提取模块102的第四端。

51.示例性的,请参考图7,下面对全双工发射接收电路100中各个组成模块或者单元的具体电路结构进行详细说明。

52.比如,提取模块102中转换单元1021可以包括但不限于第一电阻r1、第二电阻r2、第一场效应管q1、第二场效应管q2、第一电流源a1、第三电阻r3和第四电阻r4。其中,第一电阻r1的第一端(对应于提取模块102的第一端)连接发射模块101的第一端,第一电阻r1的第二端连接第一场效应管q1的第一端,第二电阻r2的第一端(对应于提取模块102的第二端)连接发射模块101的第二端,第二电阻r2的第二端连接第二场效应管q2的第一端,第一场效应管q1的第二端(对应于提取模块102的第三端)分别与第三电阻r3的第一端、计算单元1022的第一端和计算单元1022的第二端相连接,第一场效应管q1的第三端连接第一电流源a1的第一端,第一电流源a1的第二端接地,第三电阻r3的第二端连接电源(vdd),第二场效应管q2的第二端(对应于提取模块102的第四端)分别与第四电阻r4的第一端、计算单元1022的第三端和计算单元1022的第四端相连接,第二场效应管q2的第三端连接第一电流源a1的第一端,第四电阻r4的第二端连接电源(vdd)。

53.可选的,本发明实施例中第一场效应管q1和第二场效应管q2均为nmos管,则第一场效应管q1的第一端为nmos管的栅极(g),第一场效应管q1的第二端为nmos管的漏极(d),第一场效应管q1的第三端为nmos管的源极(s),以及第二场效应管q2的第一端为nmos管的栅极(g),第二场效应管q2的第二端为nmos管的漏极(d),第二场效应管q2的第三端为nmos管的源极(s)。

54.再如,提取模块102中计算单元1022可以包括但不限于第三场效应管q3、第四场效应管q4、第二电流源a2、第五场效应管q5、第六场效应管q6和第三电流源a3。其中,第三场效应管q3的第一端连接转换单元1021的第三端,第三场效应管q3的第二端连接发射模块101的第三端(fctx_in1),第三场效应管q3的第三端连接第二电流源a2的第一端,第二电流源a2的第二端接地;第四场效应管q4的第一端连接转换单元1021的第四端,第四场效应管q4的第二端连接发射模块101的第四端(fctx_ip1),第四场效应管q4的第三端连接第二电流源a2的第一端;第五场效应管q5的第一端连接转换单元1021的第三端,第五场效应管q5的第二端连接发射模块101的第五端(fctx_in2),第五场效应管q5的第三端连接第三电流源a3的第一端,第三电流源a3的第二端接地;以及,第六场效应管q6的第一端连接转换单元1021的第四端,第六场效应管q6的第二端连接发射模块101的第六端(fctx_ip2),第六场效应管q6的第三端连接第三电流源a3的第一端。

55.可选的,本发明实施例中第三场效应管q3、第四场效应管q4、第五场效应管q5和第六场效应管q6均为nmos管,则第三场效应管q3的第一端为nmos管的漏极(d),第三场效应管q3的第二端为nmos管的栅极(g),第三场效应管q3的第三端为nmos管的源极(s);第四场效应管q4的第一端为nmos管的漏极(d),第四场效应管q4的第二端为nmos管的栅极(g),第四场效应管q4的第三端为nmos管的源极(s);第五场效应管q5的第一端为nmos管的漏极(d),第五场效应管q5的第二端为nmos管的栅极(g),第五场效应管q5的第三端为nmos管的源极(s);以及,第六场效应管q6的第一端为nmos管的漏极(d),第六场效应管q6的第二端为nmos管的栅极(g),第六场效应管q6的第三端为nmos管的源极(s)。

56.又如,发射模块101可以包括第七场效应管q7、第五电阻r5、第六电阻r6、第八场效应管q8、第九场效应管q9、第七电阻r7、第八电阻r8、第十场效应管q10、第十一场效应管

q11、第九电阻r9、第十电阻r10、第十二场效应管q12、第十三场效应管q13、第十一电阻r11、第十二电阻r12和第十四场效应管q14。其中,第七场效应管q7的第一端连接电源(vdd),第七场效应管q7的第二端接入第一路子正向高速差分信号(通过fctx_in1端脚),第七场效应管q7的第三端连接第五电阻r5的第一端,第五电阻r5的第二端分别与第六电阻r6的第一端和发射模块101的第一端(fch_tx_op)相连接,第六电阻r6的第二端连接第八场效应管q8的第一端,第八场效应管q8的第二端连接第七场效应管q7的第二端,第八场效应管q8的第三端接地;第九场效应管q9的第一端连接电源(vdd),第九场效应管q9的第二端接入第二路子正向高速差分信号(通过fctx_in2端脚),第九场效应管q9的第三端连接第七电阻r7的第一端,第七电阻r7的第二端分别与第八电阻r8的第一端和发射模块101的第一端(fch_tx_op)相连接,第八电阻r8的第二端连接第十场效应管q10的第一端,第十场效应管q10的第二端连接第九场效应管q9的第二端,第十场效应管q10的第三端接地。

57.而第十一场效应管q11的第一端连接电源(vdd),第十一场效应管q11的第二端接入第三路子正向高速差分信号(通过fctx_ip1端脚),第十一场效应管q11的第三端连接第九电阻r9的第一端,第九电阻r9的第二端分别与第十电阻r10的第一端和发射模块101的第二端(fch_tx_on)相连接,第十电阻r10的第二端连接第十二场效应管q12的第一端,第十二场效应管q12的第二端连接第十一场效应管q11的第二端,第十二场效应管q12的第三端接地;以及,第十三场效应管q13的第一端连接电源(vdd),第十三场效应管q13的第二端接入第四路子正向高速差分信号(通过fctx_ip2端脚),第十三场效应管q13的第三端连接第十一电阻r11的第一端,第十一电阻r11的第二端分别与第十二电阻r12的第一端和发射模块101的第二端(fch_tx_on)相连接,第十二电阻r12的第二端连接第十四场效应管q14的第一端,第十四场效应管q14的第二端连接第十三场效应管q13的第二端,第十四场效应管q14的第三端接地。

58.可选的,本发明实施例中第七场效应管q7、第九场效应管q9、第十一场效应管q11和第十三场效应管q13均为pmos管,而第八场效应管q8、第十场效应管q10、第十二场效应管q12和第十四场效应管q14均为nmos管。此时,第七场效应管q7的第一端为pmos管的源极(s),第七场效应管q7的第二端为pmos管的栅极(g),第七场效应管q7的第三端为pmos管的漏极(d);第八场效应管q8的第一端为nmos管的漏极(d),第八场效应管q8的第二端为nmos管的栅极(g),第八场效应管q8的第三端为nmos管的源极(s);第九场效应管q9的第一端为pmos管的源极(s),第九场效应管q9的第二端为pmos管的栅极(g),第九场效应管q9的第三端为pmos管的漏极(d);第十场效应管q10的第一端为nmos管的漏极(d),第十场效应管q10的第二端为nmos管的栅极(g),第十场效应管q8的第三端为nmos管的源极(s)。

59.而第十一场效应管q11的第一端为pmos管的源极(s),第十一场效应管q11的第二端为pmos管的栅极(g),第十一场效应管q11的第三端为pmos管的漏极(d);第十二场效应管q12的第一端为nmos管的漏极(d),第十二场效应管q12的第二端为nmos管的栅极(g),第十二场效应管q12的第三端为nmos管的源极(s);以及,第十三场效应管q13的第一端为pmos管的源极(s),第十三场效应管q13的第二端为pmos管的栅极(g),第十三场效应管q13的第三端为pmos管的漏极(d);第十四场效应管q14的第一端为nmos管的漏极(d),第十四场效应管q14的第二端为nmos管的栅极(g),第十四场效应管q14的第三端为nmos管的源极(s)。

60.另如,接收模块103中滤波放大单元1031可以包括但不限于第十三电阻r13、第一

电容c1、第十四电阻r14和第二电容c2。其中,第十三电阻r13的第一端(对应于接收模块103的第一端)连接提取模块102的第三端,第十三电阻r13的第二端分别与第一电容c1的第一端和接收模块103的第一输出端(rch_on)相连接,第一电容c1的第二端接地,而第十四电阻r14的第一端(对应于接收模块103的第二端)连接提取模块102的第四端,第十四电阻r14的第二端分别与第二电容c2的第一端和接收模块103的第二输出端(rch_op)相连接,第二电容c2的第二端接地。

61.下面结合图7,对本发明实施例提供的全双工发射接收电路100的工作过程进行说明。首先,正向高速差分信号通过pam4架构电路输出到芯片端脚fch_tx_op和fch_tx_on上,同时该芯片端脚还会接收到从解串电路芯片端发送过来的反向低速差分信号;其次,将该芯片端脚上的混合差分信号通过第一电阻r1和第二电阻r2分别发送到第一场效应管q1的栅极和第二场效应管q2的栅极,由于第一场效应管q1和第二场效应管q2的漏极输出既有正向高速差分信号分量,还有反向低速差分信号分量,此时通过第三场效应管q3、第四场效应管q4、第五场效应管q5和第六场效应管q6将正向高速差分信号分量减去,得到只包含接收到的从解串电路芯片端发送过来的反向低速差分信号分量;进而,再通过第十三电阻r13、第一电容c1、第十四电阻r14和第二电容c2将恢复出来的反向低速差分信号分量进行滤波和放大处理,便可以实现全双工通信。

62.作为另一方面,本发明实施例还提供了一种串行电路芯片。如图8所示,该串行电路芯片200可以包括但不限于图3~图7对应实施例中的基于pam4架构的全双工发射接收电路100。

63.作为再一方面,本发明实施例还提供了一种电子设备。如图9所示,该电子设备300可以包括解串电路芯片301、传输媒体302以及图8对应实施例中串行电路芯片200。其中,传输媒体302设置在解串电路芯片301与串行电路芯片200之间,比如该传输媒体302可以为屏蔽双绞线或者同轴电缆等。

64.作为又一方面,本发明实施例还提供了一种车辆。如图10所示,该车辆400可以包括图9对应实施例中的电子设备300。

65.本发明实施例提供了一种基于pam4架构的全双工发射接收电路、串行电路芯片、电子设备及车辆,通过在四级脉冲放大调制电路架构的基础上增加提取模块和接收模块,进而该提取模块可以从发射模块发射的混合差分信号中提取出反向低速差分信号分量,并向接收模块输出,由此能够在单通道上实现全双工通信,结构简单,便于广泛应用,同时大幅降低了制造成本。

66.以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

67.以上实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1