一种时钟同步方法、装置、电子设备及存储介质与流程

1.本发明涉及信号处理领域,尤其涉及一种时钟同步方法、装置、系统及存储介质。

背景技术:

2.随着自动驾驶技术的不断发展,车载控制器的功能复杂度越来越高,现有的汽车电子电气架构逐步由分立向集中转换。现有的中央集中式方案架构,一般需要对视频数据、毫米波雷达数据、激光雷达数据等进行时钟同步处理,因此需要有较为稳定的时钟源作为参考时钟。为了提供稳定的时钟源,可以采用gps(global positioning system,全球定位系统)模块输出的1pps(1pulsepersecond,秒脉冲)信号在整个系统当中传输,利用其边沿作为系统各个模块的时钟同步参考。然而,由于中央集中式架构涉及自动驾驶域、智能座舱域、底盘控制域等多个功能域的模块或芯片,因此,1pps信号存在多单板、多芯片传输的场景,在上述场景下,传输过程的信号时延、信号损耗等因素均可能对系统的时钟信号同步产生不利影响。

3.现有方案通过对1pps信号自身在传输过程中产生的相位差进行识别及校准,虽然能够一定程度满足时钟信号的纠偏要求,但校准效率低,且时钟源可靠性不足。

技术实现要素:

4.针对现有技术存在的缺陷,本公开实施例提供一种时钟同步方法、装置、系统及存储介质,可以提高时钟信号的校准效率,并且保证时钟源的可靠性。

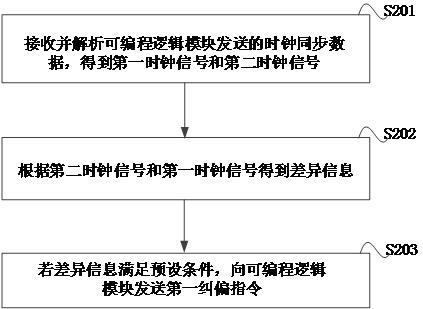

5.本技术实施例提供一种时钟同步方法,方法包括:接收并解析可编程逻辑模块发送的时钟同步数据,得到第一时钟信号和第二时钟信号;第一时钟信号和第二时钟信号用于互为备用地向多个时钟应用单元提供参考,以使多个时钟应用单元时钟同步;根据第二时钟信号和第一时钟信号得到差异信息;若差异信息满足预设条件,向可编程逻辑模块发送第一纠偏指令;第一纠偏指令用于指示可编程逻辑模块调整第二时钟信号,得到第一纠偏信号。

6.可选的,第二时钟信号由可编程逻辑模块将第一时钟信号后移一个周期得到;差异信息包括第一偏差值,第一偏差值表征第一时钟信号的第二个周期的上升沿和第二时钟信号的第一个周期的上升沿之间的偏差;若差异信息满足预设条件,向可编程逻辑模块发送第一纠偏指令,包括:若第一偏差值满足第一预设偏差条件,向可编程逻辑模块发送第一纠偏指令;第一纠偏指令包括第一偏差值。

7.可选的,若差异信息满足预设条件,向可编程逻辑模块发送第一纠偏指令之后,方法还包括:接收可编程逻辑模块发送的第一纠偏信号;根据第一时钟信号或第一纠偏信号,确定目标时钟信号;发送目标时钟信号至时钟应用模块。

8.可选的,根据第一时钟信号或第一纠偏信号,确定目标时钟信号,包括:根据第一时钟信号或第一纠偏信号,确定基准时钟信号;若检测到第一纠偏信号存在缺失周期,从基准时钟信号中确定补充时钟信号;补充时钟信号用于补充缺失周期上的信息;向可编程逻

辑模块发送信号补充指令;信号补充指令包括补充时钟信号,信号补充指令用于指示可编程逻辑模块根据补充时钟信号补充第一纠偏信号,得到目标补充信号;接收可编程逻辑模块发送的目标补充信号;根据第一时钟信号或目标补充信号,确定目标时钟信号。

9.可选的,根据第一时钟信号或第一纠偏信号,确定目标时钟信号,包括:根据第一时钟信号或第一纠偏信号,确定基准时钟信号;基于第一纠偏信号和基准时钟信号得到第二偏差值;第二偏差值表征第一纠偏信号的第二个周期的上升沿和基准时钟信号的第一个周期或者第二个周期的上升沿之间的偏差;若第二偏差值满足第二预设偏差条件,向可编程逻辑模块发送第二纠偏指令;第二纠偏指令包括第二偏差值,第二纠偏指令用于指示可编程逻辑模块根据第二偏差值调整第一纠偏信号,得到第二纠偏信号;接收可编程逻辑模块发送的第二纠偏信号;根据第一时钟信号或第二纠偏信号,确定目标时钟信号。

10.可选的,确定目标时钟信号之后,还包括:对目标时钟信号进行去抖、取均值操作,得到应用时钟信号。发送目标时钟信号至时钟应用模块,包括:发送应用时钟信号至时钟应用模块。

11.可选的,主控模块的数量为多个;时钟应用模块用于接收多个主控模块发送的多个目标时钟信号,根据时钟优先级从多个目标时钟信号中确定主用时钟信号。

12.相应地,本技术还提供一种时钟同步装置,装置包括:接收模块,用于接收并解析可编程逻辑模块发送的时钟同步数据,得到第一时钟信号和第二时钟信号;第一时钟信号和第二时钟信号用于互为备用地向多个时钟应用单元提供参考,以使多个时钟应用单元时钟同步;确定模块,用于根据第二时钟信号和第一时钟信号得到差异信息;发送模块,用于若差异信息满足预设条件,向可编程逻辑模块发送第一纠偏指令;第一纠偏指令用于指示可编程逻辑模块调整第二时钟信号,得到第一纠偏信号。

13.可选的,第二时钟信号由可编程逻辑模块将第一时钟信号后移一个周期得到;差异信息包括第一偏差值,第一偏差值表征第一时钟信号的第二个周期的上升沿和第二时钟信号的第一个周期的上升沿之间的偏差。发送模块还用于若第一偏差值满足第一预设偏差条件,向可编程逻辑模块发送第一纠偏指令;第一纠偏指令包括第一偏差值。

14.可选的,装置还包括应用模块,用于接收可编程逻辑模块发送的第一纠偏信号;根据第一时钟信号或第一纠偏信号,确定目标时钟信号;发送目标时钟信号至时钟应用模块。

15.可选的,确定模块还用于根据第一时钟信号或第一纠偏信号,确定基准时钟信号;若检测到第一纠偏信号存在缺失周期,从基准时钟信号中确定补充时钟信号;补充时钟信号用于补充缺失周期上的信息;向可编程逻辑模块发送信号补充指令;信号补充指令包括补充时钟信号,信号补充指令用于指示可编程逻辑模块根据补充时钟信号补充第一纠偏信号,得到目标补充信号;接收可编程逻辑模块发送的目标补充信号;根据第一时钟信号或目标补充信号,确定目标时钟信号。

16.可选的,确定模块还用于根据第一时钟信号或第一纠偏信号,确定基准时钟信号;基于第一纠偏信号和基准时钟信号得到第二偏差值;第二偏差值表征第一纠偏信号的第二个周期的上升沿和基准时钟信号的第一个周期或者第二个周期的上升沿之间的偏差;若第二偏差值满足第二预设偏差条件,向可编程逻辑模块发送第二纠偏指令;第二纠偏指令包括第二偏差值,第二纠偏指令用于指示可编程逻辑模块根据第二偏差值调整第一纠偏信

号,得到第二纠偏信号;接收可编程逻辑模块发送的第二纠偏信号;根据第一时钟信号或第二纠偏信号,确定目标时钟信号。

17.可选的,确定模块还用于,在确定目标时钟信号之后,对目标时钟信号进行去抖、取均值操作,得到应用时钟信号。发送模块还可以用于发送应用时钟信号至时钟应用模块。

18.可选的,主控模块的数量为多个;时钟应用模块用于接收多个主控模块发送的多个目标时钟信号,根据时钟优先级从多个目标时钟信号中确定主用时钟信号。

19.相应地,本公开实施例提供一种电子设备,电子设备包括处理器和存储器,存储器中存储有至少一条指令、至少一段程序、代码集或指令集,至少一条指令、至少一段程序、代码集或指令集由处理器加载并执行以实现上述的时钟同步方法。

20.相应地,本公开实施例提供一种计算机可读存储介质,存储介质中存储有至少一条指令、至少一段程序、代码集或指令集,至少一条指令、至少一段程序、代码集或指令集由处理器加载并执行以实现上述的时钟同步方法。

21.本技术实施例具有如下有益效果:(1)通过采用第一时钟信号为基准,对第二时钟信号进行反馈校准,可以提高时钟信号校准的效率和准确性;(2)通过将第一时钟信号后移一个周期得到第二时钟信号,无论是在第二时钟信号的相位向前偏移的情况下还是向后偏移的情况下,都可以方便地确定第一偏差值,并根据第一偏差值消除传输过程中产生的误差,从而精确地控制并调整第二时钟信号,使得后继主控模块接收得到的第一时钟信号的第二个上升沿和接收并解析得到的第二时钟信号的第一个上升沿保持同步或者控制在预设范围内;(3)通过对后移一个周期的第二时钟信号以以太网报文的形式发送,可以减少第二时钟信号在以太网转发、ad采样以及解码过程中造成的延时,从而保证第二时钟信号校准的准确性;(4)通过时钟信号的数字化处理以及多个主控模块的时钟互为备份,可以保证时钟源在整个中央计算平台的各个模块、各个单元之中保持稳定;(5)通过确定基准时钟信号,并根据基准时钟信号进行实时校验、查漏补缺,可以提高时钟信号校验的效率和准确率;(6)通过以太网、pcie、can总线等实现数据交互,在中央计算架构下,可以实现智能驾驶域、智能座舱域、地盘控制域的时钟同步以及跨域互通;(7)通过主控单元执行待处理数据在多个计算单元中的分发调度处理,能够实现计算单元在整个系统内的资源共享,并可以合理分配计算资源,从而提升系统算力的利用率;(8)第一时钟信号和第二时钟信号互为备份,并且多个主控模块确定的目标时钟信号互为备份,可以提高时钟源的可靠性。

附图说明

22.为了更清楚地说明本技术实施例或现有技术中的技术方案和优点,下面将对实施例或现有技术描述中所需要使用的附图作简单的介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,

还可以根据这些附图获得其它附图。

23.图1是本技术实施例所提供的一种时钟同步方法的应用场景示意图;图2是本技术实施例所提供的一种时钟同步方法的第一流程示意图;图3是本技术实施例所提供的一种时钟同步方法的第二流程示意图;图4是本技术实施例所提供的一种时钟同步方法的第三流程示意图;图5是本技术实施例所提供的一种时钟同步方法的第四流程示意图;图6a是本技术实施例所提供的一种时钟同步方法的第一模块结构示意图;图6b是本技术实施例所提供的一种时钟同步方法的第一信号波形示意图;图6c是本技术实施例所提供的一种时钟同步方法的第二模块结构示意图;图7是本技术实施例所提供的一种时钟同步方法的第二信号波形示意图;图8是本技术实施例所提供的一种时钟同步方法的第三模块结构示意图;图9是本技术实施例所提供的一种时钟同步装置的结构示意图;图10是本技术实施例所提供的一种时钟同步方法的服务器的硬件结构框图。

具体实施方式

24.为使本技术的目的、技术方案和优点更加清楚,下面将结合附图对本技术实施例作进一步地详细描述。显然,所描述的实施例仅仅是本技术一个实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有作出创造性劳动的前提下所获得的所有其他实施例,都属于本技术保护的范围。

25.此处所称的“实施例”是指可包含于本技术至少一个实现方式中的特定特征、结构或特性。在本技术实施例的描述中,需要理解的是,术语“上”、“下”、“左”、“右”、“顶”、“底”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置/系统或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含的包括一个或者更多个该特征。而且,术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的本技术实施例能够以除了在这里图示或描述以外的顺序实施。此外,术语“包括”和“具有”/“为”以及他们/其的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元/模块的过程、方法、系统/装置、产品或设备不必限于清楚地列出的那些步骤或单元/模块,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元/模块。

26.下面介绍本技术提供的一种时钟同步方法的示例性场景。

27.在一种可选的实施方式中,本技术的应用场景可以包括主控模块、时钟应用模块、可编程逻辑模块和gps模块中的至少一个。可选的,可编程逻辑模块可以包括fpga(field programmable gate array,现场可编辑阵列逻辑)模块;可选的,可编程逻辑模块还可以包括cpld(complex programmable logic device,复杂可编程逻辑器件)等其他可编程逻辑模块,本技术不对可编程逻辑模块作限定,在其他可选的实施方式中,可编程逻辑模块还可以其他具有可编程逻辑能力的模块。可选的,时钟应用模块可以包括算力模块,主控模块可

以接收并解析fpga模块发送的时钟同步数据,得到第一时钟信号和第二时钟信号;第一时钟信号和第二时钟信号用于互为备用地向多个算力模块提供参考,以使多个时钟应用单元时钟同步;根据第二时钟信号和第一时钟信号得到差异信息;若差异信息满足预设条件,向fpga模块发送第一纠偏指令;第一纠偏指令用于指示fpga模块调整第二时钟信号,得到第一纠偏信号。其中,fpga可以基于gps模块发送的时钟信号,确定第一时钟信号和第二时钟信号,并将上述的第一时钟信号和第二时钟信号发送至主控模块。

28.可选的,主控模块作为管理平面以及中央计算决策的核心模块,可以负责整个车辆中央计算平台的设备管理、故障侦测、算力单元计算结果的进一步分析运算,还可以负责针对pcie(peripheral component interconnect express,高速串行计算机扩展总线标准)数据、以太网数据、can(controller area network, 控制器局域网络)数据的转发与相应命令的数据互通等工作。可选的,主控模块具备cpu(central processing unit,中央处理器)模块、mcu (microcontroller unit,微控制单元)模块,可选分别作为ap(adaptive platform)中间件、cp(classic platform)中间件的硬件承载。其中cpu借助ap中间件,可选执行设备管理、数据分发、复杂决策功能的应用功能;mcu借助cp中间件,可选执行车控决策的控制,用于进一步与外部区控制器、车控执行单元进行命令下发等工作。

29.可选的,算力模块作为自动驾驶域的重要计算模块,可以具备深度学习、数据分析的npu(neural-network process units,嵌入式神经网络处理器)、gpu(graphics processing unit,图形处理器)、cpu、dsp(digital signal processing,数字信号处理)等资源。算力模块产出的计算结果可选传输至主控模块用于进一步的决策运算,主控模块可以下发命令至外部执行单元进行车控执行动作。

30.可选的,fpga模块可以用于将外部的感知数据,经过数据预处理,将原始或经过数据预处理的数据,通过pcie、以太网发送至主控模块中,并由主控模块分发至相对应的计算模块或座舱单元,以进行进一步的视频分析与数据运算。其中,感知数据可以包括摄像头、毫米波雷达、激光雷达等采集的数据。可选的,fpga模块可以接收gps模块下发的系统产生的时钟信号,该时钟信号可以是1pps时钟信号。fpga模块可以基于该时钟信号,生成数字化的以太网信息,并利用中央计算单元的tsn(time-sensitive network,时间敏感网络)以太网交换芯片,经过主控模块分发至各个算力模块当中。可选的,fpga模块还可以将上述的以太网信息发送到其他时钟应用模块,如座舱模块。

31.图1是本技术实施例提供的一种时钟同步方法的场景示意图。下面基于图1进一步阐述本技术提供的一种时钟同步方法的应用场景。该应用场景中,算力模块可以包括算力0、算力1、算力2、算力3、算力4、算力5、算力6、算力7,主控模块可以包括主控0、主控1,fpga模块可以包括fpga预处理模块0、fpga预处理模块1。

32.可选的,时钟同步方法的应用场景中还可以包括智能座舱模块。智能座舱模块一方面可选连接舱内摄像头进行座舱主要功能实现,另一方面可选通过主控模块将数据转发至算力模块进行dms(driver monitor system,驾驶员监测系统)等系统的复杂算法运算,相对应的运算结果可以经过主控模块回传至座舱模块,以使座舱模块可以基于运算结果进行进一步的显示操作与人机交互动作。

33.可选的,主控模块的数量可以是多个。在上述应用场景中,多个主控模块或者多个计算模块还可以分别以主从组网的形式组网,从而实现系统级的冗余备份。具体而言,多个

主控模块可以具有主控优先级顺序,其中优先级较低的模块可以作为优先级较高的模块的备用模块。

34.在一种可选的实施方式中,如图1所图示,主控0可以是优先级最高的主控模块。正常状态下,主控0可以通过数据通路与各个算力模块、座舱模块、fpga模块之间连接,并可以基于最高的主从优先级进行设备管理、数据分发、计算回传等操作。可选的,主控1的优先级可以低于主控0的优先级。主控1同样通过数据通路与上述各个模块之间进行备用通路数据互通。当主控0出现异常时,上述数据通路可以切换至主控1所在的备用数据通路,以通过采用系统级的功能安全冗余备份,进行实时的冗余备份切换,从而实现实时的热切换。

35.可选的,多个主控模块之间可以通过pcie、以太网进行数据同步、数据互通等交互,以确保多个主控模块实时保持同步。

36.可选的,各个模块之间可以通过背板、线缆、板对板连接器等形式进行数据互联互通。

37.可选的,应用场景中还可以包括电源模块,电源模块包括电源0、电源1。整个时钟同步系统可选采用双电源冗余备份,即采用电源1和电源0,以提供系统工作稳定性。

38.下面介绍本技术提供的一种时钟同步方法的示例性流程。图2是本技术实施例提供的一种时钟同步方法的第一流程示意图,本说明书提供了如实施例或流程图所示的方法或者流程操作步骤,但基于常规或者无创造性的劳动可以包括更多或者更少的操作步骤。实施例中列举的步骤顺序仅仅为众多执行顺序中的一种方式,不代表唯一的执行顺序,在实际执行时,可以按照实施例或者附图所示的方法或者流程顺执行序或者并行执行(例如并行处理器或者多线程处理的环境)。在一种可选的实施方式中,时钟同步方法的执行主体可以是主动模块。具体的如图1所示,示例性流程包括:步骤s201:接收并解析可编程逻辑模块发送的时钟同步数据,得到第一时钟信号和第二时钟信号。

39.可选的,第一时钟信号和第二时钟信号可以用于互为备用地向多个时钟应用单元提供参考,以使多个时钟应用单元时钟同步。

40.可选的,时钟同步数据可以是可编程逻辑模块将第一时钟信号、第二时钟信号转换得到的数据。可编程逻辑模块可以将时钟同步数据发送至主控模块。可选的,可编程逻辑模块可以是fpga模块。

41.下面基于图6c进一步阐述步骤s304。

42.图6c是本技术实施例所提供的一种时钟同步方法的第二模块结构示意图。如图6c所图示,主控模块可以包括主控0和主控1。主控0、主控1可以分别接收fpga发送的时钟同步数据,可选的,时钟同步数据可以包括第一时钟信号,以及带有第二时钟信号的1pps数据的以太网报文。主控1和主控0可以分别解析时钟同步数据,得到第一时钟信号和第二时钟信号。

43.在一种可选的实施方式中,主控1和主控2之间可以通过以太网、pcie、can总线等方式进行数据同步与数据交互,从而保证两个主控模块各自内部的第一时钟信号保持一致,第二时钟信号也保持一致。可选的,若两个主控模块通过数据交互检测到两个模块中的第一时钟信号或第二时钟信号不一致,则通过数据交互调节优先级低的主控模块中的信号,即调整主控1的第一时钟信号或者第二时钟信号与主控0中相对应的第一时钟信号或者

第二时钟信号一致。

44.步骤s202:根据第二时钟信号和第一时钟信号得到差异信息。

45.可选的,差异信息可以表征第二时钟信号和第一时钟信号之间的差异。

46.步骤s203:若差异信息满足预设条件,向可编程逻辑模块发送第一纠偏指令。

47.可选的,第一纠偏指令可以用于指示可编程逻辑模块调整第二时钟信号,得到第一纠偏信号。第二时钟信号可以由可编程逻辑模块将第一时钟信号后移一个周期得到。

48.下面基于图6a、图6b以及图6c进一步阐述可编程逻辑模块生成并发送第一时钟信号、第二时钟信号的示例性流程。

49.图6a是本技术实施例所提供的一种时钟同步方法的第一模块结构示意图。

50.如图6a所图示,gps模块可以产生时钟同步信号,并将该时钟同步信号发送至fpga模块中。其中,该时钟同步信号可以是1pps时钟信号。

51.可选的,fpga模块可以接收该时钟同步信号,并将该时钟同步信号复制及透传成多路时钟信号。如图6a所图示,fpga可以将接收的1pps时钟信号复制并透传成一路信号,作为第一时钟信号。可选的,fpga模块可以通过内置或外置的ram,包括sram(static random-access memory,静态随机存取存储器)或者dram(dynamic random access memory,动态随机存取存储器),进行时钟同步信号相对应的数据缓存。fpga发出的信号可以包括第一时钟信号和第二时钟信号,第一时钟信号可以由fpga模块复制上述的时钟同步信号得到,第二时钟信号可以由fpga模块将第一时钟信号向后移一个周期得到。fpga可以将第一时钟信号以1pps时钟信号的方式发送,并将第二时钟信号以以太网报文的方式发送。

52.图6b是本技术实施例所提供的一种时钟同步方法的第一信号波形示意图。如图6b所图示,tr0’

可以是第一时钟信号对应的脉冲波形,tr0’’

可以是第二时钟信号对应的脉冲波形。由于包括1pps时钟信号在内的时钟信号对精度要求较高,对于采用1pps时钟信号进行整个系统时钟同步方案而言,其对信号波形边沿的上升沿时间、抖动要求较高,需要达到ns级别,如控制抖动偏差在10ns以内。因此,为确保后级接收到以太网报文时,能够有效地解析、进行上升沿以及下降沿的数据恢复,并减少在中间以太网转发、ad采样以及解码造成的延时,fpga模块可以通过下述方式处理时钟同步信号。

53.可选的,fpga模块接收到的gps模块发送的时钟同步信号的脉冲,可以按照周期分为p0、p1、p2,

…

,pn。fpga模块对时钟同步信号进行复制及分发的第一时钟信号脉冲可以为p0’、p1’、p2’,

…

,pn’,包括图6b中所图示的p0’、p1’、p2’,p3’。而对于第二时钟信号,fpga模块在进行ad采样以及转换为以太网报文时,可以将转换成以太网报文的时钟同步信号延后一个时钟周期进行发送,也就是相对于p0’后移一个时钟周期进行转发,由此得到转发的报文为p0

’’

、p1

’’

、p2

’’

,

…

,pn

’’

,包括图6b中搜图示的p0

’’

、p1

’’

、p2

’’

,p3

’’

。其中p0

’’

的上升沿可以与p1’的上升沿在时间上保持同步,p1

’’

的上升沿可以与p2’的上升沿在时间上保持同步,以此类推。在一种可选的实施方式中,步骤s202可以包括:将p0

’’

的上升沿相比p1’的上升沿的偏差确定为差异信息。

54.在本技术实施例中,通过将第一时钟信号或者时钟同步信号后移得到第二时钟信号,可以控制第一时钟信号的第二个上升沿和第二时钟信号的第一个上升沿保持同步,因此在后级的模块联合fpga模块的ram中的fifo(first input first output,先入先出队列)进行比对反馈时,无论是在第二时钟信号的相位向前偏移的情况下还是向后偏移的情

况下,都可以在第一时钟信号中定位到第二时钟信号的第一个周期的上升沿对应的位置,从而更方便地确定第一偏差值,并根据第一偏差值消除传输过程中产生的误差,从而精确地控制并调整第二时钟信号,使得后继主控模块接收并解析得到的第一时钟信号的第二个上升沿和第二时钟信号的第一个上升沿保持同步或者控制在预设范围内;并且,通过对后移一个周期的第二时钟信号以以太网报文的形式发送,可以减少第二时钟信号在以太网转发、ad采样以及解码过程中造成的延时,从而保证第二时钟信号校准的准确性。

55.下面基于图6c进行阐述。

56.如图6c所图示,在此实施方式中,中央计算单元的主控模块可以包括主控0和主控1,fpga模块可以包括fpga接口板模块0。

57.fpga接口板模块0可以向主控1和主控0发送时钟同步数据,时钟同步数据可以包括以太网报文形式的数据以及1pps时钟信号。可选的,fpga模块可以透传第一时钟信号至主控模块,并利用内部的逻辑电路,以及内部或外部的ad(analogue-to-digital,模数转换)模块,将第二时钟信号转换成具备tsn特性的以太网报文,通过以太网交换芯片发送至主控模块。可选的,在整个时钟同步系统中,时钟信号可以通过以太网以及支持tsn(time scalar network,时标网状图)的形式进行分发或者处理。

58.下面继续基于图2阐述步骤s203。

59.在上文中阐述的第二时钟信号由fpga模块将第一时钟信号后移一个周期得到的实施例中,差异信息可以包括第一偏差值,第一偏差值可以表征第一时钟信号的第二个周期的上升沿和第二时钟信号的第一个周期的上升沿之间的偏差。在此实施方式中,若差异信息满足预设条件,向fpga模块发送第一纠偏指令,可以包括:若第一偏差值满足第一预设偏差条件,向fpga模块发送第一纠偏指令;第一纠偏指令包括第一偏差值。可选的,第一预设偏差条件可以是第一偏差值大于预设值,预设值可以是0.05个周期、0.1个周期等;可选的,第一预设偏差条件可以是第一偏差值处于预设范围内,如0.1个周期~0.9个周期的范围内。fpga模块可以接收第一纠偏指令,并基于第一偏差值调整第二时钟信号。可选的,可以将第二时钟信号平移第一偏差值所对应的周期数。

60.可选的,fpga模块的ram可以在接收到第一纠偏指令之后,根据第一偏差值调整fifo堆栈,从而实现对第二时钟信号相位的调整,从而得到第一纠偏信号。

61.通过本技术实施例的一种时钟同步方法,可以将第一时钟信号作为基准,对第二时钟信号进行反馈校准,可以提高时钟信号校准的效率和准确性。

62.下面基于图3进一步阐述本技术实施例提供的一种时钟同步方法。

63.图3是本技术实施例所提供的一种时钟同步方法的第二流程示意图。具体地如图3所图示,示例性流程可以包括:步骤s301:接收并解析可编程逻辑模块发送的时钟同步数据,得到第一时钟信号和第二时钟信号。

64.步骤s302:根据第二时钟信号和第一时钟信号得到差异信息。

65.步骤s303:若差异信息满足预设条件,向可编程逻辑模块发送第一纠偏指令。

66.对于步骤s301-步骤s303的相关内容可以参考上文中针对步骤s201-步骤s203的阐述,此处不再赘述。

67.步骤s304:接收可编程逻辑模块发送的第一纠偏信号。

68.下面基于图6c进一步阐述步骤s304。如图6c所图示,主控模块可以包括主控0和主控1。主控0、主控1可以分别对接收到时钟同步数据,可选的,时钟同步数据可以包括第一时钟信号,以及带有第一纠偏信号的1pps数据的以太网报文。主控1和主控0可以分别解析时钟同步数据,得到第一时钟信号和第一纠偏信号。

69.在一种可选的实施方式中,主控1和主控2之间可以通过以太网、pcie、can总线等方式进行数据同步与数据交互,从而保证两个主控模块各自内部的第一时钟信号保持一致,第一纠偏信号也保持一致。可选的,若两个主控模块通过数据交互检测到两个模块中的第一时钟信号或第一纠偏信号不一致,则通过数据交互调节优先级低的主控模块中的信号,即调整主控1的第一时钟信号或者第一纠偏信号与主控0中相对应的第一时钟信号或者第一纠偏信号一致。

70.步骤s305:根据第一时钟信号或第一纠偏信号,确定目标时钟信号。

71.可选的,第一时钟信号和第一纠偏信号可以互为备用。若检测到第一时钟信号处于异常状态,可以根据第一纠偏信号,确定目标时钟信号;若检测到第一纠偏信号处于异常状态,可以根据第一时钟信号,确定目标时钟信号。

72.在一种可选的实施方式中,在确定目标时钟信号之后,还可以包括:对目标时钟信号进行去抖、取均值操作,得到应用时钟信号。可选的,可以在接收预设周期的目标时钟信号之后,将目标时钟信号去抖、取均值,得到应用时钟信号。可选的,应用时钟信号可以是低抖动的时钟信号。

73.下面基于图4进一步阐述步骤s305。

74.图4是本技术实施例所提供的一种时钟同步方法的第三流程示意图。具体地如图4所图示,示例性流程可以包括:步骤s401:根据第一时钟信号或第一纠偏信号,确定基准时钟信号。

75.在一种可选的实施方式中,步骤s401可以在主控模块以及可编程逻辑模块对第二时钟信号进行比对和校正之后执行,以确定基准时钟信号。基准时钟信号可以用于作为比对的基准,以使主控模块基于该基准时钟信号对第一时钟信号、第一纠偏信号或者时钟同步数据的丢失、中断、错报进行纠偏或者备份补充,可选的,可以在接收预设周期的第一时钟信号或者第一纠偏信号之后,将第一时钟信号或者第一纠偏信号去抖、取均值,得到基准时钟信号。可选的,基准时钟信号可以是低抖动的时钟信号。

76.可选的,第一时钟信号和第一纠偏信号可以互为备用。若检测到第一时钟信号处于异常状态,可以根据第一纠偏信号,确定基准时钟信号;若检测到第一纠偏信号处于异常状态,可以根据第一时钟信号,确定基准时钟信号。

77.步骤s402:若检测到第一纠偏信号存在缺失周期,从基准时钟信号中确定补充时钟信号。

78.可选的,补充时钟信号可以用于补充缺失周期上的信息。

79.在一种可选的实施方式中,可以检测第一纠偏信号是否存在缺失周期,若存在,针对缺失的时钟周期,可以直接根据基准时钟信号的波形信息进行裁剪,以实现第一纠偏信号的补足,即将基准时钟信号中缺失周期所对应的波形部分确定为补充时钟信号。

80.在一种可选的实施方式中,步骤s402还可以包括:检测第一时钟信号是否存在缺失周期,若存在,针对缺失的时钟周期,可以直接根据基准时钟信号的波形信息进行裁剪,

以实现第一时钟信号的补足,即将基准时钟信号中缺失周期所对应的波形部分确定为补充时钟信号。

81.步骤s403:向可编程逻辑模块发送信号补充指令。

82.可选的,信号补充指令可以包括补充时钟信号。

83.在一种可选的实施方式中,信号补充指令可以用于指示fpga模块根据补充时钟信号补充第一纠偏信号,得到目标补充信号。

84.在本技术实施例中,通过将该补充时钟信号从基准时钟信号上裁剪并补充至第一纠偏信号上,可以在第一纠偏信号的不完整的情况下通过信号补充得到目标补充信号,从而保证参考信号的完整性,避免后续影响时钟应用模块的时钟同步参考判断。

85.在上文中阐述的步骤s402包括检测第一时钟信号是否存在缺失周期的实施方式中,信号补充指令还可以用于指示fpga模块根据补充时钟信号补充第一时钟信号,得到补充后的第一时钟信号。

86.步骤s404:接收可编程逻辑模块发送的目标补充信号。

87.下面基于图6c进一步阐述步骤s404。如图6c所图示,主控模块可以包括主控0和主控1。主控0、主控1可以分别对接收到时钟同步数据,可选的,时钟同步数据可以包括第一时钟信号,以及带有目标补充信号的1pps数据的以太网报文。主控1和主控0可以分别解析时钟同步数据,得到第一时钟信号和目标补充信号。

88.在一种可选的实施方式中,主控1和主控2之间可以通过以太网、pcie、can总线等方式进行数据同步与数据交互,从而保证两个主控模块各自内部的第一时钟信号保持一致,目标补充信号也保持一致。可选的,若两个主控模块通过数据交互检测到两个模块中的第一时钟信号或目标补充信号不一致,则通过数据交互调节优先级低的主控模块中的信号,即调整主控1的第一时钟信号或者目标补充信号与主控0中相对应的第一时钟信号或者目标补充信号一致。

89.步骤s405:根据第一时钟信号或目标补充信号,确定目标时钟信号。

90.可选的,第一时钟信号和目标补充信号可以互为备用。若检测到第一时钟信号处于异常状态,可以根据目标补充信号,确定目标时钟信号;若检测到目标补充信号处于异常状态,可以根据第一时钟信号,确定目标时钟信号。

91.在一种可选的实施方式中,在确定目标时钟信号之后,还可以包括:对目标时钟信号进行去抖、取均值操作,得到应用时钟信号。可选的,可以在接收预设周期的目标时钟信号之后,将目标时钟信号去抖、取均值,得到应用时钟信号。可选的,应用时钟信号可以是低抖动的时钟信号。

92.下面基于图5进一步阐述步骤s305。

93.图5是本技术实施例所提供的一种时钟同步方法的第四流程示意图。具体地如图5所图示,示例性流程可以包括:步骤s501:根据第一时钟信号或第一纠偏信号,确定基准时钟信号。

94.在一种可选的实施方式中,步骤s501可以在主控模块以及fpga模块对第二时钟信号进行比对和校正之后执行,以确定基准时钟信号。基准时钟信号可以用于作为比对的基准,以使主控模块基于该基准时钟信号对第一时钟信号、第一纠偏信号或者时钟同步数据的丢失、中断、错报进行纠偏或者备份补充,可选的,可以在接收预设周期的第一时钟信号

或者第一纠偏信号之后,将第一时钟信号或者第一纠偏信号去抖、取均值,得到基准时钟信号。可选的,基准时钟信号可以是低抖动的时钟信号。

95.可选的,第一时钟信号和第一纠偏信号可以互为备用。若检测到第一时钟信号处于异常状态,可以根据第一纠偏信号,确定基准时钟信号;若检测到第一纠偏信号处于异常状态,可以根据第一时钟信号,确定基准时钟信号。

96.步骤s502:基于第一纠偏信号和基准时钟信号得到第二偏差值。

97.可选的,经过第一纠偏信号的上升沿和基准时钟信号的上升沿之间的比对,可以得到第二偏差值。第二偏差值可以表征第一纠偏信号的第二个周期的上升沿和基准时钟信号的第一个周期或者第二个周期的上升沿之间的偏差。

98.下面介绍两种基于第一纠偏信号和基准时钟信号得到第二偏差值的具体实施方式:在第一种可选的实施方式中,若基准时钟信号基于第一时钟信号确定,则步骤s502可以包括:将第一纠偏信号的第二个周期的上升沿和基准时钟信号的第一个周期的上升沿进行比对。第二偏差值可以表征第一纠偏信号的第二个周期的上升沿和基准时钟信号的第一个周期的上升沿之间的偏差。

99.在第二种可选的实施方式中,若基准时钟信号基于第一纠偏信号确定,则步骤s502可以包括:将第一纠偏信号的第二个周期的上升沿和基准时钟信号的第二个周期的上升沿进行比对。第二偏差值可以表征第一纠偏信号的第二个周期的上升沿和基准时钟信号的第二个周期的上升沿之间的偏差。

100.可选的,步骤s502还可以包括:基于第一时钟信号和基准时钟信号得到第二偏差值。第二偏差值可以表征第一时钟信号的第一个周期或者第二个周期的上升沿和基准时钟信号的第一个周期的上升沿之间的偏差。

101.下面介绍两种基于第一时钟信号和基准时钟信号得到第二偏差值的具体实施方式:在第一种可选的实施方式中,若基准时钟信号基于第一时钟信号确定,则步骤s502可以包括:将第一时钟信号的第一个周期的上升沿和基准时钟信号的第一个周期的上升沿进行比对。第二偏差值可以表征第一时钟信号的第一个周期和基准时钟信号的第一个周期的上升沿之间的偏差。

102.在第二种可选的实施方式中,若基准时钟信号基于第一纠偏信号确定,则步骤s502可以包括:将第一时钟信号的第二个周期的上升沿和基准时钟信号的第一个周期的上升沿进行比对。第二偏差值可以表征第一时钟信号的第二个周期的上升沿和基准时钟信号的第一个周期的上升沿之间的偏差。

103.步骤s503:若第二偏差值满足第二预设偏差条件,向可编程逻辑模块发送第二纠偏指令。

104.可选的,第二纠偏指令可以包括第二偏差值。第二纠偏指令可以用于指示fpga模块根据第二偏差值调整第一纠偏信号,得到第二纠偏信号。

105.在一种可选的实施方式中,第二预设偏差条件可以是第二偏差值大于预设值,预设值可以是0.05个周期、0.1个周期等;可选的,第二预设偏差条件可以是第二偏差值处于预设范围内,如0.1个周期~0.9个周期的范围内。fpga模块可以接收第二纠偏指令,并基于

第二偏差值调整第一纠偏信号。可选的,可以将第一纠偏信号平移第二偏差值所对应的周期数。

106.在上文中阐述的步骤s502包括基于基于第一时钟信号和基准时钟信号得到第二偏差值的实施方式中,fpga模块可以接收第二纠偏指令,并基于第二偏差值调整第一时钟信号。可选的,可以将第一时钟信号平移第二偏差值所对应的周期数。

107.下面基于图7进一步阐述步骤s503。

108.图7是本技术实施例所提供的一种时钟同步方法的第二信号波形示意图。如图7所图示,第二预设偏差条件可以是第二偏差值大于或者等于预设阈值δth,图7中的c0表征基准时钟信号,第一个d

’’

表征第一种实施方式中的第一纠偏信号,第二个d

’’

表征第二种实施方式中的第一纠偏信号。下面对两种实施方式进行具体的介绍。

109.在第一种实施方式中,如图7所图示,第一纠偏信号的波形比基准时钟信号的波形相位超前,第二偏差值为δt1。当|δt1|》=|δth|时,则第二偏差值满足第二预设偏差条件,相当于可以认为当前第一纠偏信号的边沿抖动超出了警戒阈值范围,向fpga模块发送第二纠偏指令,以通过反馈调整第一纠偏信号。

110.在第二种实施方式中,如图7所图示,第一纠偏信号的波形比基准时钟信号的波形相位之后,第二偏差值为δt2。当|δt2|》=|δth|时,则第二偏差值满足第二预设偏差条件,相当于可以认为当前第一纠偏信号的边沿抖动超出了警戒阈值范围,向fpga模块发送第二纠偏指令,以通过反馈调整第一纠偏信号。

111.可选的,fpga模块的ram可以在接收到第二纠偏指令之后,根据第二偏差值调整fifo堆栈,从而实现对第一纠偏信号相位的调整,从而得到第二纠偏信号。

112.可选的,在向fpga发送第二纠偏指令的同时,执行模块还可以进行告警记录,并知会fpga接口模块的ram,调整fifo堆栈,对输出的d

’’

相位进行调整。

113.步骤s504:接收可编程逻辑模块发送的第二纠偏信号。

114.下面基于图6c进一步阐述步骤s404。如图6c所图示,主控模块可以包括主控0和主控1。主控0、主控1可以分别对接收到时钟同步数据,可选的,时钟同步数据可以包括第一时钟信号,以及带有第二纠偏信号的1pps数据的以太网报文。主控1和主控0可以分别解析时钟同步数据,得到第一时钟信号和第二纠偏信号。

115.在一种可选的实施方式中,主控1和主控2之间可以通过以太网、pcie、can总线等方式进行数据同步与数据交互,从而保证两个主控模块各自内部的第一时钟信号保持一致,第二纠偏信号也保持一致。可选的,若两个主控模块通过数据交互检测到两个模块中的第一时钟信号或第二纠偏信号不一致,则通过数据交互调节优先级低的主控模块中的信号,即调整主控1的第一时钟信号或者第二纠偏信号与主控0中相对应的第一时钟信号或者第二纠偏信号一致。

116.在一种可选的实施方式中,步骤s503-步骤s504可以是:若第二偏差值满足第二预设偏差条件,通过主控模块的cpu,利用内存资源基于第二偏差值调整第一纠偏信号,得到第二纠偏信号。在这种实施方式中,无需和fpga模块进行通信,也无需进行反馈交互。

117.步骤s505:根据第一时钟信号或第二纠偏信号,确定目标时钟信号。

118.可选的,第一时钟信号和第二纠偏信号可以互为备用。若检测到第一时钟信号处于异常状态,可以根据第二纠偏信号,确定目标时钟信号;若检测到第二纠偏信号处于异常

状态,可以根据第一时钟信号,确定目标时钟信号。

119.在一种可选的实施方式中,在确定目标时钟信号之后,还可以包括:对目标时钟信号进行去抖、取均值操作,得到应用时钟信号。可选的,可以在接收预设周期的目标时钟信号之后,将目标时钟信号去抖、取均值,得到应用时钟信号。可选的,应用时钟信号可以是低抖动的时钟信号。

120.下面继续基于图3进行阐述:步骤s306:发送目标时钟信号至时钟应用模块。

121.在一种可选的实施方式中,在上文中阐述的得到应用时钟信号的实施方式中,步骤s306可以包括:发送应用时钟信号至时钟应用模块。

122.下面基于图8进一步阐述步骤s306。

123.图8是本技术实施例所提供的一种时钟同步方法的第三模块结构示意图。如图8所图示,时钟应用模块可以包括计算单元0、计算单元1,主控模块可以包括主控0、主控1,fpga模块可以包括fpga接口板模块0。

124.其中,主控0可以具有最高的主控优先级,目标时钟信号可以由主控0发送到计算单元0、计算单元1。这里不对时钟应用模块的类别作限定,在其他一些可选的实施例中,时钟应用模块还可以是任何需要参考时钟的模块,如车控模块、其他算力模块、座舱模块等。主控1的主控优先级低于主控0的主控优先级。主控1作为备用主控,同样可以发送目标时钟信号至计算单元0、计算单元1。

125.可选的,主控1和主控0可以进行数据交互,保证主控1和主控0 的目标时钟信号保持一致或者同步。在主控0的目标时钟信号异常或者丢失后,主控1的目标时钟信号可以作用备用时钟进行切换。以计算单元0为例,计算单元可以接收主控0发送的目标时钟信号,以及主控1发送的目标时钟信号,两者发送的目标时钟信号分别携带有0级时钟优先级信息和1级时钟优先级信息;计算单元0在接收到两者发送的目标时钟信号之后,可以基于0级时钟优先级信息,将主控0发送的目标时钟信号确定为参考时钟信号。计算单元1确定参考时钟信号的示例性流程可以参考上述的计算单元0确定参考时钟信号的流程,这里不再赘述。

126.下面继续基于图3阐述步骤s306。

127.在一种可选的实施方式中,主控模块的数量可以为多个。时钟应用模块可以用于接收多个主控模块发送的多个目标时钟信号,根据时钟优先级从多个目标时钟信号中确定主用时钟信号。本技术中,不仅第一时钟信号和第二时钟信号可以互为备份,并且多个主控模块确定的目标时钟信号可以互为备份,可以提高时钟源的可靠性。

128.可选的,多个主控模块可选通过pcie、以太网(如sgmii信号)、can总线,以及i2c(inter-integrated circuit,两线式串行总线)、gpio(general purpose input output,通用输入/输出口)等通信方式,分别与多个计算单元、座舱单元、底盘控制单元进行数据交互与控制。同时上述各个从单元可选通过心跳、在位等形式,及时识别自身的工作状态并上报主控模块。

129.通过本技术实施例提供的一种时钟同步方法,通过时钟信号的数字化处理以及多个主控模块的时钟互为备份,可以保证时钟源在整个中央计算平台的各个模块、各个单元之中保持稳定;并且,通过确定基准时钟信号,并根据基准时钟信号进行实时校验、查漏补缺,可以提高时钟信号校验的效率和准确率;进一步的通过以太网、pcie、can总线等实现数

据交互,在中央计算架构下,可以实现智能驾驶域、智能座舱域、地盘控制域的时钟同步以及跨域互通;通过主控单元执行待处理数据在多个计算单元中的分发调度处理,能够实现计算单元在整个系统内的资源共享,并可以合理分配计算资源,从而提升系统算力的利用率。

130.相应地,本技术提供一种时钟同步装置。图9是本技术实施例所提供的一种时钟同步装置的结构示意图。如图9所图示,时钟同步装置900用于主控模块,可以包括:接收模块901,用于接收并解析可编程逻辑模块发送的时钟同步数据,得到第一时钟信号和第二时钟信号;第一时钟信号和第二时钟信号用于互为备用地向多个时钟应用单元提供参考,以使多个时钟应用单元时钟同步;确定模块902,用于根据第二时钟信号和第一时钟信号得到差异信息;发送模块903,用于若差异信息满足预设条件,向可编程逻辑模块发送第一纠偏指令;第一纠偏指令用于指示可编程逻辑模块调整第二时钟信号,得到第一纠偏信号。

131.可选的,第二时钟信号由可编程逻辑模块将第一时钟信号后移一个周期得到;差异信息包括第一偏差值,第一偏差值表征第一时钟信号的第二个周期的上升沿和第二时钟信号的第一个周期的上升沿之间的偏差。发送模块903还可以用于若第一偏差值满足第一预设偏差条件,向可编程逻辑模块发送第一纠偏指令;第一纠偏指令包括第一偏差值。

132.可选的,装置还可以包括应用模块,用于接收可编程逻辑模块发送的第一纠偏信号;根据第一时钟信号或第一纠偏信号,确定目标时钟信号;发送目标时钟信号至时钟应用模块。

133.可选的,确定模块902还可以用于根据第一时钟信号或第一纠偏信号,确定基准时钟信号;若检测到第一纠偏信号存在缺失周期,从基准时钟信号中确定补充时钟信号;补充时钟信号用于补充缺失周期上的信息;向可编程逻辑模块发送信号补充指令;信号补充指令包括补充时钟信号,信号补充指令用于指示可编程逻辑模块根据补充时钟信号补充第一纠偏信号,得到目标补充信号;接收可编程逻辑模块发送的目标补充信号;根据第一时钟信号或目标补充信号,确定目标时钟信号。

134.可选的,确定模块902还可以用于根据第一时钟信号或第一纠偏信号,确定基准时钟信号;基于第一纠偏信号和基准时钟信号得到第二偏差值;第二偏差值表征第一纠偏信号的第二个周期的上升沿和基准时钟信号的第一个周期或者第二个周期的上升沿之间的偏差;若第二偏差值满足第二预设偏差条件,向可编程逻辑模块发送第二纠偏指令;第二纠偏指令包括第二偏差值,第二纠偏指令用于指示可编程逻辑模块根据第二偏差值调整第一纠偏信号,得到第二纠偏信号;接收可编程逻辑模块发送的第二纠偏信号;根据第一时钟信号或第二纠偏信号,确定目标时钟信号。

135.可选的,确定模块902还可以还用于,在确定目标时钟信号之后,对目标时钟信号进行去抖、取均值操作,得到应用时钟信号。发送模块903还可以用于发送应用时钟信号至时钟应用模块。

136.可选的,主控模块的数量可以为多个;时钟应用模块可以用于接收多个主控模块发送的多个目标时钟信号,根据时钟优先级从多个目标时钟信号中确定主用时钟信号。

137.本技术的一种时钟同步装置的实施例可以和本技术的一种时钟同步方法的实施例基于相同的构思。

138.相应地,本公开实施例还提供一种电子设备,电子设备包括处理器和存储器,存储器中存储有至少一条指令、至少一段程序、代码集或指令集,至少一条指令、至少一段程序、代码集或指令集由处理器加载并执行以实现上述的时钟同步方法。

139.本技术实施例所提供的方法实施例可以在计算机终端、服务器或者类似的运算装置中执行。以运行在服务器上为例,图10是本技术实施例提供的时钟同步方法的服务器的硬件结构框图。如图10所示,该服务器1000可因配置或性能不同而产生比较大的差异,可以包括一个或一个以上中央处理器(central processing units,cpu)1010(中央处理器1010可以包括但不限于微处理器mcu或可编程逻辑器件fpga等的处理装置)、用于存储数据的存储器1030,一个或一个以上存储应用程序1023或数据1022的存储介质1020(例如一个或一个以上海量存储设备)。其中,存储器1030和存储介质1020可以是短暂存储或持久存储。存储在存储介质1020的程序可以包括一个或一个以上模块,每个模块可以包括对服务器中的一系列指令操作。更进一步地,中央处理器1010可以设置为与存储介质1020通信,在服务器1000上执行存储介质1020中的一系列指令操作。服务器1000还可以包括一个或一个以上电源1050,一个或一个以上有线或无线网络接口1050,一个或一个以上输入输出接口1040,和/或,一个或一个以上操作系统1021,例如windows servertm,mac os xtm,unixtm, linuxtm,freebsdtm等等。

140.输入输出接口1040可以用于经由一个网络接收或者发送数据。上述的网络具体实例可包括服务器1000的通信供应商提供的无线网络。在一个实例中,输入输出接口1040包括一个网络适配器(network interface controller,nic),其可通过基站与其他网络设备相连从而可与互联网进行通讯。在一个实例中,输入输出接口1040可以为射频(radio frequency,rf)模块,其用于通过无线方式与互联网进行通讯。

141.本领域普通技术人员可以理解,图10所示的结构仅为示意,其并不对上述电子装置的结构造成限定。例如,服务器1000还可包括比图10中所示更多或者更少的组件,或者具有与图10所示不同的配置。

142.本技术实施提供一种存储介质,存储介质可设置于服务器之中以保存用于实现方法实施例中时钟同步方法相关的至少一条指令、至少一段程序、代码集或指令集,该至少一条指令、该至少一段程序、该代码集或指令集由该处理器加载并执行以实现上述时钟同步方法。

143.具体地,在本实施例中,上述存储介质可以位于计算机网络的多个网络服务器中的至少一个网络服务器。可选地,在本实施例中,上述存储介质可以包括但不限于包括:u盘、只读存储器(rom,read-only memory)、移动硬盘、磁碟或者光盘等各种可以存储程序代码的介质。

144.在本发明中,除非另有明确的规定和限定,术语“相连”、“连接”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的相连或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

145.需要说明的是:上述本技术实施例的先后顺序仅仅为了描述,不代表实施例的优劣,且上述本说明书对特定的实施例进行了描述,其他实施例也在所附权利要求书的范围

内。在一些情况下,在权利要求书中记载的动作或者步骤可以按照不同的实施例中的顺序来执行并且能够实现预期的结果。另外,在附图中描绘的过程不一定要求示出特定顺序或者而连接顺序才能够实现期望的结果,在某些实施方式中,多任务并行处理也是可以的或者可能是有利的。

146.本说明书中的各个实施例均采用递进的方式描述,各个实施例之间相同相似的部分互相参见即可,每个实施例重点说明的均为与其他实施例的不同之处。尤其,对于装置/系统的实施例而言,由于其基于相似于方法实施例,所以描述的比较简单,相关之处参见方法实施例的部分说明即可。

147.以上是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1