图像传感器和相机的制作方法

图像传感器和相机

1.本技术要求于2021年9月16日在韩国知识产权局提交的第10-2021-0124267号韩国专利申请和于2022年3月10日在韩国知识产权局提交的第10-2022-0030323号韩国专利申请的优先权,所述韩国专利申请的公开通过引用全部包含于此。

技术领域

2.本公开涉及一种图像传感器,更具体地,涉及一种用于测量距离的图像传感器和包括该图像传感器的相机。

背景技术:

3.基于飞行时间(tof)的图像传感器可通过测量到对象的距离来生成对象的三维图像。基于tof的图像传感器可通向对象照射光并测量直到接收到从对象反射的光的光飞行时间来获得关于到对象的距离的信息。因为与距离相关的信息包括由于各种因素导致的噪声,因此有必要最小化噪声以获得准确的信息。

技术实现要素:

4.本公开提供能够减少读噪声的用于距离测量的图像传感器和包括图像传感器的相机。

5.根据示例实施例的一个方面,一种图像传感器包括:解调时钟生成电路,被配置为生成分别具有第一相位至第四相位的第一解调时钟信号至第四解调时钟信号;解调相位选择电路,被配置为基于第一解调时钟信号至第四解调时钟信号和针对多个包中的每个包而改变的随机数,生成第一预解调信号至第四预解调信号;延迟电路,被配置为通过将第一预解调信号延迟多个延迟相位来生成多个第一延迟信号,通过将第二预解调信号延迟所述多个延迟相位来生成多个第二延迟信号,通过将第三预解调信号延迟所述多个延迟相位来生成多个第三延迟信号,并且通过将第四预解调信号延迟所述多个延迟相位来生成多个第四延迟信号;以及相位混合器,被配置为生成相位基于地址而改变的多个第一解调信号、相位基于地址而改变的多个第二解调信号、相位基于地址而改变的多个第三解调信号和相位基于地址而改变的多个第四解调信号,地址针对所述多个包中的每个包而改变。第一相位至第四相位彼此具有90

°

的相位差。

6.根据示例实施例的一个方面,一种图像传感器包括:像素阵列,包括第一组像素和第二组像素;以及控制电路,被配置为将调制信号提供给光源,并且将相位基于随机数和地址而改变的多个第一解调信号、相位基于随机数和地址而改变的多个第二解调信号、相位基于随机数和地址而改变的多个第三解调信号和相位基于随机数和地址而改变的多个第四解调信号提供给像素阵列。提供给第一组像素的第一解调信号至第四解调信号与提供给第二组像素的第一解调信号至第四解调信号具有不同的相位,与一帧对应的积分时间包括多个包,并且随机数和地址针对所述多个包中的每个包而改变。

7.根据示例实施例的一个方面,一种相机包括:光源;以及图像传感器。图像传感器

包括:像素阵列,包括多个像素,所述多个像素被配置为接收由光源生成的和从对象反射的光信号;以及控制电路,被配置为将调制信号提供给光源,并且将相位基于随机数和地址而改变的多个第一解调信号、相位基于随机数和地址而改变的多个第二解调信号、相位基于随机数和地址而改变的多个第三解调信号和相位基于随机数和地址而改变的多个第四解调信号提供给像素阵列。与一帧对应的积分时间包括多个包,并且随机数和地址针对所述多个包中的每个包而改变。

附图说明

8.从下面的结合附图的示例实施例的描述,以上和其他方面和特征将变得更加清楚,其中:

9.图1是根据示例实施例的系统的示意配置图;

10.图2是用于解释根据示例实施例的相机的配置图;

11.图3是用于解释图2中示出的像素的结构的示例实施例的示图;

12.图4是示出根据示例实施例的包括在图像传感器中的控制电路的框图;

13.图5是示出根据示例实施例的图4的解调相位选择电路的框图;

14.图6a是示出根据示例实施例的基于随机数的调制信号和多个预解调信号的时序图;

15.图6b是示出根据示例实施例的由图像传感器的延迟电路生成的延迟信号的时序图;

16.图7是示出根据示例实施例的图像传感器的像素阵列的框图;

17.图8是示出根据示例实施例的基于地址提供给像素阵列的第一解调信号至第四解调信号的时序图。

18.图9是用于描述根据示例实施例的提供给包括在像素阵列中的多个像素组中的每个像素组的第一解调信号的示图;

19.图10是用于解释根据示例实施例的包括具有4抽头结构的像素的图像传感器的操作的时序图;

20.图11是用于解释图2中示出的像素的结构的示例实施例的示图;

21.图12和图13是用于解释根据示例实施例的包括具有双抽头结构的像素的图像传感器的操作的时序图;

22.图14是示出根据示例实施例的图像传感器的示意图。

具体实施方式

23.在下文中,将参照附图详细描述示例实施例。提供在此描述的实施例作为示例,并且因此,本公开不限于此,并且可以以各种其他形式实现。在下面的描述中提供的每个示例实施例不被排除与也在此提供的另外的示例或另外的实施例的一个或多个特征相关联,或者与未在此提供但与本公开一致的另外的示例或另外的实施例的一个或多个特征相关联。诸如

“……

中的至少一个”的表述在一列元素之后时,修饰整列元素而不是修饰列中的单个元素。例如,表述“a、b和c中的至少一个”应被理解为:仅包括a、仅包括b、仅包括c、包括a和b二者、包括a和c二者、包括b和c二者或者包括全部的a、b和c。

24.图1是根据示例实施例的系统的示意配置图。

25.参照图1,系统10可包括处理器30和相机100。系统10还可包括连接到处理器30以存储从相机100接收的信息(诸如,图像数据)的存储器20。在一个示例实施例中,系统10可被集成到一个半导体芯片中,并且相机100、处理器30和存储器20中的每个可被实现为单独的半导体芯片。存储器20可包括一个或多个存储器芯片。在一个示例实施例中,处理器30可包括多个处理芯片。

26.系统10可以是电子装置,并且可将图像传感器用于距离测量。系统10可以是便携式的或固定的。系统10的便携形式的示例包括移动装置、蜂窝电话、智能电话、用户设备(ue)、平板计算机、数码相机、膝上型计算机或台式计算机、电子智能手表、机器对机器(m2m)通信装置、虚拟现实(vr)装置或虚拟现实(vr)模块、机器人等。系统10的固定形式的示例包括视频游戏室中的游戏机、交互式视频终端、汽车、机械视觉系统、工业机器人、虚拟现实(vr)装置、汽车中驾驶员侧安装的相机等。

27.相机100可包括光源12和图像传感器14。光源12可生成可入射到对象200上的发送光信号tx。从光源12输出的发送光信号tx可被对象200反射,并且从对象200反射的接收光信号rx可被图像传感器14接收。图像传感器14可通过使用飞行时间(tof)获得深度信息(例如,关于对象200的距离信息)。

28.光源12可包括光源(例如,发光二极管(led))和驱动光源的光源驱动器。图像传感器14可包括像素阵列、用于驱动像素阵列的控制电路、以及用于读出从像素阵列输出的像素信号的读出电路。

29.处理器30可以是中央处理器(cpu),中央处理器(cpu)是通用处理器。在一个示例实施例中,除了cpu之外,处理器30还可包括微控制器、数字信号处理器(dsp)、图形处理器(gpu)、专用集成电路(asic)处理器等。此外,处理器30可包括一个以上在分布式处理环境中操作的cpu。在一个示例实施例中,处理器30可以是具有cpu的功能的附加功能的片上系统(soc)。

30.处理器30可控制光源12和图像传感器14的操作。在一个示例实施例中,系统10可由用户控制,并且可包括模式开关以在二维(2d)成像模式与三维(3d)成像模式之间进行切换。当用户使用模式开关选择2d成像模式时,因为2d成像模式使用环境光,所以处理器30可激活图像传感器14,并且光源12可不被激活。

31.当用户使用模式开关选择3d成像模式时,处理器30可激活光源12和图像传感器14二者。从读出电路接收的处理后的图像数据可被处理器30存储在存储器20中。处理器30可在系统10的显示屏幕上显示由用户选择的2d图像或3d图像。处理器30可以用软件或固件被编程以执行描述的各种处理任务。在一个示例实施例中,处理器30可包括用于执行上面描述的部分或全部功能的可编程硬件逻辑电路。例如,存储器20可允许处理器30通过存储程序代码、查找表或中间操作结果来执行相应的功能。

32.存储器20可以是例如动态随机存取存储器(dram)(诸如,同步dram(sdram))、高带宽存储器(hbm),或基于dram的3d堆栈(3ds)存储器(诸如,混合存储器立方体(hmc)存储器)。存储器20可以是例如固态驱动器(ssd)、dram、或基于半导体的存储装置(诸如,静态随机存取存储器(sram)、相变随机存取存储器(pram)、电阻式随机存取存储器(rram)、导电桥接ram(cbram)、磁ram(mram)、自旋转移力矩mram(stt-mram))。

33.图2是用于解释根据示例实施例的相机的配置图。

34.参照图1和图2,相机100可被用于获得关于对象200的距离信息。距离信息可由处理器30基于从图像传感器14输出的图像数据idata来计算,或者可在图像传感器14内部自行计算。在一个示例实施例中,距离信息可被处理器30用作3d用户接口的一部分,以使得与对象200的3d图像的交互能够作为由系统10的用户在系统10上运行的游戏或另外的应用的一部分,或者使得能够使用以三维形成的对象200的3d图像。

35.光源12可包括光源驱动器140和光源器件150。光源12还可包括透镜。

36.光源器件150可将发送光信号tx发送到对象200。光源器件150可以是可发射红外光或可见光的激光二极管(ld)或发光二极管(led),作为近红外激光(nir)、点光源、白色灯和单色器的组合的单色照明源、或其他激光光源的组合。例如,光源器件150可以是垂直腔表面发射激光器(vcsel)。在一个示例实施例中,光源器件150可输出具有约800纳米至约1000纳米的波长的红外发送光信号tx。

37.光源驱动器140可生成用于驱动光源器件150的驱动信号。光源驱动器140可根据从控制电路120接收的调制信号mod来驱动光源器件150。

38.图像传感器14可使用tof原理测量距离或深度。图像传感器14可接收从对象200反射的接收光信号rx。图像传感器14可包括像素阵列110、控制电路120和读出电路130。图像传感器14还可包括透镜,接收光信号rx可通过透镜被提供给像素阵列110。

39.像素阵列110可包括多个像素111。多个像素111可以以tof方法操作。多个像素111中的每个像素的结构将稍后关于图3来描述。

40.像素阵列110可以是rgb像素阵列,在rgb像素阵列中,不同的像素收集不同的光色(例如,第一像素可收集红光,第二像素可收集绿光,并且第三像素可收集蓝光)。像素阵列110可以是例如2d传感器(诸如,具有红外(ir)阻挡滤色器的2d rgb传感器、2d红外(ir)传感器、2d近红外(nir)传感器、2d rgbw传感器或2d rgb-ir传感器等)。系统10可使用同一像素阵列110,来不仅测量到对象200的距离,而且对对象200(或包含对象的场景)的2d rgb颜色进行成像。

41.像素阵列110可将接收光信号rx转换为电信号(即,像素信号)。读出电路130可基于从像素阵列110输出的像素信号生成图像数据idata。例如,读出电路130可对像素信号执行模数转换。

42.图像传感器14还可包括存储器和图像信号处理器。图像数据idata可被存储在存储器中,并且图像信号处理器可处理图像数据idata以计算距离信息或深度信息。存储器或图像信号处理器可被设置在图像传感器14的外部。

43.控制电路120可控制图像传感器14的组件(例如,像素阵列110和读出电路130),并且可控制光源12的光源驱动器140。控制电路120可将调制信号mod发送到光源驱动器140,并可将与调制信号mod对应的解调信号demod发送到像素阵列110。解调信号demod可以指的是用于控制包括在像素111中的每个中的每个传输晶体管的信号,但不限于此。

44.控制电路120可基于随机数生成调制信号mod和与调制信号mod对应的解调信号demod。因此,图像传感器14可通过聚合为随机噪声分量来移除接收光信号rx中由于由另外的装置(诸如,除相机100之外的相机)生成的光信号而生成的噪声(例如,多用户干扰(mui))。

45.此外,控制电路120可为包括在像素阵列110中的多个像素组中的每个提供具有不同延迟相位的解调信号demod,并且可将针对在积分时间(integration time)内的每个包(packet)具有不同延迟相位的解调信号demod提供给一个像素组。例如,在一个积分时间内的包的数量可与像素组的数量对应。因此,在像素阵列110中生成的解调信号demod的峰值电流可被减小,并且因此,电磁干扰(emi)可被减小,高速调制操作可以是可行的,并且可防止由于深度像素固定图案(pfppn)导致的恶化。

46.图3是用于解释图2中示出的像素111的结构的示例实施例的示图。

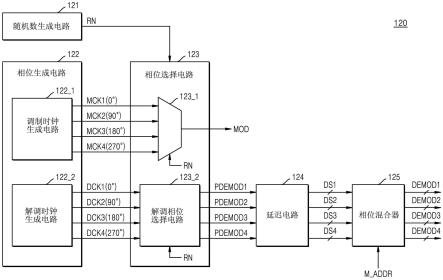

47.如图3中所示,像素111可具有4抽头结构。4抽头结构指示一个像素111包括四个抽头的结构,并且抽头可以指的是:在外部光信号通过不同相位照射时,能够区分和发送在像素111中针对每个相位生成和积累的光电荷的组件。

48.包括具有4抽头结构的像素111的图像传感器(例如,图2中的图像传感器14)可使用四个抽头实现关于0

°

、90

°

、180

°

和270

°

相位的发送的方法。例如,像素111的第一抽头可生成关于0

°

的相位的第一像素信号vout1,第二抽头可生成关于90

°

的相位的第二像素信号vout2,第三抽头可生成关于180

°

的相位的第三像素信号vout3,并且第四抽头可生成关于270

°

的相位的第四像素信号vout4。

49.参照图3,像素111可包括光电二极管pd、溢出门og、传输晶体管ts1至ts4、存储晶体管ss1至ss4、抽头传输晶体管txs1至txs4、复位晶体管rs1至rs4、源极跟随器sf1至sf4和选择晶体管sel1至sel4。根据一个示例实施例,溢出门og、存储晶体管ss1至ss4、抽头传输晶体管txs1至txs4、复位晶体管rx1至rx4、源极跟随器sf1至sf4和选择晶体管sel1至sel4中的至少一个可被省略。

50.光电二极管pd可生成根据接收光信号(例如,图2的rx)的强度而变化的光电荷。即,光电二极管pd可将接收光信号rx转换为电信号。光电二极管pd是光电转换装置的示例,并且可以是光电晶体管、光电门、钉扎光电二极管(ppd)及其组合中的至少一个。

51.第一传输晶体管ts1至第四传输晶体管ts4可根据第一解调信号demoda至第四解调信号demodd将由光电二极管pd生成的电荷分别发送到第一存储晶体管ss1至第四存储晶体管ss4。因此,第一传输晶体管ts1至第四传输晶体管ts4可根据第一解调信号demoda至第四解调信号demodd将由光电二极管pd生成的电荷分别发送到第一浮置扩散节点fd1至第四浮置扩散节点fd4。

52.第一解调信号demoda至第四解调信号demodd可被包括在图2的解调信号demod中,并且可以是彼此具有相同频率、相同占空比和不同相位的信号。第一解调信号demoda至第四解调信号demodd彼此之间可具有90

°

的相位差。例如,当第一解调信号demoda关于第一解调信号demoda具有0

°

的相位时,第二解调信号demodb可具有90

°

的相位,第三解调信号demodc可具有180

°

的相位,并且第四解调信号demodd可具有270

°

的相位。

53.第一存储晶体管ss1至第四存储晶体管ss4可存储通过第一传输晶体管ts1至第四传输晶体管ts4中的每个传送的光电荷,并且第一抽头传输晶体管txs1至第四抽头传输晶体管txs4可将存储在第一存储晶体管ss1至第四存储晶体管ss4中的每个中的光电荷传送到第一浮置扩散节点fd1至第四浮置扩散节点fd4。

54.第一源极跟随器sf1至第四源极跟随器sf4可基于由于在第一浮置扩散节点fd1至第四浮置扩散节点fd4中积累的光电荷导致的电势,将光电荷放大并输出到第一选择晶体

管sel1至第四选择晶体管sel4。第一选择晶体管sel1至第四选择晶体管sel4可根据选择控制信号通过列线输出第一像素信号vout1至第四像素信号vout4。

55.像素111可在预定时间(例如,积分时间)内积累光电荷,并且将根据积累结果生成的第一像素信号vout1至第四像素信号vout4输出到读出电路(例如,图2的读出电路130)。

56.第一复位晶体管rs1至第四复位晶体管rs4可将第一浮置扩散节点fd1至第四浮置扩散节点fd4复位到电源电压vdd。溢出门og可以是用于释放溢出电荷的晶体管,溢出门og的源极可被连接到光电二极管pd,并且电源电压vdd可被提供给溢出门og的漏极。

57.尽管参照图3示出和描述的像素111是4抽头结构,但是示例实施例不限于此。图像传感器14可包括具有不同的抽头结构的像素。例如,像素可具有双抽头结构,其示例稍后将参照图11来描述。

58.图4是示出根据示例实施例的包括在图像传感器中的控制电路的框图。图5是示出根据示例实施例的图4的解调相位选择电路123_2的框图。

59.参照图4,控制电路120可生成可被发送到光源驱动器(例如,图2的光源驱动器130)的调制信号mod和可被发送到像素阵列(例如,图2的像素阵列110)的第一解调信号demod1至第四解调信号demod4。控制电路120可包括随机数生成电路121、相位生成电路122、相位选择电路123、延迟电路124和相位混合器(phase mixer)125。

60.在定义一帧的积分时间期间,多个包可相互区分。随机数生成电路121可针对每个包新生成随机数rn。例如,随机数生成电路121可生成2位随机数#1:00、#2:01、#3:10和#4:11。控制电路120可包括线性反馈移位寄存器(lfsr),而不是随机数生成电路121。

61.相位生成电路122可包括调制时钟生成电路122_1和解调时钟生成电路122_2。调制时钟生成电路122_1可生成多个调制时钟信号(例如,第一调制时钟信号mck1至第四调制时钟信号mck4)。第一调制时钟信号mck1至第四调制时钟信号mck4可具有相同的频率、相同的占空比和不同的相位。例如,第一调制时钟信号mck1可具有0

°

的相位,第二调制时钟信号mck2可具有90

°

的相位,第三调制时钟信号mck3可具有180

°

的相位,并且第四调制时钟信号mck4可具有270

°

的相位。

62.解调时钟生成电路122_2可生成多个解调时钟信号(例如,第一解调时钟信号dck1至第四解调时钟信号dck4)。第一解调时钟信号dck1至第四解调时钟信号dck4可具有相同的频率、相同的占空比和不同的相位。例如,第一解调时钟信号dck1可具有0

°

的相位,第二解调时钟信号dck2可具有90

°

的相位,第三解调时钟信号dck3可具有180

°

的相位,并且第四解调时钟信号dck4可具有270

°

的相位。在这种情况下,第一调制时钟信号mck1至第四调制时钟信号mck4可具有与第一解调时钟信号dck1至第四解调时钟信号dck4的频率相同的频率。

63.相位选择电路123可包括调制相位选择电路123_1和解调相位选择电路123_2。调制相位选择电路123_1可接收第一调制时钟信号mck1至第四调制时钟信号mck4,并且根据随机数rn输出第一调制时钟信号mck1至第四调制时钟信号mck4之一作为调制信号mod。

64.参照图4和图5,解调相位选择电路123_2可接收第一解调时钟信号dck1至第四解调时钟信号dck4,并且根据随机数rn生成第一预解调信号pdemod1至第四预解调信号pdemod4。第一预解调信号pdemod1至第四预解调信号pdemod4可具有相同的频率、相同的占空比和不同的相位。

65.解调相位选择电路123_2可包括第一选择电路s1至第四选择电路s4。第一选择电路s1至第四选择电路s4可分别接收第一解调时钟信号dck1至第四解调时钟信号dck4。

66.第一选择电路s1可基于随机数rn生成第一解调时钟信号dck1至第四解调时钟信号dck4之一作为第一预解调信号pdemod1,第二选择电路s2可基于随机数rn生成第一解调时钟信号dck1至第四解调时钟信号dck4之一作为第二预解调信号pdemod2。第三选择电路s3可基于随机数rn生成第一解调时钟信号dck1至第四解调时钟信号dck4之一作为第三预解调信号pdemod3,并且第四选择电路s4可基于随机数rn生成第一解调时钟信号dck1至第四解调时钟信号dck4之一作为第四预解调信号pdemod4。

67.在这种情况下,解调相位选择电路123_2可生成第一预解调信号pdemod1至第四预解调信号pdemod4,从而基于第一预解调信号pdemod1,第二预解调信号pdemod2具有从第一预解调信号pdemod1延迟90

°

的相位,第三预解调信号pdemod3具有从第一预解调信号pdemod1延迟180

°

的相位,并且第四预解调信号pdemod4具有从第一预解调信号pdemod1延迟270

°

的相位。例如,当第一解调时钟信号dck1被选为第一预解调信号pdemod1时,第二解调时钟信号dck2可被选为第二预解调信号pdemod2,第三解调时钟信号dck3可被选为第三预解调信号pdemod3,并且第四解调时钟信号dck4可被选为第四预解调信号pdemod4。例如,当第二解调时钟信号dck2被选为第一预解调信号pdemod1时,第三解调时钟信号dck3、第四解调时钟信号dck4和第一解调时钟信号dck1可分别被选为第二预解调信号pdemod2至第四预解调信号pdemod4。例如,当第三解调时钟信号dck3被选为第一预解调信号pdemod1时,第四解调时钟信号dck4、第一解调时钟信号dck1和第二解调时钟信号dck2可分别被选为第二预解调信号pdemod2至第四预解调信号pdemod4。可选地,例如,当第四解调时钟信号dck4被选为第一预解调信号pdemod1时,第一解调时钟信号dck1、第二解调时钟信号dck2和第三解调时钟信dck3可分别被选为第二预解调信号pdemod2至第四预解调信号pdemod4。

68.返回参照图4,延迟电路124可接收第一预解调信号pdemod1至第四预解调信号pdemod4,并且生成多个第一延迟信号ds1、多个第二延迟信号ds2、多个第三延迟信号ds3和多个第四延迟信号ds4。在一个示例实施例中,延迟电路124可被实现为缓冲器链(buffer chain)。

69.延迟电路124可通过将第一预解调信号pdemod1分别延迟指定的多个延迟相位(例如,4、10、20或40个不同的延迟相位等)来生成多个第一延迟信号ds1。例如,40个不同的延迟相位可被分别指定,并且延迟电路124可生成各个从第一预解调信号pdemod1延迟40个不同的延迟相位的40个第一延迟信号。此外,延迟电路124可通过将第二预解调信号pdemod2分别延迟指定的多个延迟相位来生成多个第二延迟信号ds2,通过将第三预解调信号pdemod3分别延迟指定的多个延迟相位来生成多个第三延迟信号ds3,并且通过将第四预解调信号pdemod4分别延迟指定的多个延迟相位来生成多个第四延迟信号ds4。

70.相位混合器125可基于地址m_addr,将通过混合多个第一延迟信号ds1获得的第一解调信号demod1中的每个提供给像素阵列110的相应像素组中的每个。例如,如果像素组的数量是40,则地址m_addr可以是1到40之间的整数。例如,第一解调信号demod1中的每个可作为第一解调信号(例如,图3的demoda)被提供给包括在相应像素组中的像素(例如,图3的111)的第一传输晶体管(例如,图3的ts1)。例如,相位混合器125可输出以与不同地址m_addr对应的不同相位排序方式而排序的多个第一延迟信号ds1作为第一解调信号demod1。

换言之,相位混合器125对多个第一延迟信号ds1的序号或索引进行不同的调整,使得当多个第一延迟信号ds1针对不同的地址m_addr被输出作为第一解调信号demod1时,多个第一延迟信号ds1中的针对不同的地址m_addr的相同序号或索引的第一延迟信号的相位是不同的。

71.相位混合器125可根据地址m_addr,通过混合多个第二延迟信号ds2,将第二解调信号demod2中的每个提供给像素阵列110的相应像素组中的每个。例如,第二解调信号demod2中的每个可作为第二解调信号(例如,图3的demodb)被提供给包括在相应像素组中的像素111的第二传输晶体管(例如,图3的ts2)。例如,相位混合器125可输出以与不同地址m_addr对应的不同相位排序方式而排序的多个第二延迟信号ds2作为第二解调信号demod2。

72.相位混合器125可根据地址m_addr,通过混合多个第三延迟信号ds3,将第三解调信号demod3中的每个提供给像素阵列110的相应像素组中的每个。例如,第三解调信号demod3中的每个可作为第三解调信号(例如,图3的demodc)被提供给包括在相应像素组中的像素111的第三传输晶体管(例如,图3的ts3)。例如,相位混合器125可输出以与不同地址m_addr对应的不同相位排序方式而排序的多个第三延迟信号ds3作为第三解调信号demod3。

73.此外,相位混合器125可根据地址m_addr,通过混合多个第四延迟信号ds4,将第四解调信号demod4中的每个提供给像素阵列110的相应像素组中的每个。例如,第四解调信号demod4中的每个可作为第四解调信号(例如,图3的demodd)被提供给包括在相应像素组中的像素111的第四传输晶体管(例如,图3的ts4)。例如,相位混合器125可输出以与不同地址m_addr对应的不同相位排序方式而排序的多个第四延迟信号ds4作为第四解调信号demod4。

74.地址m_addr可针对每个特定的时间区间而改变。例如,地址m_addr可针对每个包而改变,并且相位混合器125可输出相位针对每个包而改变的多个第一解调信号demod1至多个第四解调信号demod4。

75.多个第一解调信号demod1中的每个具有与另外的第一解调信号不同的延迟相位,多个第二解调信号demod2中的每个具有与另外的第二解调信号不同的延迟相位,多个第三解调信号demod3中的每个具有与另外的第三解调信号不同的延迟相位,并且多个第四解调信号demod3中的每个可具有与另外的第四解调信号不同的延迟相位。因此,第一解调信号demod1至第四解调信号demod4的电流分散效应可发生并且峰值电流可降低。此外,随着地址m_addr被周期性地改变,因为提供给像素阵列110的第一解调信号demod1至第四解调信号demod4的相位被周期性地改变,因此深度偏移误差可被减小。

76.图6a是示出基于随机数的调制信号和多个预解调信号的时序图。积分时间可被划分为多个包,并且随机数rn可被新分配给多个包中的每个。在一个示例实施例中,随机数rn可以是2位,并且在图6a中,随机数rn可以通过数字1至4表示。然而,示例性实施例不限于此,并且随机数rn的数量可被不同地改变。

77.参照图4和图6a,根据随机数rn,调制信号mod和多个预解调信号(例如,第一预解调信号pdemod1至第四预解调信号pdemod4)可一起被改变。调制信号mod可具有与第一预解调信号pdemod1至第四预解调信号pdemod4的周期相同的周期。在一个示例实施例中,调制

信号mod可具有50%的占空比,并且第一预解调信号pdemod1至第四预解调信号pdemod4中的每个可具有25%的占空比。然而,示例实施例不限于此,并且调制信号mod的占空比和第一预解调信号pdemod1至第四预解调信号pdemod4的占空比可被修改。

78.例如,当随机数rn是1时,调制信号mod的相位可以是0

°

,第一预解调信号pdemod1的相位可以是0

°

,第二预解调信号pdemod2的相位可以是90

°

,第三预解调信号pdemod3的相位可以是180

°

,并且第四预解调信号pdemod4的相位可以是270

°

。

79.例如,当随机数rn是2时,调制信号mod的相位可以是90

°

,第一预解调信号pdemod1的相位可以是90

°

,第二预解调信号pdemod2的相位可以是180

°

,第三预解调信号pdemod3的相位可以是270

°

,并且第四预解调信号pdemod4的相位可以是0

°

。

80.例如,当随机数rn是3时,调制信号mod的相位为180

°

,第一预解调信号pdemod1的相位可以是180

°

,第二预解调信号pdemod2的相位可以是270

°

,第三预解调信号pdemod3的相位可以是0

°

,并且第四预解调信号pdemod4的相位可以是90

°

。

81.此外,例如,当随机数rn是4时,调制信号mod的相位可以是270

°

,第一预解调信号pdemod1的相位可以是270

°

,第二预解调信号pdemod2的相位可以是0

°

,第三预解调信号pdemod3的相位可以是90

°

,并且第四预解调信号pdemod4的相位可以是180

°

。

82.调制信号mod和第一预解调信号pdemod1至第四预解调信号pdemod4可根据随机数rn而一起被改变,并且随着第一预解调信号pdemod1至第四预解调信号pdemod4被改变,第一解调信号demod1至第四解调信号demod4可被改变。随着包括在积分时间中的包的数量增加,从另外的相机输出的由光学信号导致的噪声可被转化为随机噪声分量,并且图像传感器的深度测量精度可被提高。

83.图6b是示出根据示例实施例的由图像传感器的延迟电路生成的延迟信号的时序图。参照图6b描述从第一预解调信号pdemod1生成的第一延迟信号ds1,并且相应的描述可被应用于从第二解调信号pdemod2至第四解调信号pdemod4中的每个生成的第二延迟信号ds2至第四延迟信号ds4。

84.参照图4和图6b,延迟电路124可通过将第一预解调信号pdemod1分别延迟指定的多个延迟相位来生成多个第一延迟信号ds1。例如,基于第一预解调信号pdemod1,多个第一延迟信号ds1之中的第一信号ds11的延迟时间td可以是0

×

δt,多个第一延迟信号ds1之中的第二信号ds12的延迟时间td可以是1

×

δt,多个第一延迟信号ds1之中的第三信号ds13的延迟时间td可以是2

×

δt,并且多个第一延迟信号ds1之中的第i个信号ds1i的延迟时间可以是(i-1)

×

δt。这里,i可以是自然数(例如,4、10、20或40等)。在一个示例实施例中,多个第一延迟信号ds1之中的第i个信号ds1i的延迟时间td可不超过从第一预解调信号pdemod1到第二预解调信号pdemod2的的延迟时间。

85.图7是示出根据示例实施例的图像传感器的像素阵列的框图。图8是示出根据示例实施例的基于地址提供给像素阵列的第一解调信号至第四解调信号的时序图。

86.参照图7,像素阵列110可包括多个像素组(例如,第一像素组pg1至第四十像素组pg40)。以包括在像素阵列110中的像素组的数量是40为示例。包括在像素阵列110中的像素组的数量可以是例如4、10、20或40,并且可被不同地修改。

87.第一像素组pg1至第四十像素组pg40中的每个像素组可包括至少一个像素。包括在第一像素组pg1至第四十像素组pg40之中的同一像素组中的像素可以是在列方向上并排

布置的像素,或者可以是在行方向上并排布置的像素。第一像素组pg1可包括至少一个第一像素px1,第二十像素组pg20可包括至少一个第二十像素px20,并且第四十像素组pg40可包括至少一个第四十像素px40。

88.第一信号集set1可被提供给第一像素组pg1,第二十信号集set20可被提供给第二十像素组pg20,并且第四十信号集set40可被提供给第四十像素组pg40。第一信号集set1可包括第一解调信号demod1_1至第四解调信号demod4_1,第二十信号集set20可包括第一解调信号demod1_20至第四解调信号demod4_20,并且第四十信号集set40可包括第一解调信号demod1_40至第四解调信号demod4_40。

89.第一信号集set1的第一解调信号demod1_1至第四解调信号demod4_1可彼此具有90

°

的相位差。第一信号集set1的第一解调信号demod1_1可被提供给第一像素组pg1的第一像素px1的第一传输晶体管,并且第一信号集set1的第二解调信号demod2_1可被提供给第一像素组pg1的第一像素px1的第二传输晶体管。第一信号集set1的第三解调信号demod3_1可被提供给第一像素组pg1的第一像素px1的第三传输晶体管,并且第一信号集set1的第四解调信号demod4_1可被提供给第一像素组pg1的第一像素px1的第四传输晶体管。

90.第二十信号集set20的第一解调信号demod1_20至第四解调信号demod4_20可彼此具有90

°

的相位差。第四十信号集set40的第一解调信号demod1_40至第四解调信号demod4_40可彼此具有90

°

的相位差。第一信号集set1的描述可被类似地应用于第二信号集set2至第四十信号集set40的描述。

91.参照图7和图8,积分时间可被划分为多个包,并且地址m_addr可针对多个包中的每个包而改变。在一个示例实施例中,地址m_addr可具有1至40的值。然而,示例实施例不限于此,并且地址m_addr的值的数量可以是4、10、20或40,并且可被不同地改变。

92.激活时段at可指示第一解调信号demod1至第四解调信号demod4中的每个的相位改变的时段。即,在激活时段at内,第一解调信号demod1至第四解调信号demod4中的每个的相位可根据包而改变。

93.对于相同地址m_addr,在激活时段at中,针对不同像素组的第一解调信号demod1的相位可彼此不同。即,在激活时段at内,第一信号集set1的第一解调信号demod1_1、第二十信号集set20的第一解调信号demod1_20和第四十信号集set40的第一解调信号demod1_40的相位可彼此不同。

94.此外,随着地址m_addr被改变,第一解调信号demod1中的每个的相位可在激活时段at内被改变。即,随着地址m_addr从1到40被递增地改变,第一信号集set1的第一解调信号demod1_1的相位可在激活时段at内被改变,第二十信号集set20的第一解调信号demod1_20的相位可在激活时段at内被改变,并且第四十信号集set40的第一解调信号demod1_40的相位可在激活时段at内被改变。

95.第一解调信号demod1的描述可被类似地应用于第二解调信号demod2至第四解调信号demod4。

96.因为第一解调信号demod1包括具有彼此不同的相位的信号(例如,demod1_1至demod1_40),所以可防止在第一解调信号demod1中的峰值电流的生成。此外,因为第二解调信号demod2包括具有彼此不同的相位的信号(例如,demod2_1至demod2_40),所以可防止在第二解调信号demod2中的峰值电流的生成。出于同样的原因,可防止在第三解调信号

demod3(包括具有彼此不同的相位的信号(例如,demod3_1至demod3_40))和第四解调信号demod4(包括具有彼此不同的相位的信号(例如,demod4_1至demod4_40)中的峰值电流的生成。

97.通过从延迟电路(例如,图4中的124)接收第一延迟信号ds1至第四延迟信号ds4并基于地址m_addr混合第一延迟信号ds1至第四延迟信号ds4,相位混合器(例如,图4的相位混合器125)可将相位针对每个预定时间区间(包)而改变的第一解调信号demod1至第四解调信号demod4输出到像素阵列110。地址m_addr的数量可与由延迟电路124生成的延迟信号的数量对应。因此,像素阵列110的全部像素可接收由延迟电路124生成的全部的第一延迟信号ds1至第四延迟信号ds4作为在光积分时间期间的第一解调信号demod1至第四解调信号demod4。这种操作可被称为多重交织操作。因为像素阵列110接收相位在积分区间(例如,积分时间)内改变的第一解调信号demod1至第四解调信号demod4,所以可防止发生深度偏移误差。

98.图9是用于描述提供给包括在像素阵列中的多个像素组中的每个像素组的第一解调信号的示图。图9可与图4一起参考。

99.在图9中,主要描述了从第一预解调信号pdemod1生成的第一解调信号demod1,并且与图9的描述类似的描述可被应用于从第二预解调信号pdemod2生成的第二解调信号demod2、从第三预解调信号pdemod3生成的第三解调信号demod3和从第四预解调信号pdemod4生成的第四解调信号demod4。当第一解调信号demod1中的每个具有0

°

的相位作为参考时,与第一解调信号demod1中的每个对应的第二解调信号demod2可具有90

°

的相位差,与第一解调信号demod1中的每个对应的相应第三解调信号demod3可具有180

°

的相位差,并且与第一解调信号demod1中的每个对应的相应第四解调信号demod4可具有270

°

的相位差。

100.参照图9,延迟电路124可接收第一预解调信号pdemod1,并且将多个第一延迟信号发送到相位混合器125,并且相位混合器125可将第一解调信号demod1(例如,demod1_1至demod1_40)输出到像素阵列110。相位混合器125可将第一解调信号demod1_1输出到第一像素组pg1,可将第一解调信号demod1_2输出到第二像素组pg2,并且可将第一解调信号demod1_40输出到第四十像素组pg40。

101.第一像素组pg1的第一解调信号demod1_1的相位和延迟时间td可根据地址m_addr而变化。例如,当地址m_addr改变为1、2、3、4、

……

、37、38、39或40时,第一像素组pg1的第一解调信号demod1_1的延迟时间td可改变为0

×

δt、39

×

δt、38

×

δt、37

×

δt、

……

、4

×

δt、3

×

δt、2

×

δt或1

×

δt。作为一个示例,基于参照图9描述的地址m_addr的第一解调信号demod1_1的延迟时间td的改变可被不同地修改。

102.第二像素组pg2的第一解调信号demod1_2的相位和延迟时间td可根据地址m_addr而改变。第二像素组pg2的第一解调信号demod1_2可从第一像素组pg1的第一解调信号demod1_1偏移。例如,当地址m_addr改变为1、2、3、4、

……

、37、38、39或40时,第二像素组pg2的第一解调信号demod1_2的延迟时间td可改变为1

×

δt、0

×

δt、39

×

δt、38

×

δt、

……

、5

×

δt、4

×

δt、3

×

δt或2

×

δt。

103.第四十像素组pg40的第一解调信号demod1_40的相位和延迟时间td可根据地址m_addr而改变。第四十像素组pg40的第一解调信号demod1_40可从第一像素组pg1的第一解调信号demod1_1至第三十九像素组pg39的第一解调信号demod1_39偏移。例如,当地址m_addr

改变为1、2、3、4、

……

、37、38、39或40时,第四十像素组pg40的第一解调信号demod1_40的延迟时间td可改变为39

×

δt、38

×

δt、37

×

δt、36

×

δt、...、3

×

δt、2

×

δt、1

×

δt或0

×

δt。

104.图10是用于解释根据示例实施例的包括具有4抽头结构的像素的图像传感器的操作的时序图。4抽头结构可指示具有能够在一帧中基于四个相位生成像素信号的抽头的结构。

105.参照图4和图10,延迟电路124可通过不同的延迟相位而从第一预解调信号pdemod1生成四十个第一延迟信号ds1,四十个第二延迟信号ds2可通过不同的延迟相位而从第二预解调信号pdemod2生成,四十个第三延迟信号ds3可通过不同的延迟相位而从第三预解调信号pdemod3生成,并且四十个第四延迟信号ds4可通过改变延迟相位而从第四预解调信号pdemod4生成。

106.地址m_addr可针对每个包从1到40顺序地被改变。地址m_addr的数量可与由延迟电路124生成的延迟信号的数量对应。随着地址m_addr被改变,相位混合器125可混合第一延迟信号ds1以生成第一解调信号demod1,可混合第二延迟信号ds2以生成第二解调信号demod2,可混合第三延迟信号ds3以生成第三解调信号demod3,并且可混合第四延迟信号ds4以生成第四解调信号demod4。

107.因此,积分时间内的包的总数可以是由延迟电路124基于一个预解调信号生成的延迟信号的数量(例如,第一延迟信号ds1的数量)的倍数(n倍,n是大于或等于1的自然数)。例如,当延迟电路124生成具有40个不同延迟相位的延迟信号时,在积分时间期间的包的数量可以是40的倍数。考虑到图像传感器的操作精度和图像传感器的操作速度,包的数量可被调整。

108.在根据示例实施例的图像传感器中,当包被改变,操作光源的调制信号mod与被输入到像素阵列的第一解调信号demod1至第四解调信号demod4之间的相位差可不固定,并且可针对每个包而被改变。因此,第一解调信号demod1至第四解调信号demod4具有额外的相位改变,而不管根据随机数rn的改变的调制信号mod的改变如何。通过这样,可实现具有低峰值电流和高深度测量精度的高性能相机。

109.图11是用于解释图2中示出的像素的结构的示例实施例的示图。

110.如图11中所示,像素111a可具有双抽头结构。双抽头结构指示一个像素111a包括两个抽头的结构,并且抽头可以指的是:在外部光信号通过不同相位照射时,能够区分和发送在像素111a中针对每个相位生成和积累的光电荷的单位组件。

111.包括具有双抽头结构的像素111a的图像传感器(例如,图2中的14)可使用两个抽头实现关于0

°

、90

°

、180

°

和270

°

相位的发送的方法。例如,在偶数帧(第一帧)中,基于像素111a的第一抽头,当第一抽头生成关于0

°

的相位的第一像素信号vout1时,第二抽头可生成关于180

°

的相位的第二像素信号vout2,并且在奇数帧中,第一抽头可生成关于90

°

的相位的第一像素信号vout1,并且第二抽头可生成关于270

°

的相位的第二像素信号vout2。

112.参照图11,像素111a可包括光电二极管pd、溢出门og、传输晶体管ts1和ts2、存储晶体管ss1和ss2、抽头传输晶体管txs1和txs2、复位晶体管rs1和rs2、源极跟随器sf1和sf2和选择晶体管sel1和sel2。根据一个示例实施例,溢出门og、存储晶体管ss1和ss2、抽头传输晶体管txs1和txs2、复位晶体管rx1和rx2、源极跟随器sf1和sf2和选择晶体管sel1和

sel2中的至少一个可被省略。

113.第一传输晶体管ts1可在偶数帧中根据第一解调信号demoda将由光电二极管pd生成的电荷传送到第一存储晶体管ss1,并且可以在奇数帧中根据第二解调信号demodb将由光电二极管pd生成的电荷传送到第一存储晶体管ss1。第二传输晶体管ts2可在偶数帧中根据第三解调信号demodc将由光电二极管pd生成的电荷传送到第二存储晶体管ss2,并且可在奇数帧中根据第四解调信号demodd将由光电二极管pd生成的电荷传送到第二存储晶体管ss2。第一解调信号demoda至第四解调信号demodd可被包括在图2的解调信号demod中,并且可以是彼此具有相同频率、相同占空比和不同相位的信号。第一解调信号demoda至第四解调信号demodd彼此之间可具有90

°

的相位差。例如,当第一解调信号demoda关于第一解调信号demoda具有0

°

的相位时,第二解调信号demodb可具有90

°

的相位,第三解调信号demodc可具有180

°

的相位,并且第四解调信号demodd可具有270

°

的相位。

114.像素111a可在偶数帧中的积分时间期间累积光电荷,并且将基于累积结果生成的第一像素信号vout1和第二像素信号vout2输出到读出电路(例如,图2的130)。此外,像素111a可在奇数帧中的积分时间期间累积光电荷,并且将根据累积结果生成的第一像素信号vout1和第二像素信号vout2输出到读出电路130。

115.图12和图13是用于解释根据示例实施例的包括具有双抽头结构的像素的图像传感器的操作的时序图。图12是用于解释在偶数帧中图像传感器的操作的示图,并且图13是用于解释在奇数帧中图像传感器的操作的示图。偶数帧和奇数帧可彼此交替地执行。图12和图13中的第一解调信号demod1至第四解调信号demod4中的每个可被应用于图11的第一解调信号demoda至第四解调信号demodd中的每个。

116.参照图12和图13,调制信号mod的占空比可以是50%,并且第一预解调信号pdemod1至第四预解调信号pdemod4中的每个的占空比可以是50%。然而,第一预解调信号pdemod1至第四预解调信号pdemod4中的每个的占空比可被自由地修改。

117.在偶数帧中,第一预解调信号pdemod1和第三预解调信号pdemod3可被生成。第三预解调信号pdemod3关于第一预解调信号pdemod1的相位差可以是180

°

。延迟电路(例如,图4的延迟电路124)可通过不同的延迟相位而从第一预解调信号pdemod1生成指定数量(例如,40)的第一延迟信号ds1,并且可通过改变延迟相位而从第三预解调信号pdemod3生成四十个第三延迟信号ds3。

118.在奇数帧中,第二预解调信号pdemod2和第四预解调信号pdemod4可被生成。第二预解调信号pdemod2关于第一预解调信号pdemod1的相位差可以是90

°

,并且第四预解调信号pdemod4关于第一预解调信号pdemod1的相位差可以是270

°

。延迟电路124可通过不同的延迟相位而从第二预解调信号pdemod2生成40个第二延迟信号ds2,并且可通过改变延迟相位而从第四预解调信号pdemod4生成40个第四延迟信号ds4。

119.地址m_addr可针对每个包从1到40顺序地被改变。地址m_addr的数量可与由延迟电路124生成的延迟信号的数量对应。在偶数帧中,随着地址m_addr被改变,相位混合器(例如,图4的相位混合器125)可混合第一延迟信号ds1以生成第一解调信号demod1,并且可混合第三延迟信号ds3以生成第三解调信号demod3。在奇数帧中,随着地址m_addr被改变,相位混合器125可混合第二延迟信号ds2以生成第二解调信号demod2,并且可混合第四延迟信号ds4以生成第四解调信号demod4。

120.双抽头结构具有像素的配置比4抽头结构简单的优点,并且4抽头结构与双抽头结构相比,具有基于四个相位(0

°

、90

°

、180

°

和270

°

)的像素信号可在一帧内被生成的优点。

121.图14是示出根据示例实施例的图像传感器的示意图。

122.参照图14,图像传感器1000可以是包括在垂直方向上堆叠的第一芯片cp1和第二芯片cp2的堆叠式图像传感器。参照图1描述的图像传感器14可被实现为图像传感器1000。

123.第一芯片cp1可包括像素区域pr1和垫(pad)区域pr2,并且第二芯片cp2可包括外围电路区域pr3和下垫区域pr2’。设置有多个像素px的像素阵列可被形成在像素区域pr1中,并且可包括参照图2、图7和图9描述的像素阵列110。

124.第二芯片cp2的外围电路区域pr3可包括逻辑电路块lc,并且可包括多个晶体管。例如,逻辑电路块lc可包括参照图2描述的控制电路120和读出电路130的至少一部分。外围电路区域pr3可将恒定信号提供给包括在像素区域pr1中的多个像素px中的每个,并且可读取从多个像素px中的每个输出的像素信号。

125.第二芯片cp2的下垫区域pr2’可包括下导电垫pad’。下导电垫pad’可以是多个,并且可各自与导电垫pad对应。下导电垫pad’可通过过孔结构vs电连接到第一芯片cp1的导电垫pad。

126.在一些示例实施例中,根据示例实施例,由如图1、图2、图4、图5和图9中示出的块所表示的组件、元件、模块和单元中的每个可被实现为执行以上描述的相应的功能的各种数量的硬件、软件和/或固件结构。例如,这些组件、元件、模块和单元中的至少一个可包括包含数字电路、可编程或不可编程的逻辑器件或逻辑阵列、专用集成电路(asic)、晶体管、电容器、逻辑门、或使用可通过一个或多个微处理器或其他控制设备的控制来执行相应的功能的直接电路结构(诸如,存储器、处理器、逻辑电路、查找表等)的其他电路系统的各种硬件组件。此外,这些组件、元件、模块和单元中的至少一个可包括包含用于执行指定的逻辑功能的一个或多个可执行指令并且由一个或多个微处理器或其他控制设备执行的模块、程序或代码的一部分。此外,这些组件、元件、模块和单元中的至少一个还可包括处理器(诸如,执行相应的功能的中央处理器(cpu)、微处理器等),或者可由处理器(诸如,执行相应的功能的中央处理器(cpu)、微处理器等)来实现。示例实施例的功能性方面可以以在一个或多个处理器上执行的算法实现。此外,由块或处理步骤表示的组件、元件、模块和单元可采用用于电子配置、信号处理和/或信号控制、数据处理等的任何数量的现有技术。

127.虽然已经具体示出并描述了示例实施例的方面,但是将理解,在不脱离所附权利要求的精神和范围的情况下,可在其中做出形式上和细节上的各种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1