加解密方法、装置、设备、介质和产品与流程

1.本公开涉及数据处理领域,具体地涉及一种加解密方法、装置、设备、介质和产品。

背景技术:

2.目前常用密码算法的加解密方式都是128位的,比如aes、sm1、sm4等密码算法,其相应的总线宽度也为128位。而有些密码算法本身是64位的分组数据加解密,由软件调用gmssl等开源的加解密库来实现加解密。

3.这种方式虽然加解密成本低、易于实现,但是受限于64位的分组数据加解密,加解密效率低、安全性弱,在高性能场景下无法使用。

技术实现要素:

4.鉴于上述问题,本公开提供了一种加解密方法、装置、设备、介质和产品。

5.本公开的第一个方面,提供了一种加解密方法,所述方法包括:

6.响应于接收到的明文的处理请求,拆分所述明文,得到多个部分数据,所述处理请求为加密请求或解密请求;

7.构建多个加解密模块,所述加解密模块用于加密或解密所述部分数据,所述加解密模块的数量与所述部分数据的数量相同;

8.将所述多个部分数据一一对应发送给所述多个加解密模块,以利用所述多个加解密模块对所述多个部分数据进行处理。

9.在本公开一实施例中,所述方法还包括:

10.获取所述明文的密钥;

11.在接收到所述密钥的扩展指令的情况下,扩展所述密钥,得到多组轮密钥;

12.将所述多组轮密钥依次按组发送给所述多个加解密模块,以使所述多个加解密模块利用所述多组轮密钥进行加密或解密处理。

13.在本公开一实施例中,所述将所述多个部分数据一一对应发送给所述多个加解密模块包括:

14.按照预设的发送方式,将所述多个部分数据一一对应发送给所述多个加解密模块,所述预设发送方式包括并行发送或串行发送。

15.在本公开一实施例中,所述将所述多个部分数据一一对应发送给所述多个加解密模块之前,包括:

16.获取执行所述处理请求的密码算法的应用模式;

17.基于接收到的所述明文的所述处理请求和所述应用模式,确定所述发送方式。

18.在本公开一实施例中,所述方法还包括:

19.获取所述明文的数据位数和所述加解密模块的可输入数据位数;

20.将所述明文的数据位数除以所述加解密模块的可输入数据位数,得到需构建的所述加解密模块的数量。

21.在本公开一实施例中,所述方法还包括:

22.获取所述多个加解密模块对所述多个部分数据进行处理的多个处理结果;

23.将所述多个处理结果进行重组,得到对于所述处理请求的请求结果。

24.在本公开一实施例中,执行所述处理请求的密码算法为基于sm7的密码算法;

25.所述加解密模块为f函数。

26.本公开的第二个方面提供了一种加解密装置,所述装置包括:

27.拆分模块,用于响应于接收到的明文的处理请求,拆分所述明文,得到多个部分数据,所述处理请求为加密请求或解密请求;

28.构建模块,用于构建多个加解密模块,所述加解密模块用于加密或解密所述部分数据,所述加解密模块的数量与所述部分数据的数量相同;

29.发送模块,用于将所述多个部分数据一一对应发送给所述多个加解密模块;

30.所述多个加解密模块,用于对所述多个部分数据进行处理。

31.在本公开一实施例中,加解密装置还包括:

32.密钥获取模块,用于获取所述明文的密钥;

33.密钥扩展模块,用于在接收到所述密钥的扩展指令的情况下,扩展所述密钥,得到多组轮密钥;

34.密钥发送模块,将所述多组轮密钥依次按组发送给所述多个加解密模块,以使所述多个加解密模块利用所述多组轮密钥进行加密或解密处理。

35.在本公开一实施例中,所述发送模块具体用于按照预设的发送方式,将所述多个部分数据一一对应发送给所述多个加解密模块,所述预设发送方式包括并行发送或串行发送。

36.在本公开一实施例中,加解密装置还包括:

37.模式获取模块,用于获取执行所述处理请求的密码算法的应用模式;

38.方式确定模块,用于基于接收到的所述明文的所述处理请求和所述应用模式,确定所述发送方式。

39.在本公开一实施例中,加解密装置还包括:

40.位数获取模块,用于获取所述明文的数据位数和所述加解密模块的可输入数据位数;

41.数量计算模块,用于将所述明文的数据位数除以所述加解密模块的可输入数据位数,得到需构建的所述加解密模块的数量。

42.在本公开一实施例中,加解密装置还包括:

43.结果获取模块,用于获取所述多个加解密模块对所述多个部分数据进行处理的多个处理结果;

44.结果重组模块,用于将所述多个处理结果进行重组,得到对于所述处理请求的请求结果。

45.在本公开一实施例中,执行所述处理请求的密码算法为基于sm7的密码算法;

46.所述加解密模块为f函数。

47.本公开的第三方面提供了一种电子设备,包括:一个或多个处理器;存储装置,用于存储一个或多个程序,其中,当所述一个或多个程序被所述一个或多个处理器执行时,使

得一个或多个处理器执行上述方法。

48.本公开的第四方面还提供了一种计算机可读存储介质,其上存储有可执行指令,该指令被处理器执行时使处理器执行上述方法。

49.本公开的第五方面还提供了一种计算机程序产品,包括计算机程序,该计算机程序被处理器执行时实现上述方法。

50.根据本公开提供的加解密方法、装置、设备、介质和产品,响应于接收到的明文的处理请求,拆分该明文,得到多个部分数据,该处理请求为加密请求或解密请求,构建多个加解密模块,该加解密模块用于加密或解密该部分数据,该加解密模块的数量与该部分数据的数量相同,将该多个部分数据一一对应发送给该多个加解密模块,以利用该多个加解密模块对该多个部分数据进行处理。通过构建多个加解密模块,提升加解密过程的效率和安全性,且可适配更多种总线位宽,打破受限于64位的分组数据加解密的密码算法的局限性。

附图说明

51.通过以下参照附图对本公开实施例的描述,本公开的上述内容以及其他目的、特征和优点将更为清楚,在附图中:

52.图1示意性示出了根据本公开实施例的加解密方法、装置、设备、介质和产品的应用场景图;

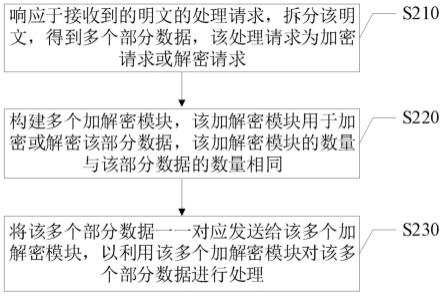

53.图2示意性示出了根据本公开实施例的加解密方法的流程图;

54.图3示意性示出了根据本公开实施例的适用于加解密方法的硬件结构示意图;

55.图4示意性示出了根据本公开实施例的加解密方法的流程图;

56.图5示意性示出了根据本公开实施例的加解密方法的流程图;

57.图6示意性示出了根据本公开实施例的加解密装置的结构框图;

58.图7示意性示出了根据本公开实施例的适于实现加解密方法的电子设备的方框图。

具体实施方式

59.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性的,而并非要限制本公开的范围。在下面的详细描述中,为便于解释,阐述了许多具体的细节以提供对本公开实施例的全面理解。然而,明显地,一个或多个实施例在没有这些具体细节的情况下也可以被实施。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本公开的概念。

60.在此使用的术语仅仅是为了描述具体实施例,而并非意在限制本公开。在此使用的术语“包括”、“包含”等表明了该特征、步骤、操作和/或部件的存在,但是并不排除存在或添加一个或多个其他特征、步骤、操作或部件。

61.在此使用的所有术语(包括技术和科学术语)具有本领域技术人员通常所理解的含义,除非另外定义。应注意,这里使用的术语应解释为具有与本说明书的上下文相一致的含义,而不应以理想化或过于刻板的方式来解释。

62.在使用类似于“a、b和c等中至少一个”这样的表述的情况下,一般来说应该按照本

领域技术人员通常理解该表述的含义来予以解释(例如,“具有a、b和c中至少一个的系统”应包括但不限于单独具有a、单独具有b、单独具有c、具有a和b、具有a和c、具有b和c、和/或具有a、b、c的系统等)。

63.在本公开的技术方案中,对数据的获取、收集、存储、使用、加工、传输、提供、公开和应用等处理,均符合相关法律法规的规定,采取了必要保密措施,且不违背公序良俗。

64.本公开提供了一种加解密方法、装置、设备、介质和产品,该方法包括:响应于接收到的明文的处理请求,拆分该明文,得到多个部分数据,该处理请求为加密请求或解密请求,构建多个加解密模块,该加解密模块用于加密或解密该部分数据,该加解密模块的数量与该部分数据的数量相同,将该多个部分数据一一对应发送给该多个加解密模块,以利用该多个加解密模块对该多个部分数据进行处理。

65.在本公开中,处理加解密的密码算法可以是基于64位的分组数据加解密的密码算法,也可以是基于32位的分组数据加解密的密码算法等等,基于64位的分组数据加解密的密码算法例如sm7算法。

66.现有sm7密码算法只包含一个f函数,该f函数用于进行加解密操作,而由于sm7密码算法规定f函数是64位的输入,因此现有的sm7密码是64位的分组加密模式。本公开以处理加解密操作的密码算法是基于64位的分组数据加解密的密码算法为例,对本公开进行示意性说明。

67.图1示意性示出了根据本公开实施例的加解密方法、装置、设备、介质和产品的应用场景图。

68.如图1所示,cpu指中央处理器,ififo和ofifo都是fifo存储设备,ififo和ofifo结构相同,其中,ififo用于存储cpu写入的明文,也即待加解密数据,该加解密装置用于对待加解密数据进行加解密处理,ofifo用于存储对待加解密数据进行加解密后得到的计算完成的数据data_out,也即对明文的处理请求的请求结果。

69.具体的,在图1所示应用场景图具体工作时,cpu写入待加解密数据data_in至ififo,cpu配置加解密场景state、密码算法的应用模式mode和加解密密钥key至加解密装置,加解密装置从ififo中读取待加解密数据data_in,然后加解密装置对待加解密数据data_in和密钥key完成加解密操作,得到计算完成的数据data_out,然后将计算完成的数据data_out写入ofifo,等待ofifo中存储的计算完成的数据data_out的数据量符合期望值后,cpu从ofifo将计算完成的数据data_out读出。

70.可理解的,若ofifo中存储的计算完成的数据data_out的数据量不符合期望值,则加解密装置从ififo中再次读取新的待加解密数据data_in进行加解密,直至符合期望值。期望值是指总共需加解密的数据除以每次加解密的数据的值,例如,用户需加密48字节的数据,且需将48字节的数据分为3个16字节数据加密,则期望值为3。

71.以下将基于图1描述的场景,通过图2~图5对公开实施例的加解密方法进行详细描述。

72.图2示意性示出了根据本公开实施例的加解密方法的流程图。

73.如图2所示,该实施例的加解密方法包括操作s210~操作s230。

74.在操作s210,响应于接收到的明文的处理请求,拆分该明文,得到多个部分数据,该处理请求为加密请求或解密请求。

75.在操作s220,构建多个加解密模块,该加解密模块用于加密或解密该部分数据,该加解密模块的数量与该部分数据的数量相同。

76.在操作s230,将该多个部分数据一一对应发送给该多个加解密模块,以利用该多个加解密模块对该多个部分数据进行处理。

77.在本公开中,该明文即待加解密数据,对待加解密数据进行拆分,可以得到的多个部分数据,每个部分数据位数均相同。对于需要分的部分数据的个数,可以基于加解密模块可以输入或处理的单个部分数据的位数而定,本公开对此不做限制。例如,待加解密数据为256位,加解密模块可以输入或处理的单个部分数据的位数为128位,则多个部分数据为两个部分数据,又例如,加解密模块可以输入或处理的单个部分数据的位数为64位,则多个部分数据为四个部分数据。

78.在本公开一实施例中,获取该明文的数据位数和该加解密模块的可输入数据位数,将该明文的数据位数除以该加解密模块的可输入数据位数,得到需构建的该加解密模块的数量。

79.可以理解的是,如需要适配64*n位的总线架构,则只需要用n块加解密模块。例如,待加解密数据为256位,则构建四块相同的加解密模块,在执行处理请求的密码算法为基于sm7的密码算法的情况下,构建四块相同的f函数即可。又例如,待加解密数据为512位,则构建八块相同的加解密模块。如图3所示,以待加解密数据data为128位为例,加解密模块的数量为2个,主控制器执行操作s210~操作s230。

80.在本公开中,将该多个部分数据一一对应发送给该多个加解密模块,例如,如图3所示,加解密模块的数量等于部分数据的数量为2,即,多个部分数据包括第一部分数据和第二部分数据,多个加解密模块包括第一加解密模块和第二加解密模块,将该多个部分数据一一对应发送给该多个加解密模块,也即,将第一部分数据发送给第一加解密模块以及将第二部分数据发送给第二加解密模块,或者,将第一部分数据发送给第二加解密模块以及将第二部分数据发送给第一加解密模块,本公开对此不做限制。

81.根据本公开实施例,响应于接收到的明文的处理请求,拆分该明文,得到多个部分数据,该处理请求为加密请求或解密请求,构建多个加解密模块,该加解密模块用于加密或解密该部分数据,该加解密模块的数量与该部分数据的数量相同,将该多个部分数据一一对应发送给该多个加解密模块,以利用该多个加解密模块对该多个部分数据进行处理。通过构建多个加解密模块,提升加解密过程的效率和安全性,且可适配更多种总线位宽,打破受限于64位的分组数据加解密的密码算法的局限性。

82.在本公开一实施例中,执行该处理请求的密码算法为基于sm7的密码算法,该加解密模块为f函数。可使用多个f函数,使得sm7密码算法的性能和安全性得到明显提升,同时可适配更多种总线位宽,打破sm7密码算法仅64位分组加密的局限性。

83.在本公开一实施例中,获取该多个加解密模块对该多个部分数据进行处理的多个处理结果,将该多个处理结果进行重组,得到对于该处理请求的请求结果。

84.图4示意性示出了根据本公开实施例的加解密方法的流程图。

85.如图4所示,该实施例的加解密方法除了包括操作s210~操作s230之外,还包括操作s410~操作s430。

86.在操作s410,获取该明文的密钥。

87.在操作s420,在接收到该密钥的扩展指令的情况下,扩展该密钥,得到多组轮密钥。

88.在操作s430,将该多组轮密钥依次按组发送给该多个加解密模块,以使该多个加解密模块利用该多组轮密钥进行加密或解密处理。

89.在本公开中,所有加解密模块使用的轮密钥均相同,在一示例中,如图3所示,执行该处理请求的密码算法为基于sm7的密码算法为例,待加解密数据为128位,则128位密钥key经拓展后可以变成16组96位的轮密钥round_key。将16组96位的轮密钥一组一组依次发送给2个加解密模块,直至完成所有加解密轮数。

90.在本公开一实施例中,对于扩展密钥后得到的多组轮密钥,可以对其进行存储,以用于下次加解密,减少密钥扩展次数。

91.在本公开中,若当前已存在待加解密数据的密钥,则无需进行密钥扩展,若当前不存在待加解密数据的密钥,则需进行密钥扩展。例如,输入数据为256位,适配64*2位的总线架构,也即加解密模块的数量为2,加解密模块可输入的数据为64位,则将输入数据为256位分为两个128位的待加解密数据,对于第一个待加解密数据,当前不存在待加解密数据的密钥,则发出密钥的扩展指令,利用图2所示方法处理,得到多组轮密钥,对于第二个待加解密数据,当前存在待加解密数据的密钥,则无需发出密钥的扩展指令,获取基于第一个待加解密数据的多组轮密钥即可。

92.更多的,用于还可以通过配置密钥扩展位进行控制,配置密钥扩展位则发出密钥扩展指令,不配置密钥扩展位,则不发出密钥扩展指令。

93.可以理解的,在本公开中,在加解密模块用于加密部分数据的情况下,多组轮密钥按顺序依次发送给多个加解密模块,在加解密模块用于解密部分数据的情况下,多组轮密钥按逆序依次发送给多个加解密模块。

94.在本公开一实施例中,按照预设的发送方式,将该多个部分数据一一对应发送给该多个加解密模块,该预设发送方式包括并行发送或串行发送。

95.并行模式下,128位待加解密数据经过拆分处理后,生成两个64位部分数据,两个64位部分数据同时发送给两个加解密模块。两个加解密模块同时启动也同时完成。在收到两个加解密模块处理完成的done信号之后,将两个加解密模块加解密处理后得到的两个64位数据重组为128位。在并行模式下,两个加解密模块同时工作,加密速度会提高一倍。

96.串行模式下,128位待加解密数据经过拆分处理后,生成两个64位部分数据,一个64位部分数据发送给一加解密模块进行处理,得到的处理结果保存至寄存器。待该一加解密模块运算完成,将另一个64位部分数据发送给另一加解密模块,待收到另一加解密模块的dnoe信号后,将两个加解密模块加解密处理后得到的两个64位数据重组为128位。

97.图5示意性示出了根据本公开实施例的加解密方法的流程图。

98.如图5所示,该实施例的加解密方法除了包括操作s210~操作s230之外,还包括操作s510~操作s520。

99.在操作s510,获取执行该处理请求的密码算法的应用模式。

100.在操作s520,基于接收到的该明文的该处理请求和该应用模式,确定该发送方式。

101.在本公开中,处理请求的密码算法的应用模式mode,例如ecb、cbc、ctr、cfb、ofb等等。如表1所示,本公开以ecb、cbc、ctr、cfb、ofb为例,示意性的说明发送方式的确定结果。

[0102][0103]

可理解的,以上仅为一种示意性示例,本领域技术人员可根据实际情况和需要对其做出适应性改变。

[0104]

在本公开一实施例中,如果待加解密数据和密钥不符合指定格式,可以在加解密模块进行加解密之前,对待加解密数据和密钥进行数据流处理。以密钥和明文都是12345678为例,在硬件中输入的密钥和明文可能是78563412的格式存储,故通过对待加解密数据和密钥进行数据流处理,可以解密待加解密数据和密钥格式不匹配的问题。

[0105]

基于上述图2至图5所示方法,本公开还提供了一种加解密装置。以下将结合图6对该加解密装置进行详细描述,结合图6对该加解密装置进行详细描述。

[0106]

图6示意性示出了根据本公开实施例的加解密装置的结构框图。

[0107]

如图6所示,该实施例的加解密装置600包括拆分模块610、构建模块620、发送模块630和加解密模块640。

[0108]

拆分模块610用于响应于接收到的明文的处理请求,拆分该明文,得到多个部分数据,该处理请求为加密请求或解密请求。在一实施例中,拆分模块610可以用于执行前文描述的操作s210,在此不再赘述。

[0109]

构建模块620用于构建多个加解密模块,该加解密模块用于加密或解密该部分数据,该加解密模块的数量与该部分数据的数量相同。在一实施例中,构建模块620可以用于执行前文描述的操作s220,在此不再赘述。

[0110]

发送模块630用于将该多个部分数据一一对应发送给该多个加解密模块。在一实施例中,发送模块630可以用于执行前文描述的操作s230,在此不再赘述。

[0111]

该多个加解密模块640,用于对该多个部分数据进行处理。

[0112]

在本公开一实施例中,加解密装置600还包括:

[0113]

密钥获取模块,用于获取该明文的密钥;

[0114]

密钥扩展模块,用于在接收到该密钥的扩展指令的情况下,扩展该密钥,得到多组轮密钥;

[0115]

密钥发送模块,将该多组轮密钥依次按组发送给该多个加解密模块,以使该多个加解密模块利用该多组轮密钥进行加密或解密处理。

[0116]

在本公开一实施例中,该发送模块630具体用于按照预设的发送方式,将该多个部分数据一一对应发送给该多个加解密模块,该预设发送方式包括并行发送或串行发送。

[0117]

在本公开一实施例中,加解密装置600还包括:

[0118]

模式获取模块,用于获取执行该处理请求的密码算法的应用模式;

[0119]

方式确定模块,用于基于接收到的该明文的该处理请求和该应用模式,确定该发送方式。

[0120]

在本公开一实施例中,加解密装置600还包括:

[0121]

位数获取模块,用于获取该明文的数据位数和该加解密模块的可输入数据位数;

[0122]

数量计算模块,用于将该明文的数据位数除以该加解密模块的可输入数据位数,得到需构建的该加解密模块的数量。

[0123]

在本公开一实施例中,加解密装置600还包括:

[0124]

结果获取模块,用于获取该多个加解密模块对该多个部分数据进行处理的多个处理结果;

[0125]

结果重组模块,用于将该多个处理结果进行重组,得到对于该处理请求的请求结果。

[0126]

在本公开一实施例中,执行该处理请求的密码算法为基于sm7的密码算法;

[0127]

该加解密模块为f函数。

[0128]

根据本公开的实施例,拆分模块610、构建模块620、发送模块630和加解密模块640中的任意多个模块可以合并在一个模块中实现,或者其中的任意一个模块可以被拆分成多个模块。或者,这些模块中的一个或多个模块的至少部分功能可以与其他模块的至少部分功能相结合,并在一个模块中实现。根据本公开的实施例,拆分模块610、构建模块620、发送模块630和加解密模块640中的至少一个可以至少被部分地实现为硬件电路,例如现场可编程门阵列(fpga)、可编程逻辑阵列(pla)、片上系统、基板上的系统、封装上的系统、专用集成电路(asic),或可以通过对电路进行集成或封装的任何其他的合理方式等硬件或固件来实现,或以软件、硬件以及固件三种实现方式中任意一种或以其中任意几种的适当组合来实现。或者,拆分模块610、构建模块620、发送模块630和加解密模块640中的至少一个可以至少被部分地实现为计算机程序模块,当该计算机程序模块被运行时,可以执行相应的功能。

[0129]

图7示意性示出了根据本公开实施例的适于实现加解密方法的电子设备的方框图。

[0130]

如图7所示,根据本公开实施例的电子设备700包括处理器701,具可以根据存储在只读存储器(rom)702中的程序或者从存储部分708加载到随机访问存储器(ram)703中的程序而执行各种适当的动作和处理。处理器701例如可以包括通用微处理器(例如cpu)、指令集处理器和/或相关芯片组和/或专用微处理器(例如,专用集成电路(asic))等等。处理器701还可以包括用于缓存用途的板载存储器。处理器701可以包括用于执行根据本公开实施例的方法流程的不同动作的单一处理单元或者是多个处理单元。

[0131]

在ram 703中,存储有电子设备700操作所需的各种程序和数据。处理器701、rom 702以及ram 703通过总线704彼此相连。处理器701通过执行rom 702和/或ram 703中的程序来执行根据本公开实施例的方法流程的各种操作。需要注意,所述程序也可以存储在除rom 702和ram 703以外的一个或多个存储器中。处理器701也可以通过执行存储在所述一个或多个存储器中的程序来执行根据本公开实施例的方法流程的各种操作。

[0132]

根据本公开的实施例,电子设备700还可以包括输入/输出(i/o)接口705,输入/输出(i/o)接口705也连接至总线704。电子设备700还可以包括连接至i/o接口705的以下部件中的一项或多项:包括键盘、鼠标等的输入部分706;包括诸如阴极射线管(crt)、液晶显示器(lcd)等以及扬声器等的输出部分707;包括硬盘等的存储部分708;以及包括诸如lan卡、

调制解调器等的网络接口卡的通信部分709。通信部分709经由诸如因特网的网络执行通信处理。驱动器710也根据需要连接至i/o接口705。可拆卸介质711,诸如磁盘、光盘、磁光盘、半导体存储器等等,根据需要安装在驱动器710上,以便于从其上读出的计算机程序根据需要被安装入存储部分708。

[0133]

本公开还提供了一种计算机可读存储介质,该计算机可读存储介质可以是上述实施例中描述的设备/装置/系统中所包含的;也可以是单独存在,而未装配入该设备/装置/系统中。上述计算机可读存储介质承载有一个或者多个程序,当上述一个或者多个程序被执行时,实现根据本公开实施例的方法。

[0134]

根据本公开的实施例,计算机可读存储介质可以是非易失性的计算机可读存储介质,例如可以包括但不限于:便携式计算机磁盘、硬盘、随机访问存储器(ram)、只读存储器(rom)、可擦式可编程只读存储器(eprom或闪存)、便携式紧凑磁盘只读存储器(cd-rom)、光存储器件、磁存储器件、或者上述的任意合适的组合。在本公开中,计算机可读存储介质可以是任何包含或存储程序的有形介质,该程序可以被指令执行系统、装置或者器件使用或者与其结合使用。例如,根据本公开的实施例,计算机可读存储介质可以包括上文描述的rom 702和/或ram 703和/或rom 702和ram 703以外的一个或多个存储器。

[0135]

本公开的实施例还包括一种计算机程序产品,其包括计算机程序,该计算机程序包含用于执行流程图所示的方法的程序代码。当计算机程序产品在计算机系统中运行时,该程序代码用于使计算机系统实现本公开实施例所提供的加解密方法。

[0136]

在该计算机程序被处理器701执行时执行本公开实施例的系统/装置中限定的上述功能。根据本公开的实施例,上文描述的系统、装置、模块、单元等可以通过计算机程序模块来实现。

[0137]

在一种实施例中,该计算机程序可以依托于光存储器件、磁存储器件等有形存储介质。在另一种实施例中,该计算机程序也可以在网络介质上以信号的形式进行传输、分发,并通过通信部分709被下载和安装,和/或从可拆卸介质711被安装。该计算机程序包含的程序代码可以用任何适当的网络介质传输,包括但不限于:无线、有线等等,或者上述的任意合适的组合。

[0138]

在这样的实施例中,该计算机程序可以通过通信部分709从网络上被下载和安装,和/或从可拆卸介质711被安装。在该计算机程序被处理器701执行时,执行本公开实施例的系统中限定的上述功能。根据本公开的实施例,上文描述的系统、设备、装置、模块、单元等可以通过计算机程序模块来实现。

[0139]

根据本公开的实施例,可以以一种或多种程序设计语言的任意组合来编写用于执行本公开实施例提供的计算机程序的程序代码,具体地,可以利用高级过程和/或面向对象的编程语言、和/或汇编/机器语言来实施这些计算程序。程序设计语言包括但不限于诸如java,c++,python,“c”语言或类似的程序设计语言。程序代码可以完全地在用户计算设备上执行、部分地在用户设备上执行、部分在远程计算设备上执行、或者完全在远程计算设备或服务器上执行。在涉及远程计算设备的情形中,远程计算设备可以通过任意种类的网络,包括局域网(lan)或广域网(wan),连接到用户计算设备,或者,可以连接到外部计算设备(例如利用因特网服务提供商来通过因特网连接)。

[0140]

附图中的流程图和框图,图示了按照本公开各种实施例的系统、方法和计算机程

序产品的可能实现的体系架构、功能和操作。在这点上,流程图或框图中的每个方框可以代表一个模块、程序段、或代码的一部分,上述模块、程序段、或代码的一部分包含一个或多个用于实现规定的逻辑功能的可执行指令。也应当注意,在有些作为替换的实现中,方框中所标注的功能也可以以不同于附图中所标注的顺序发生。例如,两个接连地表示的方框实际上可以基本并行地执行,它们有时也可以按相反的顺序执行,这依所涉及的功能而定。也要注意的是,框图或流程图中的每个方框、以及框图或流程图中的方框的组合,可以用执行规定的功能或操作的专用的基于硬件的系统来实现,或者可以用专用硬件与计算机指令的组合来实现。

[0141]

本领域技术人员可以理解,本公开的各个实施例和/或权利要求中记载的特征可以进行多种组合或/或结合,即使这样的组合或结合没有明确记载于本公开中。特别地,在不脱离本公开精神和教导的情况下,本公开的各个实施例和/或权利要求中记载的特征可以进行多种组合和/或结合。所有这些组合和/或结合均落入本公开的范围。

[0142]

以上对本公开的实施例进行了描述。但是,这些实施例仅仅是为了说明的目的,而并非为了限制本公开的范围。尽管在以上分别描述了各实施例,但是这并不意味着各个实施例中的措施不能有利地结合使用。本公开的范围由所附权利要求及其等同物限定。不脱离本公开的范围,本领域技术人员可以做出多种替代和修改,这些替代和修改都应落在本公开的范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1