一种电子倍增CCD用三电平高压驱动转换电路的制作方法

一种电子倍增ccd用三电平高压驱动转换电路

1.技术领域:本发明涉及电子倍增ccd技术领域,具体是一种电子倍增ccd用三电平高压驱动转换电路。

2.

背景技术:

电子倍增ccd技术属于微光成像领域,电子倍增ccd电路具有灵敏度高、噪声低、量子效率高等优势。部分电子倍增ccd图像传感器工作时需要施加三种电平信号,分别是低电平、中电平和高电平,为电子倍增ccd提供倍增驱动信号。为了实现更好的成像效果,对电子倍增ccd倍增级的输入信号幅值有更高的要求,一般需达到20v~50v。当倍增级的输入信号幅值低于20v时将不会产生碰撞电离效应,像元内倍增工作时需要高电平高压驱动信号,非倍增时需要中低电平驱动信号。

3.目前市场上ccd驱动时序信号设计大多采用主控模块产生ttl电平信号,然后再对时序信号进行功率驱动,产生满足ccd时序的驱动信号。但因为fpga等主控芯片只有“0”和“1”两种逻辑状态,这样产生的驱动信号只有高电平和低电平两种状态,而无法产生第三种电平信号,需要自行设计电子倍增ccd专用的三电平高压驱动转换电路。

4.经过对现有专利检索,中国实用新型专利《一种ccd专用三电平驱动电路》(授权号cn203563048u),实现了一种ccd图像传感器电路专用的三电平驱动电路,但无法提供电子倍增ccd工作所需的高压驱动信号。中国发明专利《一种用于emccd的数控高压倍增电路》(专利号cn104735370b),包括直流电平转换电路、数模转换电路和推挽驱动电路,提供了一种用于emccd的数控高压倍增电路,满足倍增稳定性,具备小型化和低功耗的特点,该专利提供了一种ccd倍增所需的数控高压倍增电路,但没有解决电子倍增ccd工作所需的三电平驱动信号。光学技术期刊第33卷第五期《三电平阶梯波形ccd时序驱动电路设计》介绍了一种驱动ccd芯片所需的三电平驱动电路,但无法提供电子倍增ccd工作所需的高压驱动信号。

5.

技术实现要素:

本发明的目的就是要解决现有技术中存在的缺点提供的一种电子倍增ccd用三电平高压驱动转换电路。

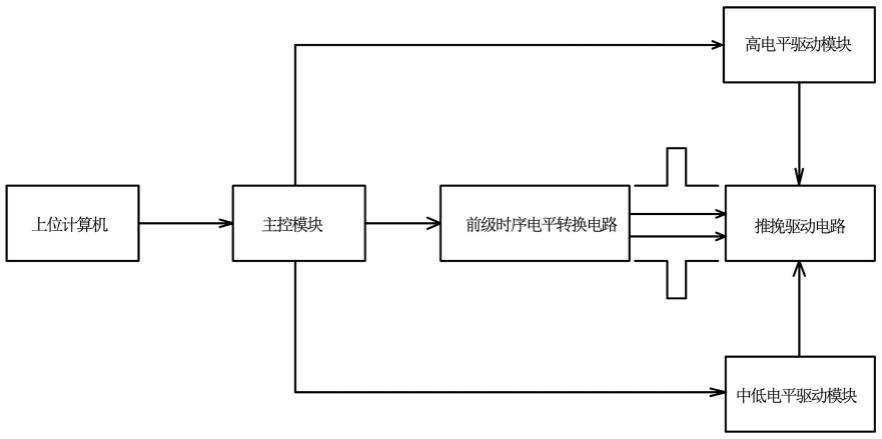

6.本发明采用了如下技术方案:一种电子倍增ccd用三电平高压驱动转换电路,包括依次连接的上位计算机和主控模块,主控模块分别连接前极时序电平转换电路、高电平驱动模块和中低电平驱动模块,前极时序电平转换电路、高电平驱动模块和中低电平驱动模块分别连接推挽驱动电路。

7.上位计算机将设置的高低电平值转换为数字信号传输给主控模块,再由主控模块控制高电平驱动模块和中低电平驱动模块输出相应的高电平及中低电平作为推挽驱动电路的驱动信号;主控模块输出一路时序控制信号,经前极时序电平转换电路转换为两路相位相反、电平幅度增加的时序信号,作为后级推挽式驱动电路的时序信号。

8.所述推挽式驱动电路选用参数匹配的一对nmos管和pmos作为功率驱动芯片。

9.发明的有益效果

电子倍增ccd的三电平驱动转换电路可通过主控模块任意调节驱动信号的高中低三路电平值,波形建立时间达到纳秒级,同时高电平驱动电压可超过35v,满足电子倍增ccd像元内倍增需要的高压驱动信号要求,可方便任意设置电子倍增ccd电路的三电平倍增驱动信号,以达到其最佳成像效果。

10.本发明的一种电子倍增ccd用三电平高压驱动转换电路,可同时输出幅度可调的三电平高压驱动信号,为电子倍增ccd器件提供倍增工作所需的三电平时钟脉冲信号。为了使时钟脉冲信号能够驱动电子倍增ccd输入管脚的高容性负载,需要脉冲信号源具备较强的瞬间大电流驱动能力,脉冲信号源的三种电平(高电平、中电平和低电平)均可根据需要实时调节电平幅度。

11.附图说明:图1是本发明的原理框图;图2是本发明的电路原理图。

12.具体实施方式:下面结合附图对本发明作进一步描述。以下实施例仅用于更加清楚地说明本发明的技术方案,而不能以此来限制本发明的保护范围。

13.如图1所示,本发明提供的一种电子倍增ccd用三电平高压驱动转换电路,包括依次连接的上位计算机和主控模块,主控模块分别连接前极时序电平转换电路、高电平驱动模块和中低电平驱动模块,前极时序电平转换电路、高电平驱动模块和中低电平驱动模块分别连接推挽驱动电路。

14.上位计算机将设置的高低电平值转换为数字信号传输给主控模块,再由主控模块控制高电平驱动模块和中低电平驱动模块输出相应的高电平及中低电平作为推挽驱动电路驱动信号。主控模块输出一路时序控制信号,经前极时序电平转换电路转换为两路相位相反、电平幅度增加的时序信号,作为后级推挽式驱动电路的时序信号。

15.三电平驱动电路工作时序可拆分为两种工作状态,即高电平-》低电平和中电平-》低电平。高、中、低三种电平状态,低电平和中电平即常规数字信号的“0”和“1”两种逻辑状态,高电平即电子倍增ccd倍增级所需的高压驱动信号,一般需达到20v~50v。

16.当选择高电平-》低电平工作状态时,中低电平驱动模块输出低电平,高电平驱动模块输出高电平,输入到n型mos管和p型mos管栅极的信号电平幅度一致,相位相反,两个mos管交替导通,产生高低电平时钟驱动信号。

17.当选择中电平-》低电平工作状态时,n型mos管持续断开,p型mos管持续导通,中低电平驱动模块el7156输出中低电平脉冲驱动信号,由nmos管驱动输出给电子倍增ccd。通过程序控制,即实现了电子倍增ccd所需的三电平高压驱动模块设计。

18.如图2所示,主控模块输出两路控制信号,一路控制信号(即图2的中低电平驱动模块输入信号)输出给中低电平驱动模块作为输入信号,通过电阻r2连接到运放u1(el7156)的3脚。

19.中低电平转换模块由el7156及其外围电路组成,el7156模块的主要作用是对主控模块发出的控制信号(中低电平驱动模块输入信号)进行电平转换和扩流,为推挽驱动电路提供中低电平驱动信号,再经由推挽驱动电路输出给ccd的倍增信号端。

20.由于常规数字信号通道板输出电平可以满足电子倍增ccd常规驱动信号电平幅度

的要求,但因为电子倍增ccd输入管脚均为高容性负载(达到nf级),不能使用通道板直接驱动,否则会因为充电时间过长而导致波形上升边沿变缓,进而影响工作频率。

21.所以在电子倍增ccd中低电平驱动模块上选择高速集成驱动芯片,用以提供驱动能力。选择el7156芯片对主控模块发出的驱动信号进行电平转换和扩流。el7156是单路ttl驱动芯片,具有3.5a的峰值驱动电流,完全符合电子倍增ccd输入端驱动要求。

22.el7156集成芯片的1脚和5脚接电源端v+、v-,分别为电路提供固定的正负电源,4脚接地。el7156的8脚和6脚为中电平电压输入端和低电平电压输入端,c3、c5两个电容和电阻r7组成一个直流滤波网络,用于对输入到8脚的直流电平进行滤波。c4、c6两个电容和电阻r8组成一个直流滤波网络,用于对输入到6脚的直流电平进行滤波,可根据需要设置三电平驱动电路的中低电平,如通过可编程数模转换器设置中电平驱动电压和低电平驱动电压给el7156的8脚和6脚进行设置,通过el7156电路的7脚输出交流波形的中低电平,电阻r1为输出中低电平的限流电阻。el7156电路的3脚为输入波形端,接入主控模块的输入信号工作波形(即中低电平驱动模块输入信号),输入信号的工作波形经驱动芯片el7156转换为频率不变、可编程控制输出波形的中低电平,中低电平驱动波形连接到推挽驱动电路q1源极。el7156电路的2脚为使能端,由主控模块控制el7156芯片工作与否。

23.图2中,高电平驱动模块由电阻r14、电容c11和电容c12组成,电阻r14输入端连接高电平驱动电压,电容c11连接于电阻r14输入端、另一端接地;电阻r14输出端作为高电平驱动模块输出端,该段连接电容c12,电容c12另一端接地。

24.图2中高电平驱动模块为可编程直流电压,由上位计算机控制可编程电源直接设置高电平驱动电压。

25.推挽式驱动电路选用参数匹配的一对nmos管和pmos作为功率驱动芯片,具有漏-源极耐压值高,导通电阻小,驱动能力强等特点。pmos管q1、nmos管q2和电阻r9、r10、r11、r12、r13组成推挽驱动电路,电阻r12和q2的源端相连,电阻r13和q1的漏端相连,作用是限制mos管漏极电流,防止电流异常对mos管造成损伤,起保护作用。q1、q2的栅极分别连接电阻r11、r10的一端,电阻r10、r11的另一端分别连接于前级时序转换电路的运放u2(si8271)的6脚和7脚,所述电阻r10、r11的另一端并联电阻r9。

26.所述中低电平驱动模块的输出的中低电平连接q1的源极,高电平驱动模块的输出高电平连接q2的漏极。

27.当输入到n型mos管q2栅极的信号电平由高变低时,输入到p型mos管q1栅极的信号保持低电平,n型mos管导通,p型mos管断开,倍增极信号输出高电平;当输入到p型mos管栅极的信号电平由低变高时,输入到n型mos管栅极的信号保持高电平,p型mos管导通,n型mos管断开,倍增极信号输出由高电平变低电平,避免了两管同时导通。

28.推挽式驱动电路经由时序信号的控制,选择高电平驱动模块和中低电平驱动模块作为驱动信号的高中低电平。

29.前级时序转换电路由运放u2 si8271及其外围电路构成,主要作用是将主控模块输入的一路时序控制信号转换为两路频率相同,相位相反的驱动信号。一路由si8271的7脚vo+端连接至推挽驱动电路的r11,一路由si8271的6脚vo-端连接至推挽驱动电路的r10。同时7脚vo+端连接至d1 bat54s的3脚,bat54s为双二极管,1脚连接至-10v,2脚连接至+20v,bat54s用于输出电压钳位,使输出电位钳位在-10.32v~20.32v之间。

30.6脚vo-端连接至d2 bat54s的3脚,d2的1脚连接至-10v,2脚连接至+20v,用于输出电压钳位。电路8脚接至+20v电源电压,同时接d4,d5两个稳压二极管到地,d4,d5作用是正电源稳压,同时接1u电容c8到地,起滤波作用。电路5脚接至-10v电源电压,同时接d3稳压二极管到地,d3作用是负电源稳压,同时接1u电容c9到地,起滤波作用。电路2脚vddi和4脚en使能端短接,并连接至5v电源端,同时接1u电容c7到地,起滤波作用。3脚gndi接到地端。1脚vi接电阻r5至主控模块的时序输出端,接受主控模块输入的时序控制信号,同时接电阻r6到地。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1