成像方法、传感器、3D形状重建方法及系统与流程

本发明一般地涉及智能互补金属氧化物半导体(cmos)图像传感器和3d测量和/或重建。更具体地,本发明涉及一种成像方法、图像传感器、3d形状重建方法和成像系统。

背景技术:

1、传统的图像传感器输出整张图像,其中可能包含许多无用的信息。例如,在3d激光扫描仪中,当激光线扫描被拍摄的对象时,亮像素的位置及强度是所需信息,而暗像素并不需要被进一步处理和计算。在这种情况下,输出暗像素的强度将导致传感器的高带宽要求以及低读出速度。

2、为了解决这个问题,本发明提出了一种降低输出带宽要求并提高模数转换器(adc)速度的成像方法和新颖的智能cmos图像传感器,以及使用根据本发明的高速智能cmos图像传感器和结构光重建对象的3d信息的方法和系统。

3、申请内容

4、本发明的一方面提出了一种具有像素选择的成像方法,包括:根据规则从一个或多个像素中选择像素;仅输出选定像素的位置或选定像素的位置和强度;通过多个并行i/o导出数据;以及通过快速导出架构来促进数据导出。

5、在一些实施例中,在输出该选定像素之前,方法还包括以下至少一项或多项:通过模数转换器将该选定像素的强度转换为数字信号;在促进数据导出的情况下,通过将所述选定像素的数据分配到多个单位中,对行上的所述选定像素进行重布线;以及存储该选定像素的数据到存储缓冲器。

6、在一些实施例中,输出该选定像素包括以下至少一项或多项:通过一个并行i/o导出一列或多列中的数据,其中,在该选定像素经过了重新布线的情况下,通过该多个并行i/o中的一个i/o通道输出一个重布线单元中的该选定像素的强度,以及选定像素的位置是在一个并行i/o中列的编码;以及输出全局标志,该全局标志用于指示以下一项或多项:待通过该并行i/o导出的选定像素的数量,是否存在待导出的选定像素,以及数据导出的工作模式。

7、在一些实施例中,根据如下规则中的至少一个规则选择像素:像素的强度大于第一阈值;或者像素与其相邻列像素的强度差大于第二阈值。第一阈值和第二阈值设置为用户自定义值,或者为当与一个或多个像素相关的光源关闭时的强度,或者为当该光源关闭时区域内所有像素的平均强度,其中该区域为一行、一列或一个图像。

8、在一些实施例中,通过将所述选定像素的数据分配到多个单位中,对行上的所述选定像素进行重布线包括:将行中相连接的若干选定像素的数据分割为一个或多个单元;以及将所述若干选定像素的分割数据平均分配到一个或多个并行i/o以进行数据导出。

9、在一些实施例中,该通过模数转换器将该选定像素的强度转换为数字信号包括以下至少一项或多项:对该一个或多个像素中的每个像素:生成与该像素相关的标志;

10、如果该像素被选定,将该标志设置为激活,以及如果该像素未被选定,将该标志设置为非激活;以及在与该像素相关的该标志为激活的情况下,将该像素的强度转换为数字信号;通过一个或多个并行模数转换器对对应于一个并行i/o的数据同时进行ad转换;以及通过一个并行模数转换器在每个周期输出一位数字数据,直到该数据完全转换为数字数据,通过n个并行ad转换器在每个周期同时输出n位数字数据,直到该数据完全转换为数字数据。

11、在一些实施例中,该模数转换器为逐次逼近型模数转换器,以及本方法还包括:从该一个或多个像素中选择像素,同时通过该逐次逼近型模数转换器将该像素转换为数字信号。

12、在一些实施例中,ad转换和数据通信采用交错时序:当该模数转换器在转换数据时,下一行的数据被开始读出。

13、在一些实施例中,该存储该选定像素的数据到存储缓冲器包括以下至少一项或多项:将对应于一个i/o的像素的数据移入一个或多个存储缓冲器,其中,该存储缓冲器的数量小于对应于同一个i/o的像素的数量;和/或通过基于进位超前加法器逻辑的控制器将该选定像素的数据移入该存储缓冲器;在该存储缓冲器为fifo存储器的情况下,逐位移入和移出数据;在该存储缓冲器为fifo存储器的情况下,并行移入和移出一批多位数据;以及当下一个强度数据被转换为数字数据时,清空该存储缓冲器中的数据。

14、在一些实施例中,本方法还包括:通过时钟信号控制操作时序;以及通过增设缓冲器以消除信号延迟,其中该缓冲器具有分层结构。

15、本发明的另一个方面还提出了一种图像传感器,包括:像素阵列中的一个或多个像素;与该像素阵列相伴的像素选择电路,用于根据规则选择像素;与该像素选择电路相伴的一个或多个并行i/o,用于输出选定像素的位置或选定像素的位置和强度;以及与该多个并行i/o相伴的快速导出架构,用于促进数据导出。

16、在一些实施例中,本图像传感器还包括以下至少一项或多项:一个或多个与像素选择电路相伴的模数转换器,用于将该选定像素的强度转换为数字信号;该快速导出架构中的一个或多个重布线电路,用于对该选定像素进行重布线;与该一个或多个并行i/o相伴中的一个或多个存储缓冲器,用于在通过该一个或多个并行i/o输出之前存储该选定像素;以及一个或多个列处理电路,包括该像素选择电路、该一个或多个并行i/o和该快速导出架构,其中,一列中的一行或多行或所有行的像素共用一个列处理电路。

17、在一些实施例中,多个并行i/o还包括以下至少一项:一个并行i/o,用于导出一列或多列中数据,其中,在该选定像素经过了重新布线的情况下,通过该多个并行i/o中的一个i/o通道输出一个重布线单元中的该选定像素的强度,以及选定像素的位置是在一个并行i/o中列的编码;以及输出全局标志,该全局标志用于指示以下一项或多项:待通过该并行i/o导出的选定像素的数量,是否存在待导出的选定像素,以及数据导出的工作模式。

18、在一些实施例中,该像素选择电路用于根据以下规则中的至少一个规则选择像素:像素的强度大于第一阈值;或者像素与其相邻列中的像素之间的强度差大于第二阈值。

19、在一些实施例中,一个或多个重布线电路还包括:将行中相邻的若干选定像素的数据分割为一个或多个重布线单元;以及将所述若干选定像素的分割数据平均分配到一个或多个并行i/o以进行数据导出。

20、在一些实施例中,一个或多个模数转换器还用于:对该一个或多个像素中的每个像素:生成与该像素相关的标志;如果该像素被选定,将该标志设置为激活,以及如果该像素未被选定,将该标志设置为非激活;以及在与该像素相关的该标志为激活的情况下,将该像素的强度转换为数字信号。

21、在一些实施例中,在该一个或多个adc将该选定像素的强度转换为数字信号的情况下,该图像传感器还包括以下至少一项或多项:一个或多个并行adc,用于对对应于一个并行i/o的数据同时进行ad转换;一个并行adc,用于在每个周期输出一位数字数据,直到该数据完全转换为数字数据,以及多个并行adc,用于在每个周期同时输出多位数字数据,直到该数据完全转换为数字数据;以及一个或多个逐次逼近型模数转换器,其中,该逐次逼近型模数转换器的比较器用于同时进行用于亮像素选择的比较和ad转换。

22、在一些实施例中,ad转换和数据通信采用交错时序:当该模数转换器在转换数据时,下一行的数据开始被读出。

23、在一些实施例中,在该一个或多个存储缓冲器存储该数据的情况下,该存储缓冲器的数量小于对应于同一个i/o的像素的数量;通过基于进位超前加法器逻辑的控制器将该数据移入和移出该存储缓冲器;在该存储缓冲器为fifo存储器的情况下,数据被逐位移入和移出;在该存储缓冲器为fifo存储器的情况下,一批多位数据被并行移入和移出;以及当下一个强度数据转换为数字数据时,清空该存储缓冲器中的数据。

24、在一些实施例中,通过时钟信号控制操作时序;以及增设缓冲器以消除信号延迟,其中该缓冲器具有分层结构。

25、本发明的又一个方面还提出了一种3d形状重建方法,包括:根据图像传感器中选定像素的位置和/或选定像素的位置和强度,计算利用特征光扫描的对象的几何形状;其中,根据上述任一个实施例所述的方法获取图像传感器中选定像素的位置和/或选定像素的位置和强度。

26、在一些实施例中,根据图像传感器中选定像素的位置和/或选定像素的位置和强度,计算利用特征光扫描的对象的几何形状包括:由选定像素和相机中心形成像素射线;将不同图像传感器中的像素射线相交于一点,或者将像素射线与入射光的平面相交;以及根据图像传感器的标定信息,计算该点的几何位置。

27、本发明的又一个方面还提出了一种成像系统,包括:包括一个或多个像素的一个或多个图像传感器;一个或多个光源;以及与该一个或多个图像传感器相配的一个或多个计算单元;其中,该一个或多个图像传感器为上述任一个实施例所述的图像传感器,以及该一个或多个计算单元用于执行上述任一个实施例所述的方法。

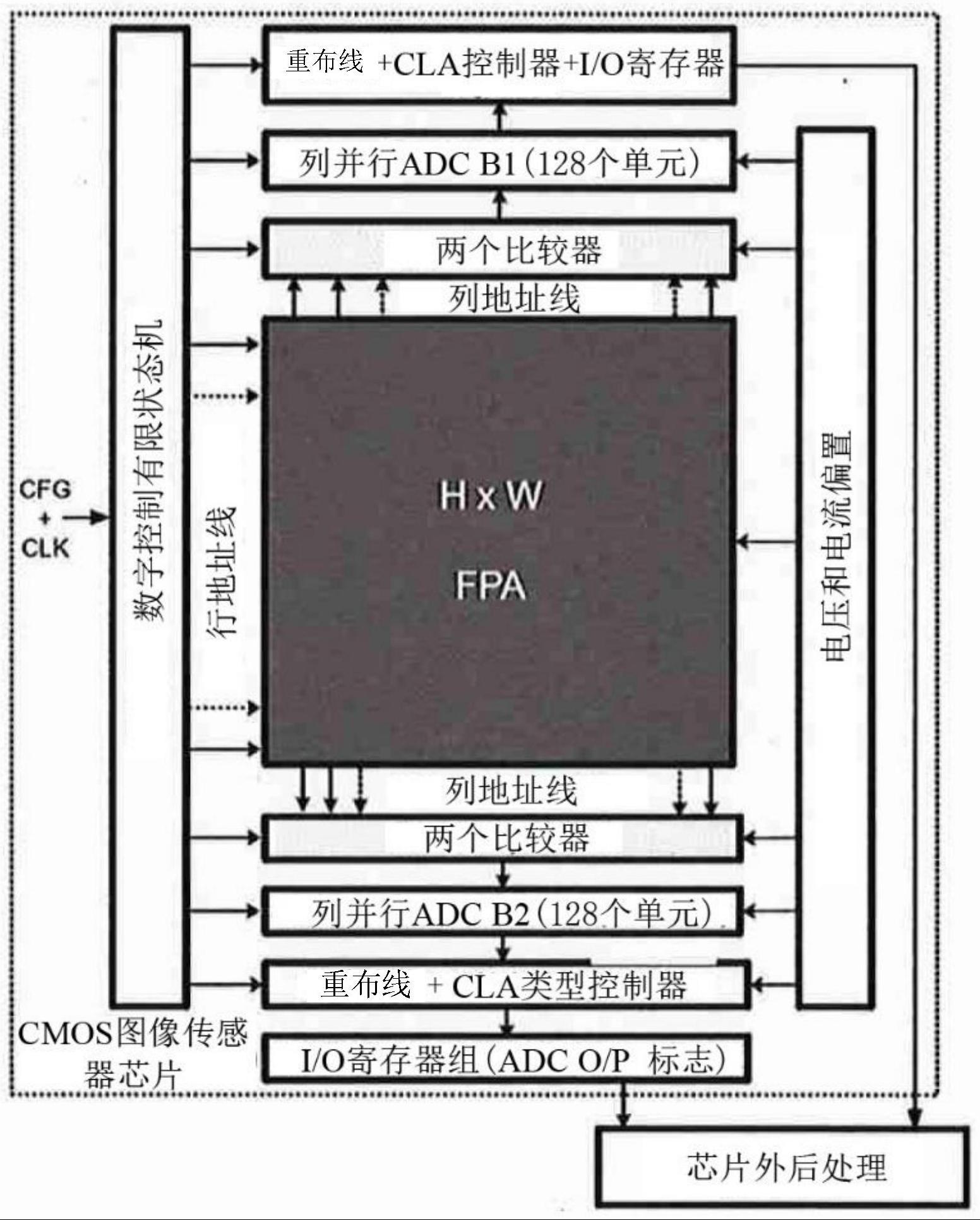

28、本发明提出了一种新颖的cmos传感器,其可检测“亮”像素并仅输出选定像素的光强度和位置。检测功能是通过应用阈值准则方法实现的。本发明提出了一种新颖的cmos结架构。两组列处理电路共享cmos焦平面阵列(fpa),分别用于选择、处理和导出fpa上半部和下半部的数据。本发明提出了一些方案,以实现高速、低能耗以及高效率的cmos;其中,多个i/o的部署可减少传输行中数据的压力;重布线方案是将“选定”像素平均分配给多个i/o;移入移出寄存器可最大化存储效率;以及交错时序方案可降低adc速度的要求。

技术实现思路

- 还没有人留言评论。精彩留言会获得点赞!