一种基于Zynq架构的GPON硬件系统的制作方法

一种基于zynq架构的gpon硬件系统

技术领域

1.本发明属于高速数字光通信技术领域,具体涉及一种基于zynq架构的gpon硬件系统。

背景技术:

2.随着5g电信网络、高速数据业务和4k高清视频传输等大量高速数字通讯与数据采集处理技术的不断发展与普及应用,ftt

×

逐渐成为民、商用的主流技接入网实现方式。而gpon作为网络中以太网交换的替代优化方案,通过取消使用无源光设备的接入和分布以太网交换机,将传统的三层以太网设计替换简化为两层光纤网络。以提供高速率、高带宽、长距离、高可靠性qos、高安全性的gpon(千兆无源光网络)接入网系统为主要特点,已成为目前最主要的光通信系统。

3.现有技术的gpon硬件系统设备,其技术实现方式主要采用进口生产厂家如microsemi的gpon olt和gpon onu专用集成芯片,实现电信级大批量民商用低成本接入网应用;另外,某些工控领域采用成本高昂且不易配置管理、维护的fpga+cpu架构,通过fpga来实现高速数据处理与传输,通过cpu实现数据协议转换、业务配置管理等,需要分别对两片芯片进行分别配置与升级。传统的gpon系统应用环境大多在常温网络机房或办公室,网络拓扑复杂,可靠性、安全性不高。如公开号为cn112055270a的中国专利公开了一种支持dpog技术的gpon系统、设备接入方法及olt,支持以有线电缆数据服务接口规范协议为基础的千兆位以太网无源光网络技术的千兆位以太网无源光网络(gpon)系统、设备接入方法及光线路终端,基于gpon系统简单地实现了对千兆位以太网无源光网络技术的支持,但其使用传统的数据处理芯片进行处理,无法满足当前的应用需求。此外,军事国防、航空航天等特种应用领域,对高速率、小型化、高可靠、全国产化,以及灵活组网,易于管理、维护,小型化、可靠性、安全性等具有更高的要求。

技术实现要素:

4.为解决上述技术问题,本发明提供了一种基于zynq架构的gpon硬件系统,适用于由国产化zynq soc(片上系统)芯片和特种严苛环境olt(光线路终端)、onu(光网络单元)光模块等组成的p2p(点到点)或p2mp(点到多点)多种灵活配置网络拓扑的高速数字光通信gpon系统。

5.本发明通过以下技术方案得以实现。

6.本发明提供的一种基于zynq架构的gpon硬件系统,包括zynq构架soc芯片、光线路终端光模块以及光网络单元光模块,所述zynq构架soc芯片包括处理系统与可编程逻辑部分,所述处理系统与可编程逻辑部分通过axi-lite协议进行通信;所述处理系统包括由qspi flash、emmc存储器、处理系统ddr3存储器组成的存储器模块和远程升级模块;可编程逻辑部分包括高速gtx串行数据收发器与低速hr并行数据收发器,所述高速gtx串行数据收发器连接有一组独立的光线路终端光模块以及光网络单元光模块;另有一组光线路终端光

模块以及光网络单元光模块分别连接至一个串并转换芯片后与所述低速hr并行数据收发器连接,所述可编程逻辑部分还包括可编程逻辑部分ddr3存储器和pcie 2.0

×

4高速接口。

7.进一步的,所述远程升级模块包括千兆网口与rs232串口。

8.进一步的,所述zynq构架soc芯片设有jtag调试口。

9.进一步的,所述存储模块的qspi flash为512mbit qspi flash。

10.进一步的,所述处理系统ddr3存储器由两片256m

×

16bit ddr3sdram存储器组成。

11.进一步的,所述可编程逻辑部分ddr3存储器为由四片256m

×

16bitddr3存储器组成。

12.进一步的,所述光线路终端光模块连接有光功分器,通过光功分器可连接至其他gpon系统的光网络单元光模块。

13.进一步的,还包括外部的远程升级、配置管理、日志维护控制平台,所述zynq构架soc芯片上处理系统的远程升级模块通过千兆网口与rs232串口连接至远程升级、配置管理、日志维护控制平台。

14.进一步的,还包括主机服务器,所述zynq构架soc芯片的可编程部分通过pcie 2.0

×

4高速接口。

15.进一步的,所述光功分器为1:16光功分器或1:32光功分器中的一种。

16.本发明的有益效果在于:通过本发明的实施,提供了一种基于zynq架构soc芯片和olt(光线路终端)光模块、onu(光网络单元)光模块等组成的p2p(点到点)或p2mp(点到多点)的灵活、可扩展、易维护网络拓扑的gpon硬件系统,系统各节点数量与拓扑可进行灵活设置,且各节点均可通过基于zynq架构的soc开发平台进行各节点的远程管理、配置与维护,通过其搭建的硬件系统具有系统简洁,成本可控,管理配置、升级维护简单,安全可靠性高,无后门等优势。

附图说明

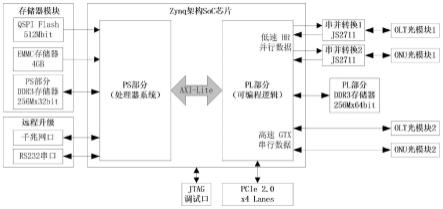

17.图1是本发明的系统实现框图;

18.图2是本发明的远程升级-千兆以太网口原理图;

19.图3是本发明的远程升级-rs232串口原理图;

20.图4是本发明的olt(光线路终端)光模块与onu(光网络单元)光模块原理图;

21.图5是本发明的串并转接js2711原理图;

22.图6是本发明的pcie 2.0

×

4lanes原理图;

23.图7是本发明的基于zynq架构的soc高速gtx bank;

24.图8是本发明的ps与pl(可编程逻辑)部分通讯axi-lite总线框图;

25.图9是本发明的基于zynq架构的gpon硬件系统网络拓扑组成框图。

具体实施方式

26.下面进一步描述本发明的技术方案,但要求保护的范围并不局限于所述。

27.如图1所示,一种基于zynq架构的gpon硬件系统,包括zynq构架soc芯片、光线路终端光模块以及光网络单元光模块,zynq构架soc芯片分为ps(处理系统)部分和pl(可编程逻辑)部分。zynq构架soc芯片ps(处理系统)部分,主要包括系统启动boot操作系统镜像文件

加载的第一启动存储器qspi flash和第二启动存储器emmc,此外还包括用户数据缓存的ddr3存储器;以及远程升级、系统管理的千兆以太网口、本地调试的rs232串口。zynq构架soc开发系统pl(可编程逻辑)部分,主要包括通过高速gtx收发器实现的2.5gbps特种严苛环境适用的olt收发光模块和onu(光网络单元)光模块;以及通过低速hr宽电压范围bank的16位并行接口到高速serdes串并转换接口芯片js2711串行接口的2.5gbps特种严苛环境适用的olt收发光模块和onu收发光模块。的2.5gbps特种严苛环境适用的olt收发光模块和onu收发光模块,组成了灵活的gpon通讯系统。可以实现本级p2p(点对点)通信,或p2mp(多级点对多点)的发射端2.5gbps速率的连续模式和接收端的2.5gbps速率的突发模式通信。两个olt(光线路终端)光模块与两个onu(光网络单元)光模块提供的i2c总线管理接口,连接到了zynq构架soc芯片ps(处理系统)部分的i2c0控制器。可实现通过系统管理与日志功能,实现两个olt和两个onu收发光模块的发射使能/禁止、接收光信号检查、发射端突发模块使用/禁止等光纤通讯链路管理与检测功能。zynq构架soc芯片pl(可编程逻辑)部分,还包括通过高速gtx收发器实现的pcie 2.0

×

4lanes高速接口,和通过hp高性能bank实现的满足pcie 5.0gbps

×

4的高速率、高带宽的实时数据缓存处理的pl(可编程逻辑)部分ddr3存储器。的zynq构架soc芯片的pl(可编程逻辑)部分,实现光纤网络gpon系统的高速串行数据收发、转换处理与协议转发;的zynq构架soc芯片的ps(处理系统)部分,实现gpon系统的用户管理、远程升级、系统日志记录等工作。的zynq构架soc开发系统ps(处理系统)部分和pl(可编程逻辑)部分,通过zynq soc芯片内部处理器间的axi-lite高速通讯总线,进行ps(处理系统)部分与pl(可编程逻辑)部分的信息交互、协议转发与数据通讯。两组olt和两个onu收发光模块,分别提供了通过gtx bank高速串行数据接口直连olt(光线路终端)光模块1和onu(光网络单元)光模块1;以及通过hrbank低速并行数据接口,经串并转换芯片后,连接olt(光线路终端)光模块2和onu(光网络单元)光模块2,两种光电转换接口。可以使得不管是高端系列芯片才具有的高速serdes接口,或是低端系列芯片仅具有hr低速接口,均可以组成灵活多样、易扩展、易管理的p2p(点对点),或p2mp(多级点对多点)的单级或多级gpon硬件系统。

28.参考图1,一种基于zynq架构的gpon硬件系统,主要用全国产化zynq架构soc芯片,以及两组适用于特种严苛环境olt(光线路终端)光模块1和2、onu(光网络单元)光模块1和2组成的具有系统管理、远程升级、数据处理、协议转发的支持多种络拓扑扩展的国产化特种gpon硬件系统。基于zynq架构soc芯片,可以选用复旦微电子的fmql系列fmql45t900等不同型号产品。其内部包含了两个部分:ps(处理系统)部分和pl(可编程逻辑)部分。这两部分可以单独使用,也可以联合起来用,而且实际上供电电路也被设计成可独立给每个部分供电,这样ps(处理系统)部分或pl(可编程逻辑)部分不被使用的话就可以被断电。

29.ps(处理系统)部分包括了四核高性能处理器,最高工作主频可达1ghz,一级缓存包括32kb指令缓存和32kb数据缓存,二级缓存容量256kb,存上存储器容量256kb,外部ddr sdram存储器接口ddr3、ddr3l、lpddr2,外部sram静态存储器接口支持2

×

qspi、nand、norflash,通用外设包括2

×

uart、2

×

can2.0、2

×

i2c,2

×

spi、2

×

64b gpio,高速通信外设包括2

×

usb、2

×

tri-mode千兆以太网、2

×

sd/sdio,安全防护措施包括:专用安全处理器、专用安全算法硬核rsa、aes、sha-256、sm4用于验签和解密,支持安全启动。

30.pl(可编程逻辑)部分包括349760个逻辑单元(logic cells)、218600个查找表

(luts)、437200个触发器(flip-flops)、545个块存储器bram(36kb blocks)、900个dsp单元,以及150个hpio、212个hrio、

×

16lanes gtx高速收发器,最大支持pcie gen2

×

8硬核接口。

31.ps(处理系统)部分的存储器模块设置了512mbit qspi flash用于zynq架构soc开发平台的第一启动配置程序加载存储器,而emmc存储器作为可选的配合第一启动存储器使用的启动后加载boot分区,用于加载操作系统镜像文件系统的4gb大容量存储器;而ps(处理系统)部分ddr3存储器设计了两片外部256m

×

16bit ddr3sdram存储器,用于ps(处理系统)部分操作系统读写数据缓存与运行程序加载。qspi flash存储器、emmc存储器与ps(处理系统)部分ddr3存储器构成了zynq架构soc芯片外部连接的存储器模块。ps(处理系统)部分还设计了用于gpon系统远程升级、系统管理与配置维护的千兆以太网口和支持或远程快速日志查询、系统调试的rs232串口。图2远程升级-千兆以太网原理图和图3远程升级-rs232串口原理图组成了图1所示的远程升级。

32.如图1所示,pl(可编程逻辑)部分包括通过高速gtx收发器直连而实现的2.5gbps特种严苛环境适用的olt1光模块1和onu(光网络单元)光模块1;以及通过低速hr宽电压范围bank的16位并行接口到高速serdes串并转换1、2接口芯片js2711串行接口的2.5gbps特种严苛环境适用的olt(光线路终端)光模块2和onu(光网络单元)光模块2。

33.所述的pl(可编程逻辑)部分的olt1光模块1、2和onu(光网络单元)光模块1、2,如图4olt(光线路终端)光模块与onu(光网络单元)光模块原理图所示,均选用全国产化设计支持2.5gbps特种严苛环境耐高温、抗震动要求的olt(光线路终端)光模块和onu(光网络单元)光模块,olt(光线路终端)光模块通过1:16或1:32光功分器,组成了灵活易拓展多种网络拓扑架构的gpon通讯系统。参考图9所示,可以实现本级p2p(点对点)通信,或p2mp(多级点对多点)的发射端2.5gbps速率的连续模式和接收端的2.5gbps速率的突发模式千兆pon网络通信。此外,所述的olt(光线路终端)光模块和onu(光网络单元)光模块外形大小、结构尺寸、接口定义完全一致,仅内部电路、收、发光波长范围、软件通讯协议和产品型号不同。可通过仅更新bom(物料清单)型号,而实现如四路onu(光网络单元)光模块、四路olt(光线路终端)光模块等等不同组合互换的硬件配置和软件定义重配置,从而扩展多元化、简易化、低成本、多功能、开发周期短的不同网络拓扑架构的gpon通讯系统。

34.所述的pl(可编程逻辑)部分的串并转换1和串并转换2高速接口芯片,参考图5串并转接js2711原理图所示,其主要聚焦于某些低成本可靠设计要求的不具备高速gtx收发器接口的zynq架构soc开发平台gpon系统,仍可以实现简化后的低成本、多功能、易扩展网络系统。

35.所述的两个olt和两个onu收发光模块提供的i2c总线管理接口,通过连接到了zynq构架soc开发平台ps(处理系统)部分的通用外设i2c0控制器。可实现通过系统管理与日志功能,实现两个olt和两个onu收发光模块的发射使能/禁止、接收光信号检查、发射端突发模块使用/禁止等光纤通讯链路管理与检测功能。

36.所述zynq构架soc开发平台pl(可编程逻辑)部分,还包括通过高速gtx收发器实现的pcie 2.0

×

4lanes高速接口,以及通过hp高性能bank实现的满足pcie 5.0gt/s

×

4的高速率、高带宽的实时数据缓存处理的pl(可编程逻辑)部分ddr3存储器。参考图6pcie 2.0

×

4lanes原理图所示,四通道高速seders串行数据连接至zyqn soc的高速gtx收发器,参考图

7,基于zynq架构的soc高速gtx bank所示。参考图9基于zynq架构的gpon硬件系统网络拓扑组成框图所示,可实现多拓扑结构gpon系统的多通道数据双向传输至主机服务器进行分析处理,或通过主机服务器同步分步顶控制信息或数据包至gpon系统各节点的zynq soc芯片进行网络系统各结点的系统配置或数据传输。所述的pl(可编程逻辑)部分ddr3存储器如图1所示,设计为四片256m

×

16bitddr3存储器,以时钟频率为400mhz计算,则数据ddr带宽为400mhz

×2×

16bit

×

4=51200mbit/8=6400mb/s=6.4gb/s,而pcie 2.0

×

4lanes最大数据吞吐量为5gt/s

×

8/10bit

×

4=2gb/s,四个olt与onu(光网络单元)光模块最大数据带宽为2.5gbps

×

8/10

×

4=250mb/s

×

4=1gb/s,系统最大数据吞吐量为2gb/s+1gb/s,共计3gb/s数据带宽,再加上信道预估最大20%损耗,共计3.75gb/s,设计pl(可编程逻辑)部分的四片ddr3存储器6.4gb/s带宽,可以满足系统数据实时存储处理带宽要求,而不需要增加pl(可编程逻辑)部分额外的数据处理。

37.所述的zynq构架soc开发平台ps(处理系统)部分和pl(可编程逻辑)部分,通过zynq soc芯片内部处理器间的axi-lite高速通讯总线,参考图8ps与pl(可编程逻辑)部分通讯axi-lite总线框图所示,使用2

×

axi 64-bit master和slave模式,以及4

×

axi 64-bit memory、16个interrupts中断信号,进行ps(处理系统)部分与pl(可编程逻辑)部分的信息交互、协议转发与数据通讯,以及通过pl(可编程逻辑)部分pcie 2.0

×

4lanes接口,实现主机服务器与远程升级、配置管理、日志维护控制平台的通讯。

38.以上的具体实施个例对本发明进行阐述,只是用于帮助理解本发明,并不用以限制本发明。对于本发明所属技术领域的技术人员,依据本发明的思想,还可以做出若干简单推演、变形或替换。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1